使用束基板通孔的3D电感器设计的制作方法

本公开的各方面涉及半导体器件,并且更具体地涉及使用束基板通孔的3d螺线管电感器设计。

背景技术:

无线通信设备结合了射频(rf)模块,该rf模块便于通信并且以用户期望为特征。随着无线系统变得更加普遍并且包括更多能力,芯片的生产已经变得更加复杂。第五代(5g)新空口(nr)无线通信设备结合了最新一代电子管芯,该电子管芯将许多特征和设备封装到较小且具有越来越小的互连的模块中。随着这些模块的密度增加,电感器对于性能而言是重要的并且可能占据管芯上的相当大的面积。移动射频(rf)芯片(诸如移动rf收发器)的设计挑战包括模拟/rf性能考虑,包括失配、噪声和其他性能考虑。这些移动rf收发器的设计包括使用无源器件(诸如电感器)来抑制谐振和/或执行滤波、旁路和耦合。这些电感器被集成到诸如应用处理器和图形处理器之类的高功率片上系统设备中。在实践中,移动rf收发器的无源器件可涉及高性能电感器部件。例如,模拟集成电路使用各种类型的无源器件,诸如集成电感器。集成电感器的使用可消耗层压或封装基板上的显著面积,且还可导致较高插入损耗和较低质量(q)因子。期望改进集成电感器的性能以提供较高的q因子。集成电感器可用于5g nr rf模块中的毫米波(mmw)滤波器。

背景技术

技术实现思路

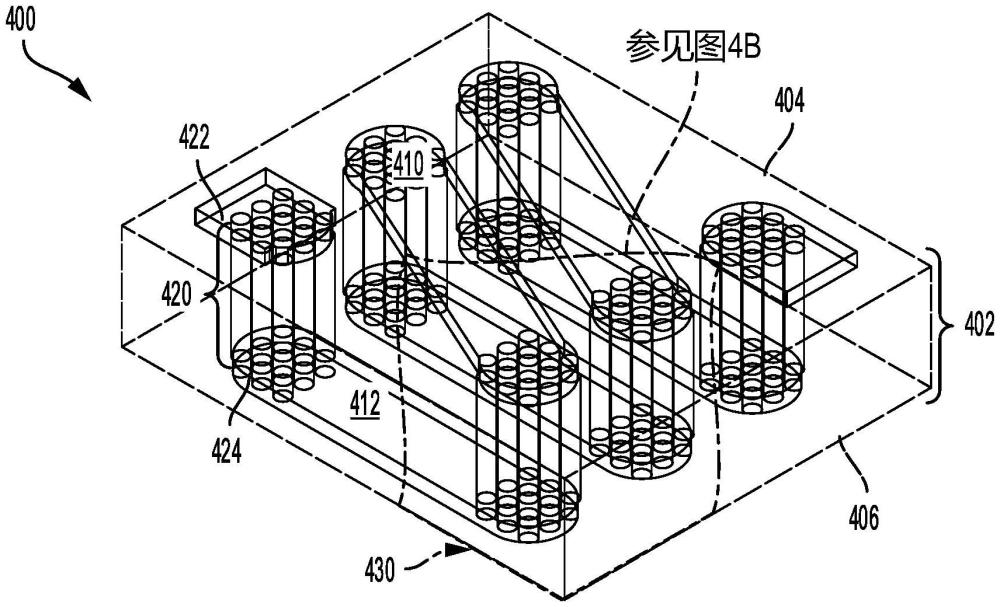

1、描述了一种三维(3d)电感器。该3d电感器包括在基板的第一区域内的第一多个微贯穿基板通孔(tsv)。该3d电感器还包括在基板的第一表面上的第一迹线,该第一迹线耦合到第一多个微tsv的第一端。该3d电感器还包括在基板的与第一表面相对的第二表面上的第二迹线,该第二迹线耦合到第一多个微tsv的与第一端相对的第二端。

2、描述了一种用于制造三维(3d)电感器的方法。该方法包括在基板的第一区域内形成第一多个微贯穿基板通孔(tsv)。该方法还包括在基板的第一表面上沉积第一迹线以接触第一多个微tsv的第一端。该方法还包括在基板的与第一表面相对的第二表面上沉积第二迹线,以接触与第一多个微tsv的第一端相对的第二端。

3、这已较宽泛地勾勒出本公开的特征和技术优势以力图使下面的详细描述可被更好地理解。本公开的附加特征和优点将在下文描述。本领域技术人员应当理解,本公开可容易地被用作修改或设计用于实施与本公开相同的目的的其他结构的基础。本领域技术人员还应认识到,这样的等效构造并不脱离所附权利要求中所阐述的本公开的教导。被认为是本公开的特性的新颖特征在其组织和操作方法两方面连同进一步的目的和优点在结合附图来考虑以下描述时将被更好地理解。然而,要清楚理解的是,提供每一幅附图均仅用于解说和描述目的,且无意作为对本公开的限定的定义。

技术特征:

1.一种三维(3d)电感器,包括:

2.根据权利要求1所述的3d电感器,其中所述第一多个微tsv中的两个微tsv之间的空间小于所述基板的对应于宏tsv的形状因子的所述第一区域与所述基板的对应于所述宏tsv的所述形状因子的第二区域之间的空间。

3.根据权利要求1所述的3d电感器,其中所述第一迹线包括第一多条带状线迹线。

4.根据权利要求1所述的3d电感器,其中所述第二迹线包括第二多条带状线迹线。

5.根据权利要求1所述的3d电感器,其中所述第一迹线包括第一多条带状线迹线并且所述第二迹线包括第二多条带状线迹线。

6.根据权利要求1所述的3d电感器,其中所述第一迹线包括多条带状线迹线并且所述第二迹线包括单条带状线迹线。

7.根据权利要求1所述的3d电感器,其中所述第一迹线包括单条带状线迹线并且所述第二迹线包括多条带状线迹线。

8.根据权利要求1所述的3d电感器,其中所述3d电感器被集成在集成无源器件(ipd)中。

9.根据权利要求8所述的3d电感器,其中所述ipd被集成在ipd滤波器管芯中。

10.根据权利要求9所述的3d电感器,其中所述ipd滤波器管芯被集成在射频前端(rffe)模块中。

11.一种用于制造三维(3d)电感器的方法,所述方法包括:

12.根据权利要求11所述的方法,其中形成所述第一多个微tsv包括均匀地间隔所述第一多个微tsv,其中所述第一多个微tsv中的两个微tsv之间的空间小于所述基板的对应于宏tsv的形状因子的所述第一区域与所述基板的对应于所述宏tsv的所述形状因子的第二区域之间的空间。

13.根据权利要求11所述的方法,其中沉积所述第一迹线包括在所述基板的所述第一表面上沉积第一多条带状线迹线。

14.根据权利要求11所述的方法,其中沉积所述第二迹线包括在所述基板的所述第二表面上沉积第二多条带状线迹线。

15.根据权利要求11所述的方法,

16.根据权利要求11所述的方法,

17.根据权利要求11所述的方法,

18.根据权利要求11所述的方法,还包括将所述3d电感器集成在集成无源器件(ipd)中。

19.根据权利要求18所述的方法,还包括将所述ipd集成在ipd滤波器管芯中。

20.根据权利要求19所述的方法,还包括将所述ipd滤波器管芯集成在射频前端(rffe)模块中。

技术总结

描述了一种三维(3D)电感器。该3D电感器包括在基板的第一区域内的第一多个微贯穿基板通孔(TSV)。该3D电感器还包括在该基板的第一表面上的第一迹线,该第一迹线耦合到该第一多个微TSV的第一端。该3D电感器还包括在该基板的与该第一表面相对的第二表面上的第二迹线,该第二迹线耦合到该第一多个微TSV的与该第一端相对的第二端。

技术研发人员:金钟海,J-H·兰,R·达塔

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!