布线电路基板的制造方法与流程

本发明涉及布线电路基板的制造方法。

背景技术:

1、以往,公知有一种在支承基板上形成布线图案和虚设图案的印刷电路板的制造方法(例如参照下述专利文献1。)。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2003-273498号公报

技术实现思路

1、发明要解决的问题

2、存在想要在专利文献1所记载那样的印刷电路板形成开口的情况。在该情况下,在专利文献1所记载那样的方法中,由于在形成印刷电路板的区域的外侧形成有虚设图案,因此,难以实现在开口的附近形成的布线图案的厚度的均匀化。

3、本发明提供能够实现在开口的附近形成的导体图案的厚度的均匀化的布线电路基板的制造方法。

4、用于解决问题的方案

5、本发明[1]提供一种布线电路基板的制造方法,其中,该布线电路基板的制造方法包含:第1工序,在该第1工序中,在支承层设定图案形成区域和开口形成区域;第2工序,在该第2工序中,至少在所述图案形成区域内,在所述支承层之上形成绝缘层;第3工序,在该第3工序中,通过电镀在所述图案形成区域内的所述绝缘层之上形成导体图案并且在所述开口形成区域内形成虚设图案;以及第4工序,在该第4工序中,对所述开口形成区域内的所述支承层的至少一部分进行蚀刻。

6、采用这样的方法,在第3工序中,能够与开口形成区域内的虚设图案一起形成图案形成区域内的导体图案。

7、因此,在镀敷液中,能够实现导体图案的周围的金属离子浓度的均匀化。

8、其结果,能够实现在开口的附近形成的导体图案的厚度的均匀化。

9、本发明[2]在上述[1]的布线电路基板的制造方法的基础上,在所述第2工序中,在所述图案形成区域内和所述开口形成区域内形成所述绝缘层,在所述第3工序中,在所述开口形成区域内的所述绝缘层之上形成所述虚设图案。

10、采用这样的方法,在开口形成区域内形成绝缘层,能够利用该绝缘层来支承虚设图案。

11、因此,即使开口形成区域内的全部支承层被蚀刻,也能够利用绝缘层来支承虚设图案。

12、本发明[3]在上述[2]的布线电路基板的制造方法的基础上,在所述第1工序中,在所述支承层进一步设定包含所述图案形成区域和所述开口形成区域的产品区域、以及与所述产品区域连接的框架区域,在所述第4工序中,对所述开口形成区域内的全部所述支承层进行蚀刻而在所述支承层形成开口,对所述产品区域与所述框架区域之间的所述支承层进行蚀刻,从而沿着所述产品区域的形状形成布线电路基板的外形并且沿着所述框架区域的形状形成与所述布线电路基板连接的框架,所述布线电路基板的制造方法还包含第5工序,在该第5工序中,从所述框架切出所述布线电路基板,并且从所述布线电路基板切出所述开口内的所述绝缘层。

13、采用这样的方法,在对开口形成区域内的全部支承层进行蚀刻而在支承层形成开口之后,切出开口内的绝缘层,由此能够简单地去除虚设图案。

14、本发明[4]在上述[1]的布线电路基板的制造方法的基础上,在所述第2工序中,在所述图案形成区域内形成所述绝缘层,不在所述开口形成区域内形成所述绝缘层,在所述第3工序中,在所述开口形成区域内的所述支承层之上形成所述虚设图案。

15、采用这样的方法,能够利用开口形成区域内的支承层来支承虚设图案。

16、本发明[5]在上述[4]的布线电路基板的制造方法的基础上,在所述第4工序中,对所述开口形成区域内的全部所述支承层进行蚀刻。

17、采用这样的方法,通过对开口形成区域内的全部支承层进行蚀刻,能够简单地去除虚设图案。

18、发明的效果

19、根据本发明的布线电路基板的制造方法,即使在开口的附近形成导体图案的情况下,也能够实现导体图案的厚度的均匀化。

技术特征:

1.一种布线电路基板的制造方法,其中,

2.根据权利要求1所述的布线电路基板的制造方法,其中,

3.根据权利要求2所述的布线电路基板的制造方法,其中,

4.根据权利要求1所述的布线电路基板的制造方法,其中,

5.根据权利要求4所述的布线电路基板的制造方法,其中,

技术总结

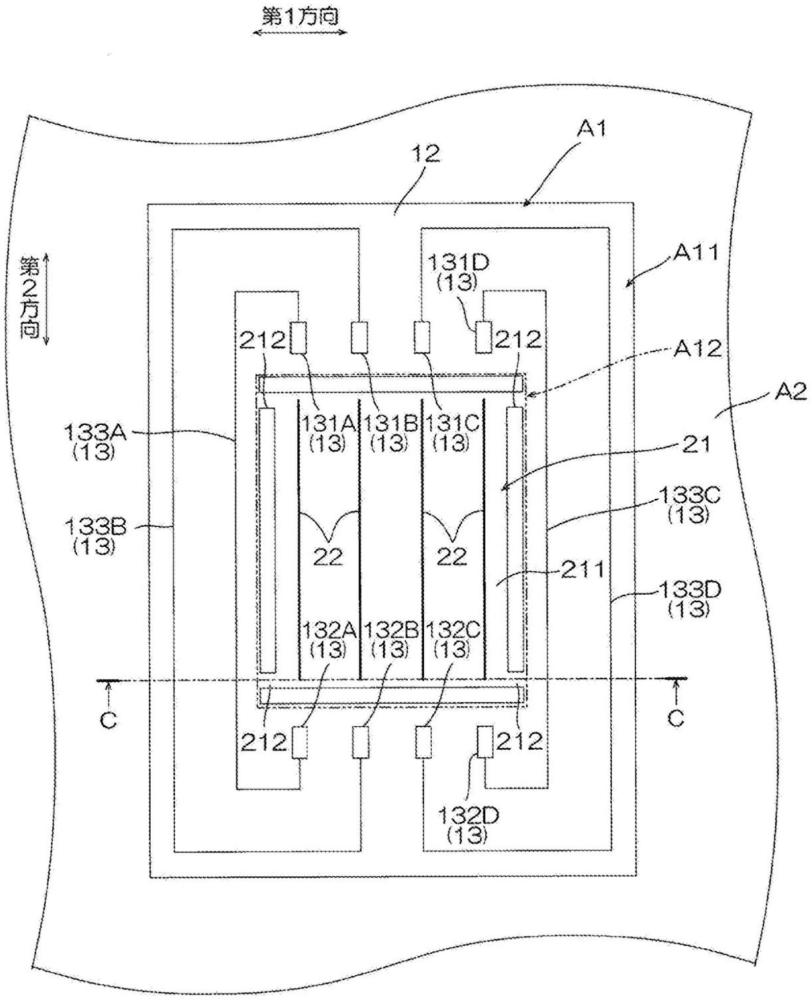

一种布线电路基板(1)的制造方法,其中,该布线电路基板(1)的制造方法包含:第1工序,在该第1工序中,在支承层(11)设定图案形成区域(A11)和开口形成区域(A12);第2工序,在该第2工序中,至少在图案形成区域(A11)内,在支承层(11)之上形成基底绝缘层(12);第3工序,在该第3工序中,通过电镀在图案形成区域(A11)内的基底绝缘层(12)之上形成导体图案(13)并且在开口形成区域(A12)内形成虚设图案(22);以及第4工序,在该第4工序中,对开口形成区域(A12)内的支承层(11)的至少一部分进行蚀刻。

技术研发人员:高仓隼人,柴田直树,福井玲,田中智章

受保护的技术使用者:日东电工株式会社

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!