半导体电路、成像设备和电子设备的制作方法

本公开涉及半导体电路、成像设备和电子设备。

背景技术:

1、偏置电压可能由于来自用于生成用于电流源等的偏置电压的电路的噪声或者从使用偏置电压的另一个电路进入的噪声而波动。为了防止偏置电压的波动,可以提供用于偏置电压的采样和保持的电路。对于偏置电压的采样和保持,需要用于采样和保持的开关。

2、当用于采样和保持的开关从导通状态(on-state)切换到截止状态(off-state)时,偏置电压可能由于电荷注入或时钟馈通而波动。为了解决该问题,可以提供用于消除的开关(参见ptl 1)。

3、[引文列表]

4、[专利文献]

5、[ptl 1]

6、jp 2010-118931a

技术实现思路

1、[技术问题]

2、然而,如果提供用于消除的开关,那么该开关可能充当连接到地的电容并且导致电源噪声在偏置电压的保持期间传播到后级的电路。

3、因此,本公开提供了一种提高对电源噪声的抵抗力的半导体电路、成像设备和电子设备。

4、[问题的解决方案]

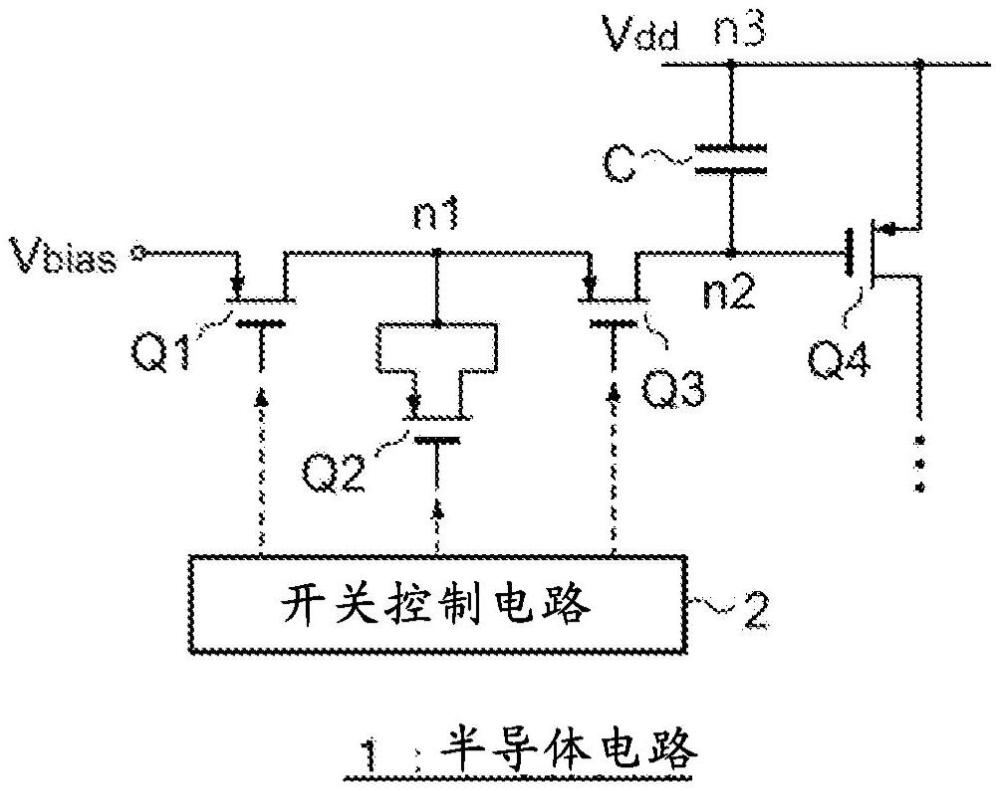

5、为了解决该问题,本公开提供了一种半导体电路,包括:第一晶体管,进行切换以是否将输入信号获取到第一节点中;

6、第二晶体管,其源极和漏极中的至少一个连接到第一节点;以及

7、第三晶体管,进行切换以使得第一节点和第二节点电短路或彼此切断(cut off),

8、其中,在第一晶体管从导通状态到截止状态的转变的定时之后,第二晶体管的状态进行具有与第一晶体管的栅极波形反相的栅极波形的转变,并且

9、在第二晶体管的状态转变的定时之后,第三晶体管进行从导通状态到截止状态的转变。

10、该半导体设备还可以包括消除开关,该消除开关包括第二晶体管并且消除第一节点的电势波动,电势波动是在第一晶体管进行从导通状态到截止状态的转变时由电荷注入和时钟馈通引起的。

11、第一晶体管的漏极可以连接到第一节点,并且输入信号可以被输入到第一晶体管的源极。

12、第一晶体管和第三晶体管可以是pmos(p沟道金属氧化物半导体)晶体管,

13、如果第二晶体管为pmos晶体管,那么第二晶体管可以在第一晶体管从导通状态到截止状态的转变的定时之后进行从截止状态到导通状态的转变,并且第三晶体管可以在第二晶体管从截止状态到导通状态的转变的定时之后进行从导通状态到截止状态的转变,并且

14、如果第二晶体管为nmos(n沟道金属氧化物半导体)晶体管,那么第二晶体管可以在第一晶体管从导通状态到截止状态的转变的定时之后进行从导通状态到截止状态的转变,并且第三晶体管可以在第二晶体管从导通状态到截止状态的转变的定时之后进行从导通状态到截止状态的转变。

15、第一晶体管的漏极可以连接到第二节点,并且输入信号可以被输入到第一晶体管的源极。

16、第一晶体管和第三晶体管可以是nmos(n沟道金属氧化物半导体)晶体管,

17、如果第二晶体管为nmos晶体管,那么第二晶体管可以在第一晶体管从导通状态到截止状态的转变的定时之后进行从截止状态到导通状态的转变,并且第三晶体管可以在第二晶体管从截止状态到导通状态的转变的定时之后进行从导通状态到截止状态的转变,并且

18、如果第二晶体管为pmos晶体管,那么第二晶体管可以在第一晶体管从导通状态到截止状态的转变的定时之后进行从导通状态到截止状态的转变,并且第三晶体管可以在第二晶体管从导通状态到截止状态的转变的定时之后进行从导通状态到截止状态的转变。

19、在第三晶体管进行从导通状态到截止状态的转变之后,第二节点可以被设置在与第二晶体管的栅极电位无关的电位。

20、该半导体电路可以包括其栅极连接到第二节点的第四晶体管;以及

21、连接在第四晶体管的栅极和参考电位节点之间的电容器。

22、电容器可以在第一晶体管从导通状态到截止状态的转变的定时保持与输入信号对应的电荷。

23、电容器可以连接在第二节点和第三节点之间,并且

24、当第三晶体管截止时,第三晶体管的栅极电位可以被设置在第三节点的电位。

25、第四晶体管的源极可以连接到传输像素信号的信号线。

26、半导体电路还可以包括电流源,该电流源包括第四晶体管。

27、该半导体电路还可以进一步包括:差分放大器,该差分放大器包括:与第四晶体管构成差分对的第五晶体管,以及

28、第六晶体管,其控制施加在第四晶体管和第五晶体管的漏极和源极之间的电流。

29、第一晶体管、第二晶体管和第三晶体管可以具有相同的导电类型。

30、第一晶体管和第三晶体管的导电类型与第二晶体管的导电类型可以彼此不同。

31、第一晶体管和第二晶体管的源极可以彼此连接,并且第一晶体管和第二晶体管的漏极可以彼此连接。

32、半导体电路还可以包括开关控制电路,其在第一晶体管从导通状态到截止状态的转变的定时之后使第二晶体管的状态进行转变,并且开关控制电路在第二晶体管的状态转变的定时之后使第三晶体管进行从导通状态到截止状态的转变。

33、本公开提供了一种成像设备,包括:像素阵列部分,被配置为使得具有多个光电转换单元的多个像素以二维方式布置;

34、多条信号线,传输在像素阵列部分中的多个像素中光电转换的像素信号;

35、内部电压生成电路,其生成偏置电压;

36、采样保持电路,以预定周期对偏置电压进行采样和保持;

37、电流源,基于由采样保持电路保持的偏置电压来控制流过多条信号线的电流;以及

38、ad转换器,基于多条信号线上的像素信号与参考信号之间的比较结果来生成与多个像素信号对应的多个数字信号,

39、采样保持电路,包括:

40、第一晶体管,进行切换以是否将偏置电压获取到第一节点中;

41、第二晶体管,其源极和漏极中的至少一个连接到第一节点;以及

42、第三晶体管,进行切换以使得第一节点和第二节点电短路或彼此切断,

43、其中,在第一晶体管从导通状态到截止状态的转变的定时之后,第二晶体管的状态进行具有与第一晶体管的栅极波形反相的栅极波形的转变,并且

44、在第二晶体管的状态转变的定时之后,第三晶体管进行从导通状态到截止状态的转变。

45、电流源可以包括与多条信号线对应的多个第四晶体管,并且

46、多个第四晶体管的漏极可以连接到相应的信号线。

47、提供了一种电子设备,该电子设备包括成像设备;以及

48、信号处理单元,其基于从成像设备输出的多个数字信号来执行信号处理。

技术特征:

1.一种半导体电路,包括:第一晶体管,进行切换以是否将输入信号获取到第一节点中;

2.根据权利要求1所述的半导体设备,还包括消除开关,所述消除开关包括第二晶体管并且消除第一节点的电势波动,所述电势波动是在第一晶体管进行从导通状态到截止状态的转变时由电荷注入和时钟馈通引起的。

3.根据权利要求1所述的半导体电路,其中第一晶体管的漏极连接到第一节点,并且所述输入信号被输入到第一晶体管的源极。

4.根据权利要求3所述的半导体电路,其中第一晶体管和第三晶体管是pmos(p沟道金属氧化物半导体)晶体管,

5.根据权利要求1所述的半导体电路,其中第一晶体管的漏极连接到第二节点,并且所述输入信号被输入到第一晶体管的源极。

6.根据权利要求5所述的半导体电路,其中第一晶体管和第三晶体管是nmos(n沟道金属氧化物半导体)晶体管,

7.根据权利要求1所述的半导体电路,其中在第三晶体管进行从导通状态到截止状态的转变之后,第二节点被设置在与第二晶体管的栅极电位无关的电位。

8.根据权利要求1所述的半导体电路,还包括其栅极连接到第二节点的第四晶体管,以及

9.根据权利要求8所述的半导体电路,其中所述电容器在第一晶体管进行从导通状态到截止状态的转变的定时保持与所述输入信号对应的电荷。

10.根据权利要求8所述的半导体电路,其中所述电容器连接在第二节点与第三节点之间,并且

11.根据权利要求8所述的半导体电路,其中第四晶体管的源极连接到传输像素信号的信号线。

12.根据权利要求8所述的半导体电路,还包括电流源,所述电流源包括第四晶体管。

13.根据权利要求8所述的半导体电路,还包括差分放大器,所述差分放大器包括:

14.根据权利要求1所述的半导体电路,其中第一晶体管、第二晶体管和第三晶体管具有相同的导电类型。

15.根据权利要求1所述的半导体电路,其中第一晶体管和第三晶体管的导电类型与第二晶体管的导电类型彼此不同。

16.根据权利要求15所述的半导体电路,其中第一晶体管和第二晶体管的源极彼此连接,并且第一晶体管和第二晶体管的漏极彼此连接。

17.根据权利要求1所述的半导体电路,还包括开关控制电路,其在第一晶体管从导通状态到截止状态的转变的定时之后使第二晶体管的状态进行转变,并且所述开关控制电路在第二晶体管的状态转变的定时之后使第三晶体管进行从导通状态到截止状态的转变。

18.一种成像设备,包括:像素阵列部分,被配置为使得具有多个光电转换单元的多个像素以二维方式布置;

19.根据权利要求18所述的成像设备,其中所述电流源包括与所述多条信号线对应的多个第四晶体管,并且

20.一种电子设备,包括:根据权利要求18所述的成像设备;以及

技术总结

[问题]提高抗电源噪声能力。[解决方案]一种半导体电路,包括:第一晶体管,进行切换以是否将输入信号获取到第一节点中;第二晶体管,其源极和漏极中的至少一个连接到第一节点;以及第三晶体管,进行切换以使得第一节点和第二节点电短路或彼此切断,其中,在第一晶体管从导通状态到截止状态的转变的定时之后,第二晶体管的状态进行具有与第一晶体管的栅极波形反相的栅极波形的转变,并且在第二晶体管的状态转变的定时之后,第三晶体管进行从导通状态到截止状态的转变。

技术研发人员:村山茂満,清水泰秀

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!