集成组合件及形成集成组合件的方法与流程

本公开涉及集成组合件(例如,集成nand存储器)。形成集成组合件的方法。

背景技术:

1、存储器为电子系统提供数据存储。快闪存储器是一种类型的存储器,且在现代计算机及装置中具有许多用途。例如,现代个人计算机可具有存储在快闪存储器芯片上的bios。作为另一实例,对于计算机及其它装置来说,在固态驱动器中利用快闪存储器来取代常规硬盘驱动器变得越来越普遍。作为又一实例,快闪存储器在无线电子装置中很受欢迎,这是因为其使制造商能够在新通信协议变得标准化时支持所述新通信协议,且提供远程升级所述装置以增强特征的能力。

2、nand可为快闪存储器的基本架构,且可经配置以包括垂直堆叠的存储器单元。

3、在具体地描述nand之前,更一般地描述存储器阵列在集成布置内的关系可能是有帮助的。图1展示现有技术装置1000的框图,其包含存储器阵列1002,存储器阵列1002具有布置成行及列的多个存储器单元1003以及存取线1004(例如,用于传导信号wl0到wlm的字线)及第一数据线1006(例如,用于传导信号bl0到bln的位线)。存取线1004及第一数据线1006可用于将信息传送到存储器单元1003及从存储器单元1003传送信息。行解码器1007及列解码器1008解码地址线1009上的地址信号a0到ax以确定将存取哪些存储器单元1003。感测放大器电路1015操作以确定从存储器单元1003读取的信息的值。i/o电路1017在存储器阵列1002与输入/输出(i/o)线1005之间传送信息的值。i/o线1005上的信号dq0到dqn可表示从存储器单元1003读取或待写入到存储器单元1003中的信息的值。其它装置可通过i/o线1005、地址线1009或控制线1020与装置1000进行通信。存储器控制单元1018用于控制待对存储器单元1003执行的存储器操作,且利用控制线1020上的信号。装置1000可分别接收第一电源线1030及第二电源线1032上的电源电压信号vcc及vss。装置1000包含选择电路1040及输入/输出(i/o)电路1017。选择电路1040可经由i/o电路1017响应于信号csel1到cseln以选择第一数据线1006及第二数据线1013上可表示待从存储器单元1003读取或待编程到存储器单元1003中的信息的值的信号。列解码器1008可基于地址线1009上的a0到ax地址信号来选择性地激活csel1到cseln信号。选择电路1040可选择第一数据线1006及第二数据线1013上的信号以在读取及编程操作期间提供存储器阵列1002与i/o电路1017之间的通信。

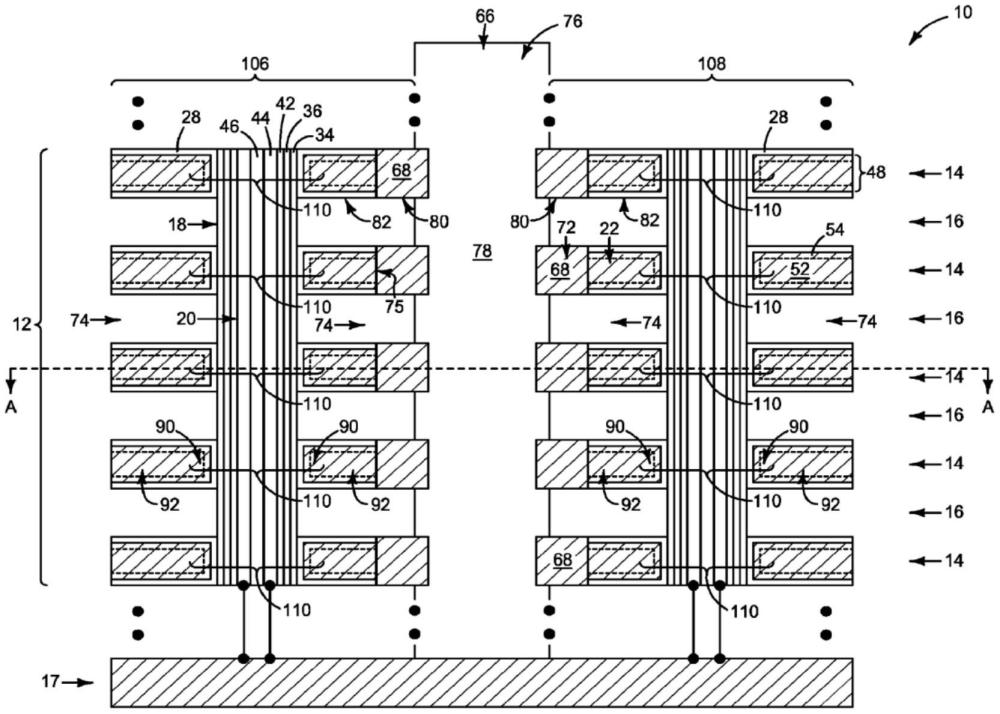

4、图1的存储器阵列1002可为nand存储器阵列,且图2展示可用于图1的存储器阵列1002的三维nand存储器装置200的示意图。装置200包括多个电荷存储装置串。在第一方向(z-z’)上,每一电荷存储装置串可包括例如彼此堆叠的三十二个电荷存储装置,其中每一电荷存储装置对应于例如三十个层面(例如,层面0到层面31)中的一者。相应串的电荷存储装置可共享共同沟道区,例如形成在半导体材料(例如,多晶硅)的相应支柱中的沟道区,电荷存储装置串围绕所述支柱而形成。在第二方向(x-x’)上,例如多个串的十六个第一群组中的每一第一群组可包括例如共享多个(例如,三十二个)存取线(即“全局控制栅极(cg)线”,也被称为字线wl)的八个串。所述存取线中的每一者可耦合层面内的电荷存储装置。当每一电荷存储装置包括能够存储两个信息位的单元时,由同一存取线耦合(且因此对应于同一层面)的电荷存储装置可在逻辑上被分组成例如两个页面,例如p0/p32、p1/p33、p2/p34等。在第三方向(y-y’)上,例如多个串的八个第二群组中的每一第二群组可包括由八个数据线中的对应一者耦合的十六个串。存储器块的大小可包括1,024个页面及总共约16mb(例如,16个wl x 32个层面x 2个位=1,024个页面/块,块大小=1,024个页面x 16kb/页面=16mb)。串、层面、存取线、数据线、第一群组、第二群组及/或页面的数量可大于或小于图2中展示的数量。

5、图3展示图2的3d nand存储器装置200的存储器块300在x-x’方向上的横截面视图,其包含在关于图2所描述的串的十六个第一群组中的一者中的十五个电荷存储装置串。存储器块300的多个串可被分组成多个子集310、320、330(例如,片块列),例如片块列i、片块列j及片块列k,其中每一子集(例如,片块列)包括存储器块300的“部分块”。全局漏极侧选择栅极(sgd)线340可耦合到多个串的sgd。例如,全局sgd线340可经由多个(例如,三个)子sgd驱动器332、334、336中的对应一者耦合到多个(例如,三个)子sgd线342、344、346,其中每一子sgd线对应于相应子集(例如,片块列)。子sgd驱动器332、334、336中的每一者可独立于其它部分块的串的sgd同时耦合或切断对应部分块(例如,片块列)的串的sgd。全局源极侧选择栅极(sgs)线360可耦合到多个串的sgs。例如,全局sgs线360可经由多个子sgs驱动器322、324、326中的对应一者耦合到多个子sgs线362、364、366,其中每一子sgs线对应于相应子集(例如,片块列)。子sgs驱动器322、324、326中的每一者可独立于其它部分块的串的sgs同时耦合或切断对应部分块(例如,片块列)的串的sgs。全局存取线(例如,全局cg线)350可耦合对应于多个串中的每一者的相应层面的电荷存储装置。每一全局cg线(例如,全局cg线350)可经由多个子串驱动器312、314及316中的对应一者耦合到多个子存取线(例如,子cg线)352、354、356。子串驱动器中的每一者可独立于其它部分块及/或其它层面的电荷存储装置同时耦合或切断对应于相应部分块及/或层面的电荷存储装置。对应于相应子集(例如,部分块)及相应层面的电荷存储装置可包括电荷存储装置的“部分层面”(例如,单个“片块”)。对应于相应子集(例如,部分块)的串可耦合到子源极372、374及376(例如,“片块源极”)中的对应一者,其中每一子源极被耦合到相应电源。

6、替代地,参考图4的示意说明来描述nand存储器装置200。

7、存储器阵列200包含字线2021到202n及位线2281到228m。

8、存储器阵列200还包含nand串2061到206m。每一nand串包含电荷存储晶体管2081到208n。所述电荷存储晶体管可使用浮动栅极材料(例如,多晶硅)来存储电荷,或可使用电荷俘获材料(例如举例来说,氮化硅、金属纳米点等)来存储电荷。

9、电荷存储晶体管208位于字线202与串206的交叉点处。电荷存储晶体管208表示用于数据存储的非易失性存储器单元。每一nand串206的电荷存储晶体管208源极到漏极串联地连接在源极选择装置(例如,源极侧选择栅极,sgs)210与漏极选择装置(例如,漏极侧选择栅极,sgd)212之间。每一源极选择装置210位于串206与源极选择线214的交叉点处,而每一漏极选择装置212位于串206与漏极选择线215的交叉点处。选择装置210及212可为任何合适存取装置,且在图4中用框概括地说明。

10、每一源极选择装置210的源极连接到共同源极线216。每一源极选择装置210的漏极连接到对应nand串206的第一电荷存储晶体管208的源极。例如,源极选择装置2101的漏极连接到对应nand串2061的电荷存储晶体管2081的源极。源极选择装置210连接到源极选择线214。

11、每一漏极选择装置212的漏极在漏极触点处连接到位线(即,数字线)228。例如,漏极选择装置2121的漏极连接到位线2281。每一漏极选择装置212的源极连接到对应nand串206的最后一个电荷存储晶体管208的漏极。例如,漏极选择装置2121的源极连接到对应nand串2061的电荷存储晶体管208n的漏极。

12、电荷存储晶体管208包含源极230、漏极232、电荷存储区域234及控制栅极236。电荷存储晶体管208将它们的控制栅极236耦合到字线202。电荷存储晶体管208的列是nand串206内耦合到给定位线228的那些晶体管。电荷存储晶体管208的行是共同耦合到给定字线202的那些晶体管。

13、期望发展出经改进nand架构及用于制造nand架构的经改进方法。

技术实现思路

- 还没有人留言评论。精彩留言会获得点赞!