用于ADC的扰动输入信号的校准方法、装置及系统与流程

本申请涉及模拟数字转换技术,尤其涉及一种用于adc的扰动输入信号的校准方法、装置、系统及计算机可读存储介质。

背景技术:

1、模数转换器(analog-to-digital converter,adc)是用于将模拟形式的连续信号转换为数字形式的一类装置。由于adc制作的工艺及材料特性,使得每个adc自身均具有不同程度的非线性失真,从而使得adc在工作时会生成具有一定非理想误差的数字输出信号。

2、对于高速adc而言,adc的动态特性决定了高速adc工作时的模数转换特性。adc的无杂散动态范围(spurious-free dynamic range,sfdr)是指载波频率(最大信号分量)的均方根值与次最大噪声分量或谐波失真分量的均方根值之比。

3、对于高速adc,若要最大程度地提高sfdr,存在两个基本限制:第一是前端放大器和采样保持电路产生的失真;第二是adc编码器部分的实际传递函数的非线性所导致的失真。因此,提高sfdr的关键是尽可能降低以上两种非线性。

4、要显着降低adc前端引起的固有失真,在adc外部着力是徒劳的。然而,adc编码器传递函数的微分非线性可以通过适当利用扰动注入(即外部噪声,与adc的模拟输入信号相加)来降低。

技术实现思路

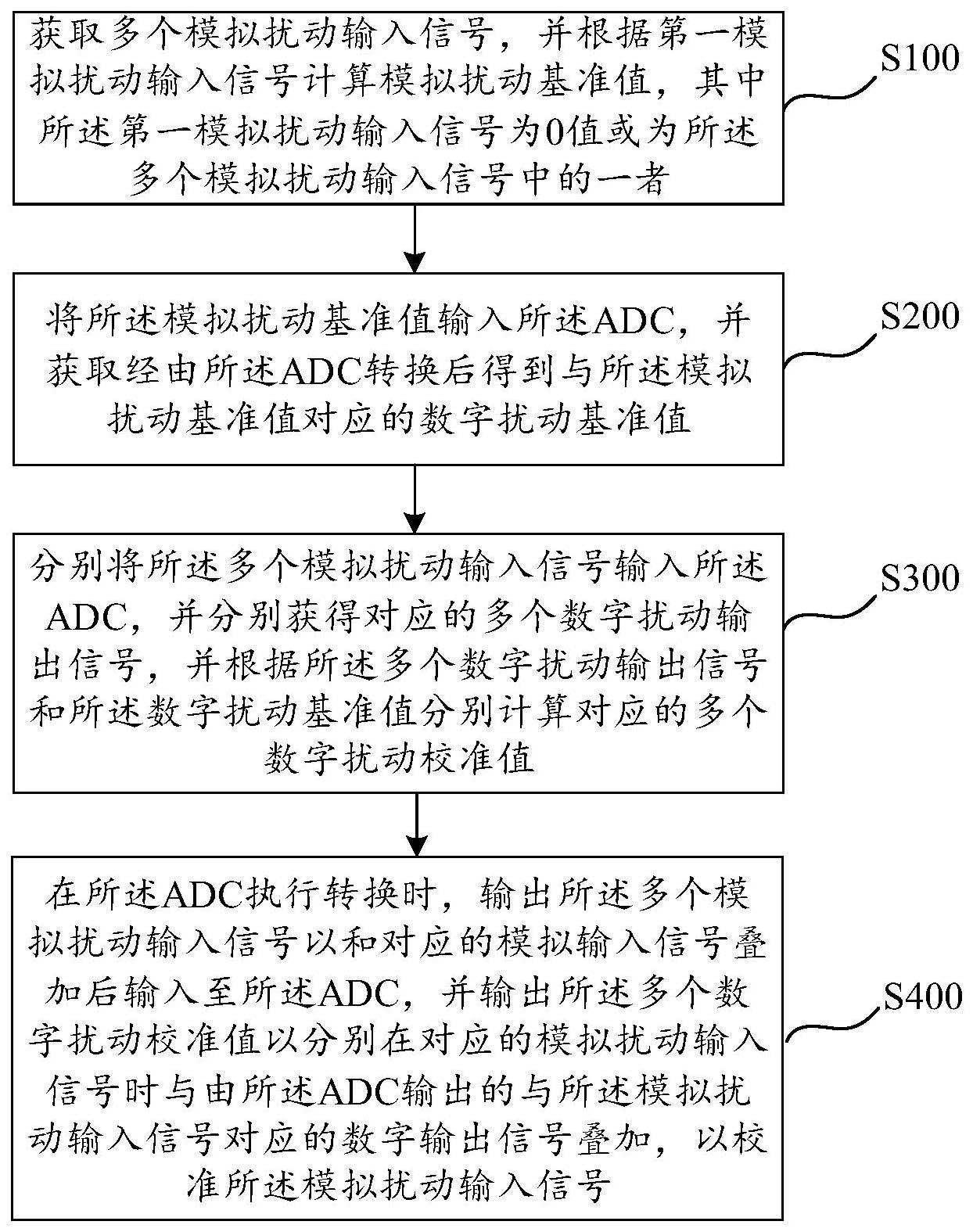

1、本申请各示例性实施例提供了一种用于adc的扰动输入信号的校准方法,包括:获取多个模拟扰动输入信号,并根据第一模拟扰动输入信号计算模拟扰动基准值,其中所述第一模拟扰动输入信号为0值或为所述多个模拟扰动输入信号中的一者;将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的数字扰动基准值;分别将所述多个模拟扰动输入信号输入所述adc,并分别获得对应的多个数字扰动输出信号,并根据所述多个数字扰动输出信号和所述数字扰动基准值分别计算对应的多个数字扰动校准值;以及在所述adc执行转换时,输出所述多个模拟扰动输入信号以和对应的模拟输入信号叠加后输入至所述adc,并输出所述多个数字扰动校准值以分别在对应的模拟扰动输入信号时与由所述adc输出的与所述模拟扰动输入信号对应的数字输出信号叠加,以校准所述模拟扰动输入信号。

2、在一实施例中,当所述第一模拟扰动输入信号为所述多个模拟扰动输入信号中的一者时,所述根据所述第一模拟扰动输入信号计算所述模拟扰动基准值的步骤包括:选取所述多个模拟扰动输入信号的中间值作为所述模拟扰动基准值;和/或所述根据所述多个数字扰动输出信号和所述数字扰动基准值分别计算对应的多个数字扰动校准值的步骤,包括:将所述多个数字扰动输出信号分别减去所述数字扰动基准值以分别获得所述对应的多个数字扰动校准值。

3、在一实施例中,所述将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的数字扰动基准值的步骤,还包括:多次将所述模拟扰动基准值输入所述adc,以获得多个单次数字扰动基准值;以及计算所述多个单次数字扰动基准值的平均值作为所述数字扰动基准值。

4、在一实施例中,所述将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的数字扰动基准值的步骤,还包括:多次将所述模拟扰动基准值输入所述adc,以获得多个单次数字扰动基准值;以及通过低通抽取滤波方法从所述多个单次数字扰动基准值中获取所述数字扰动基准值。

5、在一实施例中,所述输出所述多个数字扰动校准值以分别在所述对应的模拟扰动输入信号时与由所述adc输出的与所述模拟扰动输入信号对应的数字输出信号叠加,以校准所述模拟扰动输入信号的步骤前,还包括:分别对所述多个数字扰动校准值进行延时,其中所述延时的周期与所述adc的转换周期相关。

6、在一实施例中,所述多个模拟扰动输入信号为等差序列。

7、在一实施例中,所述多个模拟扰动输入信号中除所述中间值以外被配置为两两一组,每组模拟扰动输入信号的值相同,符号相反。

8、本申请各示例性实施例提供一种用于adc的扰动输入信号的校准装置,包括:模拟扰动信号获取模块,被配置为获取多个模拟扰动输入信号,并根据、第一模拟扰动输入信号计算模拟扰动基准值,其中所述第一模拟扰动输入信号为0值或为所述多个模拟扰动输入信号中的一者;模数扰动基准值转换模块,被配置为将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的数字扰动基准值;数字扰动校准值计算模块,被配置为分别将所述多个模拟扰动输入信号输入所述adc,并分别获得对应的多个数字扰动输出信号,并根据所述多个数字扰动输出信号和所述数字扰动基准值分别计算对应的多个数字扰动校准值;以及模拟扰动输入信号校准模块,被配置为在所述adc执行转换时,输出所述多个模拟扰动输入信号以和对应的模拟输入信号叠加后输入至所述adc,并输出所述多个数字扰动校准值以分别在对应的模拟扰动输入信号时与由所述adc输出的与所述模拟扰动输入信号对应的数字输出信号叠加,以校准所述模拟扰动输入信号。

9、本申请各示例性实施例提供一种用于adc的扰动输入信号的校准系统,所述校准系统包括至少一个处理器和存储器,所述存储器上存储有程序,所述至少一个处理器在执行所述存储器上的所述程序时,所述处理器执行前述实施例所述方法的步骤。

10、本申请各示例性实施例提供一种计算机可读存储介质,所述计算机可读存储介质上存储有程序,所述程序被执行时执行前述实施例所述方法的步骤。

11、如前文所述,传统技术中,通常通过将模拟扰动输入信号和模拟输入电压信号叠加来增加adc的动态特性。然而,发明人发现,在传统技术中仅仅针对模拟输入电压信号进行数字域的信号校准以提高adc的转换精度,但是模拟扰动输入信号的失真误差却没有进行校准,这会造成对原有信号产生恶化扰动信号性能的影响。

12、本申请各示例性实施例通过设置一种用于adc的扰动输入信号的校准装置来实现一种用于adc的扰动输入信号的校准方法,其根据分别输入至adc的正负输入端的n级的模拟扰动输入信号中的第一模拟扰动输入信号作为模拟扰动基准值,进而计算数字扰动基准值,从而在adc工作时在数字域对转换的数字结果去除扰动输入数字转换值的同时,实时对扰动输入信号的失真误差进行校准。

技术特征:

1.一种用于adc的扰动输入信号的校准方法,其特征在于,包括:

2.根据权利要求1所述的用于adc的扰动输入信号的校准方法,其特征在于,当所述第一模拟扰动输入信号为所述多个模拟扰动输入信号中的一者时,所述根据所述第一模拟扰动输入信号计算所述模拟扰动基准值的步骤包括:

3.根据权利要求2所述的用于adc的扰动输入信号的校准方法,其特征在于,所述将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的所述数字扰动基准值的步骤,还包括:

4.根据权利要求2所述的用于adc的扰动输入信号的校准方法,其特征在于,所述将所述模拟扰动基准值输入所述adc,并获取经由所述adc转换后得到与所述模拟扰动基准值对应的数字扰动基准值的步骤,还包括:

5.根据权利要求2所述的用于adc的扰动输入信号的校准方法,其特征在于,所述输出所述多个数字扰动校准值以分别在所述对应的模拟扰动输入信号时与由所述adc输出的与所述模拟扰动输入信号对应的数字输出信号叠加,以校准所述模拟扰动输入信号的步骤前,还包括:

6.根据权利要求2所述的用于adc的扰动输入信号的校准方法,其特征在于,所述多个模拟扰动输入信号为等差序列。

7.根据权利要求5所述的用于adc的扰动输入信号的校准方法,其特征在于,所述多个模拟扰动输入信号被配置为两两一组,每组模拟扰动输入信号的值相同,符号相反。

8.一种用于adc的扰动输入信号的校准装置,其特征在于,包括:

9.一种用于adc的扰动输入信号的校准系统,其特征在于,所述校准系统包括至少一个处理器和存储器,所述存储器上存储有程序,所述至少一个处理器在执行所述存储器上的所述程序时,所述处理器执行前述权利要求1至7中任一项所述方法的步骤。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有程序,所述程序被执行时执行前述利要求1至7中任一项所述方法的步骤。

技术总结

本申请提供了一种用于ADC的扰动输入信号的校准方法、装置、系统及存储介质,该方法包括:获取多个模拟扰动输入信号,根据第一模拟扰动输入信号计算模拟扰动基准值;将模拟扰动基准值输入ADC,获取数字扰动基准值;分别将多个模拟扰动输入信号输入ADC,并分别获得多个数字扰动输出信号,并根据多个数字扰动输出信号和数字扰动基准值分别计算对应的多个数字扰动校准值;及在ADC执行转换时,输出多个模拟扰动输入信号以和对应的模拟输入信号叠加后输入至ADC,并输出多个数字扰动校准值以分别在对应的模拟扰动输入信号时与由ADC输出的与模拟扰动输入信号对应的数字输出信号叠加,以校准模拟扰动输入信号。

技术研发人员:刘海涛

受保护的技术使用者:南京筠芯科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!