一种仪表着陆系统的实时高精度监控方法与流程

本发明涉及监控,特别是一种仪表着陆系统的实时高精度监控方法。

背景技术:

1、仪表着陆系统是国际应用最为广泛的飞机精密进近和着陆引导系统。它由地面发射的无线电信号在空中形成航向道和下滑道指引,并建立一条由跑道入口指向空中的虚拟航道,为飞行器提供全天时全天候的进近着陆指引,引导飞行器沿正确方向进近跑道并最终实现安全着陆。

2、仪表着陆系统发射信号的幅度、调制度、相位、频率及频差的不稳定都会带来航道和航道结构的偏移、变形、波动及错误,导致飞机无法按正确的航向进行安全着陆,严重影响飞行安全。因此在i/ii类仪表着陆系统中配置了2个监控器,iii类仪表着陆系统中配置了3个监控器,用于实时校准发射信号。监控器的实时性差、校准不及时,精度不够使系统产生的任何虚警、切机、关机,都会使航道及航道结构偏移、变形、波动及错误,因此如何提高仪表着陆系统监控器的处理精度、实时性成为了仪表着陆系统监控技术的重点和难点。传统信号处理中频域变换及多级处理会降低信号处理的实时性,同时低采样率或欠采样、采样信号抽取降速等都会造成信噪比(snr)损失,从而降低处理精度。

3、传统仪表着陆系统的监控器常采用欠采样或低采样率对信号进行低速采样,又对信号进行抽取降速处理,都损失了一定的信噪比,从而降低了处理精度;

4、传统仪表着陆系统的监控器对高速采样信号处理采用正交混频(包括nco模块)+cic滤波+hb半带滤波+抽取+fir滤波方法实现信号处理,这样的方法不仅会使信号处理变得复杂,同时也增加了处理级数,严重影响信号处理实时性;

5、传统仪表着陆系统的监控器信号处理常采用频域处理的方法实现对载波/边带信号幅度的提取,由于频域变换的处理精度受计算点数的影响、处理延迟也受点数的影响,不仅处理实时性变差,也无法同时保证处理的高精度和实时性。

技术实现思路

1、鉴于此,本发明提供一种仪表着陆系统的实时高精度监控方法,通过对信号进行高速采样,并实现了在低速时钟下实现高速采样信号的处理,减少了处理级数、简化了处理流程,从而保证了信号处理的高精度、实时性。

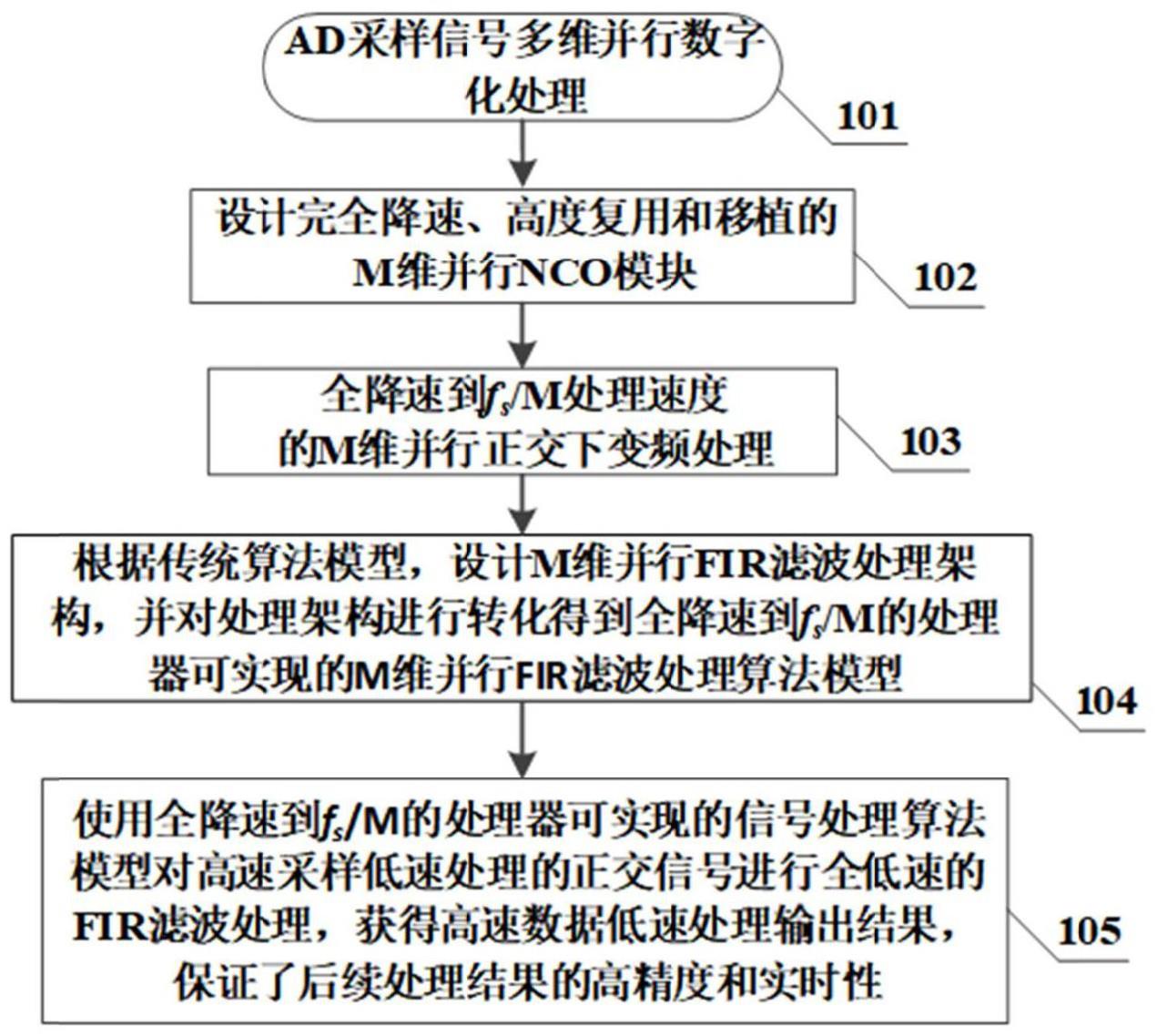

2、本发明公开了一种仪表着陆系统的实时高精度监控方法,其包括以下步骤:

3、步骤1:监控器实时接收仪表着陆系统的发射信号及空间合成信号并对接收的发射信号及空间合成信号进行高速信号采样;在不改变信号采样率fs的情况下,对采样信号进行m维并行化处理,得到降速后的m维并行同步的高速采样信号;其中,m为正整数;

4、步骤2:以直接数字频率合成技术为模型进行算法演算及变换,设计全低速多维并行nco模块,所述全低速多维并行nco模块通过实时调整相位增量输出不同频率的正交本振信号,且输出的正交本振信号为完全同步的m维高采样率低速本振信号;

5、步骤3:对步骤1生成的m维并行高速采样信号和步骤2生成的m维并行高速正交本振信号进行多维并行正交下变频处理,生成高速采样信号的m维并行低速正交信号;

6、步骤4:基于设计的m维并行fir滤波处理架构及算法模型,对步骤3输出的m维并行低速正交信号进行全降速的多维并行fir滤波处理,输出高速采样信号的全低速处理结果。

7、进一步地,所述步骤1包括:

8、步骤11:采样率fs,根据数据率降速比m,采样信号s(n)经过一个m路模m的切换开关后输出m维数据率为fs/m的信号,将采样率为fs的采样信号转换成m维并行低速高采样率信号s0(mk+0),…,sm-1(mk+m-1);

9、步骤12:将步骤11形成的m维并行低速高采样率信号,按第一维数据延迟(m-1)个fs,第二维数据延迟(m-2)个fs,…,第m-1维数据延迟1个fs后与第m维数据对齐同步,得到同步对齐后的m维并行低速高采样率信号;

10、步骤13:将处理时钟由原来的fs经过m分频后降低到fs’=fs/m,并且fs’与第m维数据进行同步,得到与fs’=fs/m同步的m维并行低速高采样率信号s0(mk+0),…,sm-1(mk+m-1),至此,m维数据s0(mk+0),…,sm-1(mk+m-1)组成的s(n)信号在保持原数据采样率fs及采样样本数不变的情况下,由原来的数据率fs降为fs/m。

11、进一步地,所述步骤2包括:

12、步骤21:由直接数字频率合成技术相位增量计算公式:及传统查表方式的直接数字频率合成技术处理流程,根据输出本振频率fout、采样率fs及相位累加器位数bθ(n),确定唯一的相位增量δθ作为dds的输入;

13、步骤22:根据δθ、积分器输出θ(n)、正交本振信号之间关系,进行演算及推导:

14、步骤23:根据步骤22推导结果,对传统的nco模块进行转换,以mδθ为相位增量,以fs/m工作时钟进行相位积分,得到基准序列θ0′(mk+0);

15、步骤24:根据步骤22推导结果中m维并行分解输出之间的关系式,将基准序列θ0′(mk+0)分别与iδθ相加得到θ(n)序列的第2维~第m维序列θ1(mk+1)~θm-1(mk+m-1);其中i=1,2,…,m-1;

16、步骤25:为使θ(n)序列的m维序列同步对齐,将基准序列θ0′(mk+0)进行一个处理时钟fs/m的延迟后得到θ0(mk+0),作为m维θ(n)序列的第一维序列,至此得到θ(n)序列同步后m维序列θ0(mk+0)~θm-1(mk+m-1),以θ0(mk+0)~θm-1(mk+m-1)分别作为m个查找表输入地址,从rom输出速率为fs/m的m维并行低速的正交本振信号cos0(mk+0)~cosm-1(mk+m-1)和sin0(mk+0)~sinm-1(mk+m-1)。

17、进一步地,所述步骤22包括:

18、积分器输出序列为:θ(n)={δθ+iδθ},对应nco输出序列为:cos(n)={cos(i)}和sin(n)={sin(i)},其中,i=0,1,2,…,+∞;

19、输出序列θ(n)、cos(n)、sin(n)均工作在采样率fs下,对θ(n)、cos(n)、sin(n)序列中时间指标n做euclid除法,即:令n=m·k+i,i=0,1,2,…,m-1,变形得到θ(n)及对应的cos(n)、sin(n)序列的m维输出为:

20、θ(n)序列:第0维:θ0(mk+0),…,第i维:θi(mk+i);

21、cos(n)序列:第0维:cos0(mk+0),…,第i维:cosi(mk+i);

22、sin(n)序列:第0维:sin0(mk+0),…,第i维:sini(mk+i);

23、根据θ(n)序列的m维输出公式,进行分解得到θ(n)的m维序列,表示为θi(mk+i)={δθ+(jm+i)δθ},i=0,1,…,m-1,j=0,1,…,+∞;

24、对θ(n)进行m维并行分解后,每一维的输出是以mδθ为相位增量进行积分累加,积分器的工作频率也变为fs/m,同时m维并行分解输出之间有如下关系:

25、第一维:θ0(mk+0)={以mδθ为相位增量,以fs/m为工作时钟的相位积分输出};

26、第i维:θi(mk+i)=θ0(mk+0)+iδθ=第一维输出+iδθ。

27、进一步地,所述步骤3包括:

28、将步骤2的s0(mk+0),…,sm-1(mk+m-1)分别与步骤3的cos0(mk+0)~cosm-1(mk+m-1)和sin0(mk+0)~sinm-1(mk+m-1)对应维数的数据相乘得到m维并行正交下变频后的i路信号i0(mk+0)~im-1(mk+m-1)和q路信号q0(mk+0)~qm-1(mk+m-1)。

29、进一步地,所述m维并行fir滤波处理架构是以传统单速率fir滤波处理为模型,进行算法演算及变换得到;

30、对所述m维并行fir滤波处理架构进行转换,得到全降速到fs/m的处理器可实现的m维并行fir滤波处理算法模型。

31、进一步地,所述m维并行fir滤波处理算法模型的获取过程为:

32、步骤51:传统n抽头的fir滤波算法在时域表示为:

33、

34、其中,{x(n)}为无限长的信号输入序列,{h(n)}为一个长度为n的fir滤波器系数,n为m的整数倍,上式在z域的表示为:

35、

36、将输入序列{x(n)}按m维并行分解后,式中m维并行数据分别表示为x0(zm)、z-1x1(zm)、…、z-(m-2)xm-2(zm)、z-(m-1)xm-1(zm),最终将x(z)表示为:

37、x(z)=x0(zm)+z-1x1(zm)+…+z-(m-1)xm-1(zm)

38、步骤52:以同样的方法将长度为n的fir滤波器系数{h(n)}按m维并行分解后,式中m维并行数据分别表示为h0(zm)、z-1h1(zm)、…、z-(m-2)hm-2(zm)、z-(m-1)hm-1(zm),最终将h(z)表示为:

39、h(z)=h0(zm)+z-1h1(zm)+…+z-(m-1)hm-1(zm)

40、步骤53:根据z域的fir滤波处理算法表示式:y(z)=h(z)x(z),对步骤51的m维并行x(z)表示式和步骤52的m维并行h(z)表示式进行计算,用矩阵形式表示如下:

41、

42、步骤54:步骤53中z-m即为m个fs延迟,每一维数据均工作在降速后的fs/m时钟下,所以一个z-m即为一个fs/m延迟,表示为一个延迟d,对步骤53推导得出的fir滤波处理m维并行分解公式进行转化并实现,构建出全降速到fs/m的处理器可实现的m维并行fir滤波处理算法模型。

43、进一步地,所述步骤4包括:

44、步骤41:根据正交fir滤波运算公式y=(i+jq)*(h_i+jh_q)=i*h_i-q*h_q+j(i*h_q+q*h_i),处理中需要将正交fir滤波处理分为4组滤波进行处理,以步骤1的方法设计m维并行fir滤波器系数虚部h_i0(mk+0)~h_im-1(mk+m-1)和滤波器系数虚部h_q0(mk+0)~h_qm-1(mk+m-1);

45、步骤42:以步骤4设计的m维并行fir滤波处理算法模型作为每一组滤波处理的算法结构,分别进行4组滤波器计算:

46、第1组滤波器输入为:m维并行i数据i0(mk+0)~im-1(mk+m-1)和滤波器系数实部h_i0(mk+0)~h_im-1(mk+m-1),得到滤波器输出:y_ii0(mk+0)~y_iim-1(mk+m-1);

47、第2组滤波器输入为:m维并行i数据i0(mk+0)~im-1(mk+m-1)和滤波器系数虚部h_q0(mk+0)~h_qm-1(mk+m-1),得到滤波器输出:y_iq0(mk+0)~y_iqm-1(mk+m-1);

48、第3组滤波器输入为:m维并行q数据q0(mk+0)~qm-1(mk+m-1)和滤波器系数实部h_i0(mk+0)~h_im-1(mk+m-1),得到滤波器输出:y_qi0(mk+0)~y_qim-1(mk+m-1);

49、第4组滤波器输入为:m维并行q数据q0(mk+0)~qm-1(mk+m-1)和滤波器系数虚部h_q0(mk+0)~h_qm-1(mk+m-1),得到滤波器输出:y_qq0(mk+0)~y_qqm-1(mk+m-1);

50、步骤43:将第1组滤波器的输出y_ii0(mk+0)~y_iim-1(mk+m-1)和第4组滤波器的输出y_qq0(mk+0)~y_qqm-1(mk+m-1)进行对应维数的数据相减,得到高速数据全低速处理后的m维并行i路信号输出y_i0(mk+0)~y_im-1(mk+m-1),将第2组滤波器的输出y_iq0(mk+0)~y_iqm-1(mk+m-1)和第3组滤波器的输出y_qi0(mk+0)~y_qim-1(mk+m-1)进行对应维数的数据相加,得到高速数据全低速处理后的m维并行q路信号输出y_q0(mk+0)~y_qm-1(mk+m-1)。

51、由于采用了上述技术方案,本发明具有如下的优点:

52、1、本发明在不改变信号采样率的情况下可实现真正意义上的全降速处理,从而避免了由于无法处理高速数据流而采用欠采样或低采样率对信号进行采样,以及对信号进行抽取降速处理带来的信噪比损失,从而提高监控器的处理精度;

53、2、本发明使信号处理流程简化为只需要正交混频+fir滤波处理即可实现高速采样信号处理,级数更少,大大提高了信号处理的实时性;

54、3、本发明采用对高速信号进行时域处理的方法,使信号处理数度及实时性不受计算点数的限制,既保证了信号处理的高精度也保证了实时性。

- 还没有人留言评论。精彩留言会获得点赞!