设计集成电路装置的系统、集成电路装置及其操作方法与流程

本揭示内容是关于一种集成电路装置、设计集成电路装置的系统及操作集成电路装置的方法。

背景技术:

1、集成电路(integrated circuit,ic)装置,包含一或多个半导体装置,其代表ic布局(亦称为“布局”或“布局图”)。布局为阶层式的,且包含多个模组,这些模组根据半导体装置的设计规格,实现较高级的功能。这些模组通常由一些单元的组合所构成,每一单元代表一或多个半导体架构,这些半导体架构用以执行特定功能。具有预先设计好的布局的单元,有时被称为标准单元,储存于标准单元数据库(下文简称为“数据库”或“单元数据库”),且可被不同工具存取,例如电子设计自动化(electronic design automation,eda)工具,用以产生、最佳化、验证ic设计。举例而言,ic设计的布局是根据ic设计的放置及布线作业所产生,其中不同的电路或单元放置于布局中,然后布线用于定义在电路或单元中的电性连接。

技术实现思路

1、本揭示内容的一些实施例包含一种集成电路装置包含一主闩锁电路,包含一第一时脉输入和一数据输出,一副闩锁电路,包含一第二时脉输入和一数据输入,数据输入电性耦接至主闩锁电路之数据输出,以及一时脉电路。时脉电路通过一第一电连接电性耦接至第一时脉输入,第一电连接用以具有一第一时间延迟,第一时间延迟介于时脉电路和第一时脉输入之间。时脉电路通过一第二电连接电性耦接至第二时脉输入,第二电连接用以具有一第二时间延迟,第二时间延迟介于时脉电路以及第二时脉输入之间。第一时间延迟长于第二时间延迟。

2、本揭示内容的一些实施例包含一种设计集成电路装置的系统包含至少一处理器,以及至少一记忆体,储存用于一或多个程序的计算机程序码。当至少一处理器执行储存于至少一记忆体的计算机程序码时,计算机程序码和至少一处理器用以致使系统执行产生一集成电路装置的一布局,布局储存于一非暂时性计算机可读媒体中。产生布局包含:在布局中,放置一主闩锁电路、一副闩锁电路和一时脉电路,以及执行布线以电性耦接时脉电路至主闩锁电路和副闩锁电路。在所述布线中,一第一电连接布线自时脉电路至主闩锁电路,第一电连接实体上长于一第二电连接,第二电连接布线自时脉电路至副闩锁电路。

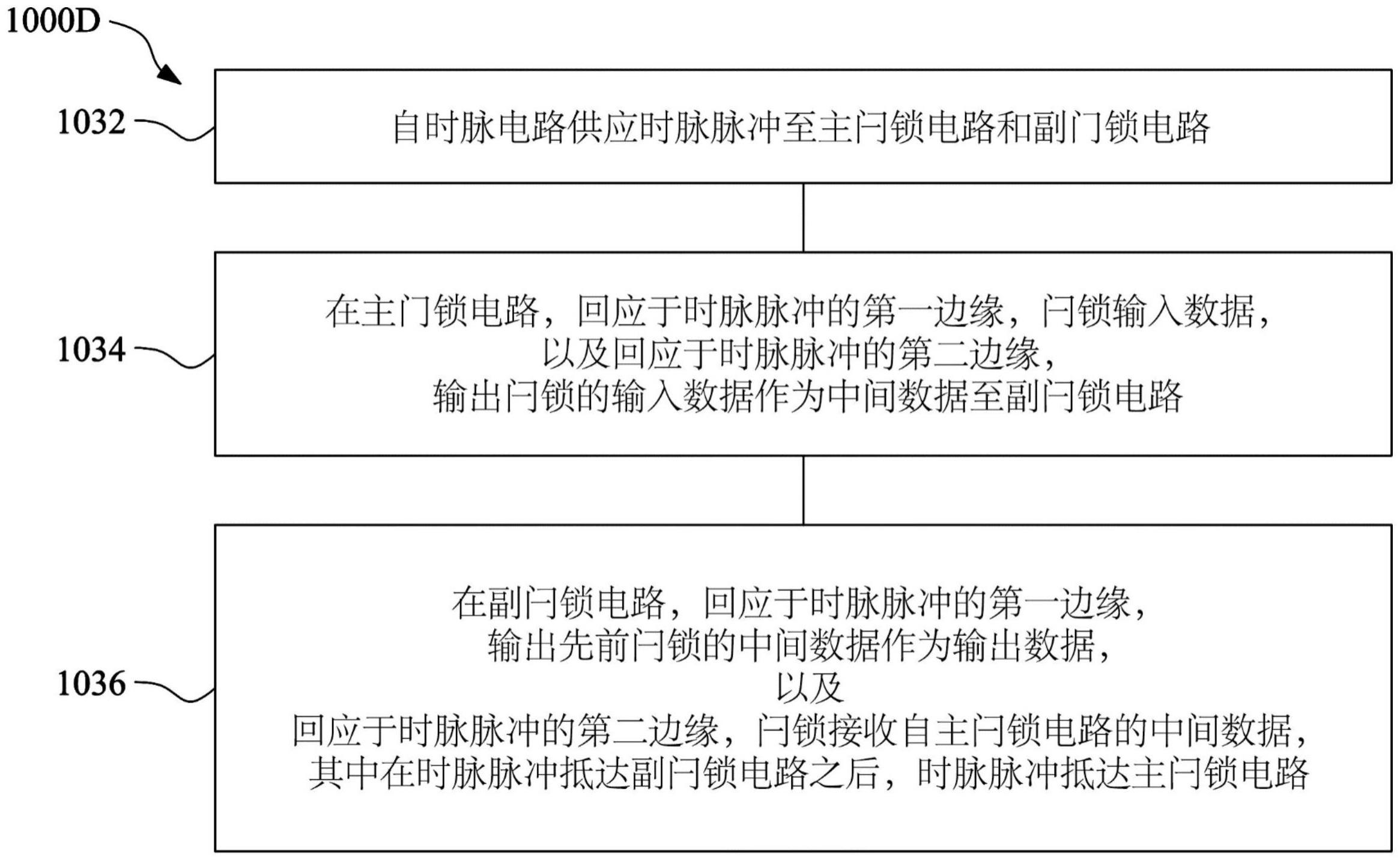

3、本揭示内容的一些实施例包含一种操作集成电路装置的方法包含:自一时脉电路供应一时脉脉冲至一主闩锁电路和一副闩锁电路。所述方法进一步包含,在主闩锁电路,回应于时脉脉冲的一第一边缘,闩锁输入数据,以及回应于时脉脉冲的一第二边缘,输出闩锁的输入数据作为中间数据至副闩锁电路。所述方法进一步包含,在副闩锁电路,回应于时脉脉冲的第一边缘,输出先前闩锁的中间数据作为输出数据,以及回应于时脉脉冲的第二边缘,闩锁接收自主闩锁电路的中间数据。在时脉脉冲抵达副闩锁电路之后,时脉脉冲抵达主闩锁电路。

技术特征:

1.一种集成电路装置,其特征在于,包含:

2.如权利要求1所述的集成电路装置,其特征在于,

3.如权利要求2所述的集成电路装置,其特征在于,

4.如权利要求1所述的集成电路装置,其特征在于,

5.如权利要求1所述的集成电路装置,其特征在于,进一步包含:

6.如权利要求5所述的集成电路装置,其特征在于,

7.一种设计集成电路装置的系统,其特征在于,包含:

8.如权利要求7所述的系统,其特征在于,

9.一种操作集成电路装置的方法,其特征在于,包含:

10.如权利要求9所述的方法,其特征在于,

技术总结

一种集成电路(integrated circuit,IC)装置,包含一主闩锁电路,具有一第一时脉输入与一数据输出、一副闩锁电路,具有一第二时脉输入与一数据输入,电性耦接至该主闩锁电路的该数据输出、以及一时脉电路。该时脉电路通过一第一电连接电性耦接至该第一时脉输入,该第一电连接用以具有一第一时间延迟,该第一时间延迟介于该时脉线路与该第一时脉输入之间。该时脉电路通过一第二电连接电性耦接至该第二时脉输入,该第二电连接用以具有一第二时间延迟,该第二时间延迟介于该时脉电路与该第二时脉输入之间。该第一时间延迟长于该第二时间延迟。

技术研发人员:林钲祐,简永溱,高嘉鸿,高章瑞,庄惠中

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!