一种在芯板层及增层均埋入元器件的PCB板结构及其制作方法与流程

本技术涉及一种在pcb板结构中制作元器件的,尤其涉及一种在芯板层及增层均埋入元器件的pcb板结构及其制作方法。

背景技术:

1、集成电路芯片的制造过程主要包括以下几个阶段:集成电路芯片的设计阶段、集成电路芯片的制作阶段、集成电路芯片的封装阶段、以及集成电路芯片的测试阶段。随着集成电路芯片的制造工艺的不断进步,电子产品向高速化、高集成度和高可靠性的方向迅速发展,对集成电路的制造工艺的要求也在不断提高。

2、目前嵌埋元器件的pcb板,内埋元件类型包括存储芯片、功率芯片、逻辑芯片这样的主动元器件,也包括贴片式的电容、电阻和电感等被动元件。不同属性的内埋元器件厚度往往不一致,即便是相同属性的元器件,也会因为元件型号的差异导致厚度不一致。如常规的c0402电容厚度为0.5mm,而常规的c0201电容厚度只有0.3mm。

3、而现有的内埋多种元器件的pcb板,如图3所示,采用的是所有元器件同层埋入的制作工艺流程:

4、(a)芯板层经贴膜→曝光→显影→蚀刻→褪膜流程,完成芯板层图形转移,其中内层芯板的厚度比最大的元件厚度大15-20um;如图3(a),其中芯板为3层结构,芯板包括中间的内层芯板。(b)芯板铣槽,铣槽加工方式可以是钢模冲切、机械铣、co2镭射钻及uv切割中的一种或多种;

5、(c)芯板层背面用贴胶机贴高温胶带,胶带为25um厚的聚酰亚胺层和25um厚的亚克力胶层的组合;

6、(d)贴元器件,元件通过盲槽底部胶带固定。元器件包括各种类型的芯片,贴片式的电容、电阻和电感等;

7、(e)芯板层top面排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将盲槽填满。粘结片包括pp或abf半固化粘结片材,铜箔包括3um载体铜箔、12um铜箔、18um铜箔、35um铜箔等其中的一种或多种。

8、(f)撕掉芯板层背面的高温胶带;

9、(g)芯板层bottom面排板,盖上粘结片及铜箔,然后进压机高温压合形成第1增层;

10、(h)第1增层做激光钻孔;

11、(i)第1增层做填孔电镀,填平激光钻盲孔;

12、(j)第1增层经贴膜→曝光→显影→蚀刻→褪膜流程,完成第1增层图形转移;

13、(k)上下两面排板,盖上粘结片及铜箔,然后进压机高温压合形成第2增层;

14、(l)第2增层做激光钻孔;

15、(m)第2增层做填孔电镀,填平激光钻盲孔;

16、然后,第2增层经贴膜→曝光→显影→蚀刻→褪膜流程,完成第2增层图形转移。重复上述步骤,最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

17、通过上述的工艺流程,制作出的pcb板结构如图4所示,发明人发现以上现有流程加工形成的产品结构有以下缺点:

18、1、比较薄的元器件(芯片)的上方出现了空洞,只有最厚的那款元器件可以双面都通过盲孔连接pcb网络并扇出信号,其余的都只能单面导通和扇出,这对于产品的整体布线和网络设计是一种浪费;

19、2、在现有产品结构中,薄元件上下严重不对称,部分元件受结构不对称产生的应力影响,造成元件弯折甚至开裂,最终导致产品报废。

20、针对上述问题,发明人认为有必要提供一种减少浪费结构空间,增加信号扇出通道,部分元件结构免受不对称应力影响的新型pcb板结构制作方式。

技术实现思路

1、本技术实施例提供一种在芯板层及增层均埋入元器件的pcb板结构的技术方案,用以解决现有技术中不同厚度芯片制作中浪费结构空间,部分元件受结构不对称产生的应力影响,容易导致产品报废的技术问题。

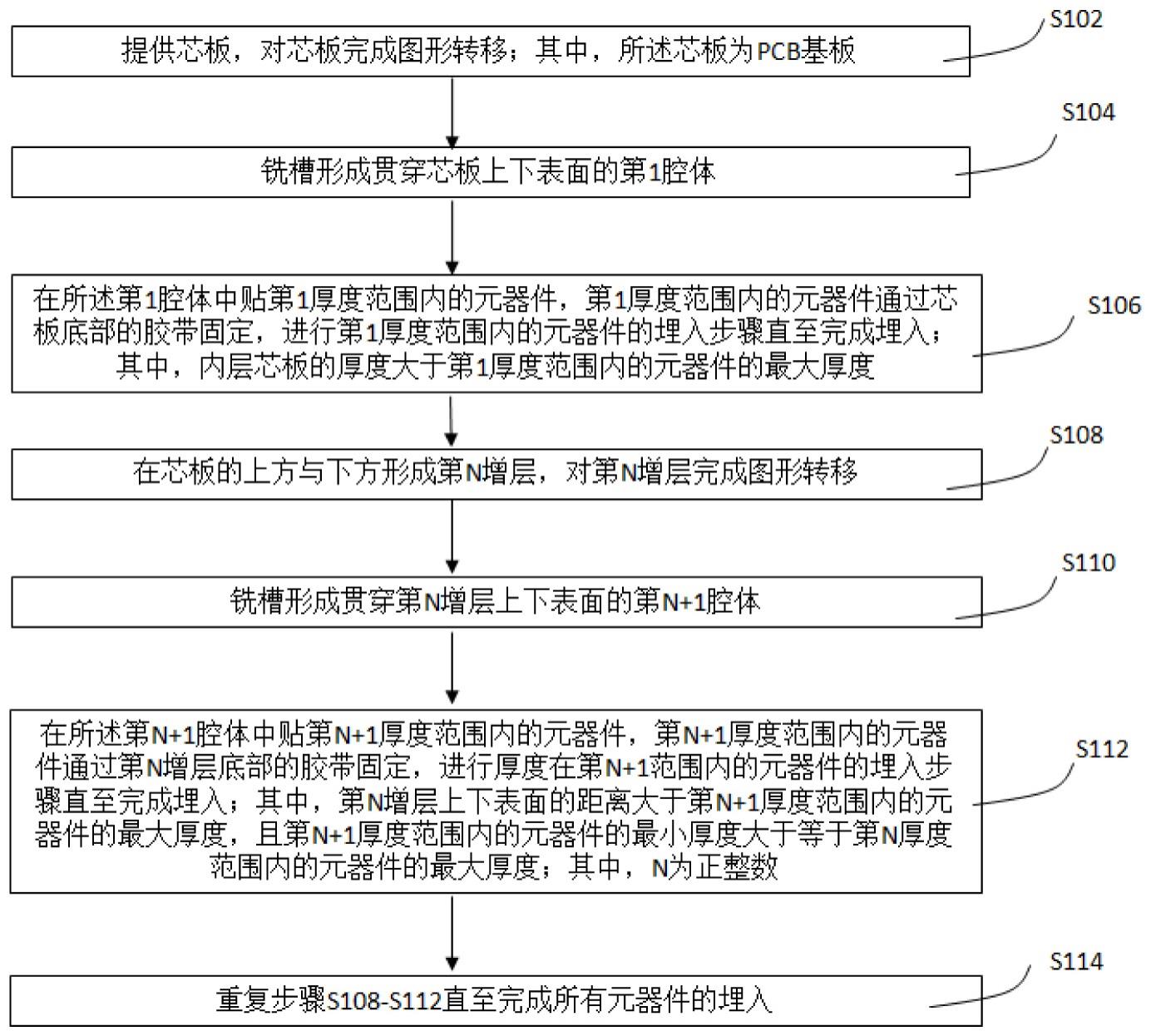

2、本技术实施例提供一种在芯板层及增层均埋入元器件的pcb板结构的制作方法,包括如下步骤:

3、s102,提供芯板,对芯板完成图形转移;其中,所述芯板为pcb基板;

4、s104,铣槽形成贯穿芯板上下表面的第1腔体;

5、s106,在所述第1腔体中贴第1厚度范围内的元器件,第1厚度范围内的元器件通过芯板底部的胶带固定,完成第1厚度范围内的元器件的埋入;其中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

6、s108,在芯板的上方与下方形成第n增层;对第n增层完成图形转移;

7、s110,铣槽形成贯穿第n增层上下表面的第n+1腔体;

8、s112,在所述第n+1腔体中贴第n+1厚度范围内的元器件,第n+1厚度范围内的元器件通过第n增层底部的胶带固定,完成厚度在第n+1范围内的元器件的埋入;其中,第n增层上下表面的距离大于第n+1厚度范围内的元器件的最大厚度,且第n+1厚度范围内的元器件的最小厚度大于等于第n厚度范围内的元器件的最大厚度;其中,n为正整数;

9、s114,重复步骤s108-s112直至完成所有元器件的埋入。

10、进一步的,所述芯板为双面覆铜板。

11、进一步的,步骤s106中,所述胶带贴在芯板底部覆盖第1腔体在芯板下表面的贯通口。

12、进一步的,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

13、进一步的,所述形成第n增层包括:

14、s1082,在芯板层上方排板,盖上粘结片及铜箔,经高温压合后粘结片的流胶将第n腔体填满;

15、s1084,去除所述胶带;

16、s1086,芯板层下方排板,盖上粘结片及铜箔,然后进压机高温压合形成第n增层。

17、进一步的,粘结片包括pp或abf半固化粘结片材。

18、进一步的,铜箔包括3um载体铜箔、12um铜箔、18um铜箔或35um铜箔中的一种或多种。

19、进一步的,所述形成第n增层还包括做激光钻盲孔,电镀填平所述激光钻盲孔。

20、进一步的,所述图形转移包括贴膜、曝光、显影、蚀刻和褪膜流程。

21、进一步的,所述胶带为25um厚的聚酰亚胺层和25um厚的亚克力胶层的组合。

22、进一步的,所述铣槽包括钢模冲切、机械铣、co2镭射钻或uv切割中的一种或多种。

23、进一步的,所述第n厚度范围内的元器件相互之间的厚度差不超过10um。

24、进一步的,还包括最外层的压合、激光钻孔、机械钻孔、电镀、图形转移、阻焊加工、表面处理和切割成形。

25、进一步的,所述去除所述胶带通过人工去除或智能设备去除。

26、进一步的,第n增层包括芯板上方和下方的导电层和/或导热层。

27、本技术实施例还提供一种在芯板层及增层均埋入元器件的pcb板结构,包括芯板,所述芯板为pcb基板;其中,芯板具有贯穿芯板上下表面的第1腔体;第1厚度范围内的元器件嵌埋于所述第1腔体中,内层芯板的厚度大于第1厚度范围内的元器件的最大厚度;

28、第n增层;具有贯穿第n增层上下表面的第n+1腔体;

29、第n+1厚度范围内的元器件嵌埋于所述第n+1腔体中;其中,第n增层上下表面的距离大于第n+1厚度范围内的元器件的最大厚度,且第n+1厚度范围内的元器件的最小厚度大于等于第n厚度范围内的元器件的最大厚度;其中,n为正整数。

30、进一步的,所述芯板为双面覆铜板。

31、进一步的,内层芯板的厚度比第1厚度范围内的元器件的最大厚度大15-20um。

32、进一步的,所述第n增层还包括芯板上方和下方的导电层和/或导热层。

33、进一步的,所述第n厚度范围内的元器件相互之间的厚度差不超过10um。

34、本技术实施例还提供一种电子器件,包括前述的在芯板层及增层均埋入元器件的pcb板结构。

35、本技术实施例还提供一种电子设备,包括前述的在芯板层及增层均埋入元器件的pcb板结构。

36、本技术提供的实施例至少具有以下有益效果:

37、本技术提供一种在芯板层及增层均埋入元器件的pcb板结构的制作方法,通过对现有的埋入元器件的pcb板结构制作工艺进行改造,按照厚度范围将不同厚度的芯片分成若干组;将厚度低于内层芯板的第1厚度范围的芯片嵌埋于内层芯板所在层的第1腔体内,制作第1增层,第1增层是第1厚度范围芯片的导电和/或散热层,将第2厚度范围的芯片埋设在第1增层厚度范围内的第2腔体,依次类推,将不同厚度的芯片分批次埋入,可实现充分布线和提升产品的空间利用率,解决了空腔上方填胶空洞和靠近空腔位置介电层厚度偏薄的问题;在新产品结构中,能有效减少浪费结构空间,增加信号扇出通道,部分元件结构免受不对称应力影响,延长使用寿命。

- 还没有人留言评论。精彩留言会获得点赞!