金属浮栅存储器及其制造方法与流程

本申请涉及半导体,具体涉及一种金属浮栅存储器及其制造方法。

背景技术:

1、随着微电子技术的发展,存储器面临一系列的挑战,例如更快的速度、更低的功耗和更高的集成度等。对于传统的多晶硅浮栅存储器而言,多晶硅浮栅的厚度随着器件特征尺寸的减小而同步减薄,使得具有高能量的入射电子增多。大量高能入射电子会穿过多晶硅浮栅对衬底造成损伤,产生更多的陷阱和缺陷,影响器件的可靠性。为了克服这一问题,以金属代替多晶硅作为浮栅的方案被提出来。

2、金属浮栅存储器利用水平电场进行写操作,通过金属浮栅顶端的无电压耦合进行擦除操作。金属浮栅的材料为氮化钛(tin),受周围环境和工艺过程影响,金属浮栅顶端区域的tin因氧化导致性能发生变化,造成擦除电压偏高,速度过慢。

技术实现思路

1、鉴于以上所述现有技术的缺点,本申请的目的在于提供一种金属浮栅存储器及其制造方法,用于解决现有技术中金属浮栅顶端区域因氧化导致擦除电压偏高及速度过慢的问题。

2、为实现上述目的及其它相关目的,本申请提供一种金属浮栅存储器及其制造方法。该技术方案如下:

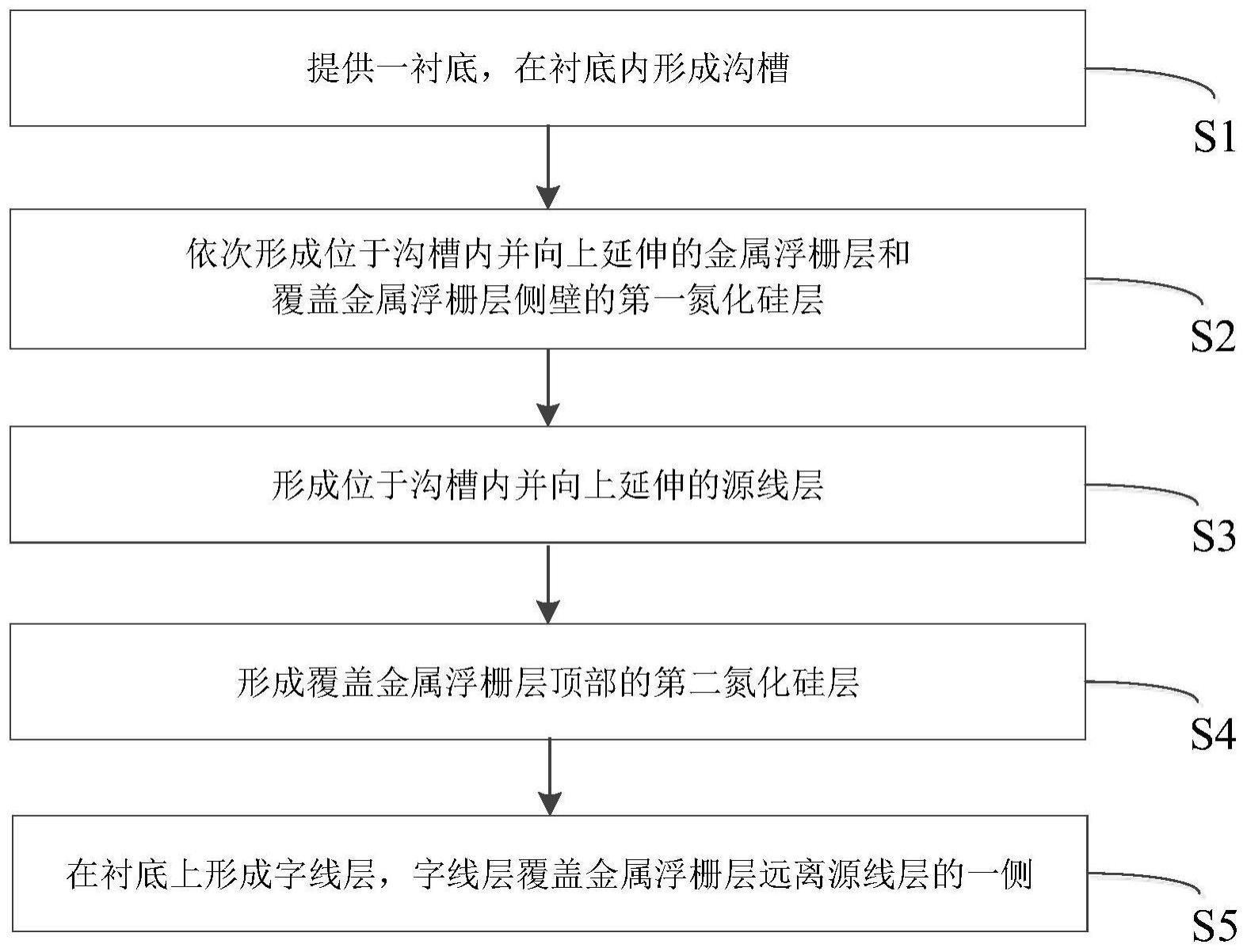

3、第一方面,本申请实施例提供了一种金属浮栅存储器的制造方法,包括:

4、步骤s1,提供一衬底,在衬底内形成沟槽;

5、步骤s2,依次形成位于沟槽内并向上延伸的金属浮栅层和覆盖金属浮栅层侧壁的第一氮化硅层;

6、步骤s3,形成位于沟槽内并向上延伸的源线层;

7、步骤s4,形成覆盖金属浮栅层顶部的第二氮化硅层;

8、步骤s5,在衬底上形成字线层,字线层覆盖金属浮栅层远离源线层的一侧。

9、优选的,第一氮化硅层的顶部和金属浮栅层的顶部平齐。

10、优选的,在衬底内形成沟槽的步骤包括:在衬底上依次形成第一氧化层、字线材料层、第二氧化层和硬掩膜层;依次刻蚀衬底的存储区上的硬掩膜层、第二氧化层、字线材料层和第一氧化层,直至形成露出衬底的开口;沿开口向下继续刻蚀部分衬底,以使开口延伸至衬底内,开口位于衬底内的部分构成沟槽。

11、优选的,硬掩膜层的厚度为1750埃-1950埃。

12、优选的,形成源线层之后,在形成第二氮化硅层之前还包括在源线层的顶部形成第一介质层的步骤,第一介质层的顶部和第一氮化硅层的顶部平齐。

13、优选的,采用原子层沉积工艺形成第一氮化硅层、第一介质层和第二氮化硅层。

14、优选的,原子层沉积工艺的温度为250℃~350℃。

15、优选的,形成字线层之后,还包括在衬底上依次形成第二介质层和擦除栅的步骤。

16、第二方面,本申请实施例提供了一种根据前述制造方法制备的金属浮栅存储器,该金属浮栅存储器中的金属浮栅层朝向源线层的一侧侧壁上形成有第一氮化硅层,第一氮化硅层的顶部和金属浮栅层的顶部平齐,金属浮栅层的顶部形成有第二氮化硅层。

17、优选的,金属浮栅层的材料为氮化钛。

18、如上所述,本申请提供的完整的金属浮栅存储器及其制造方法,具有以下有益效果:可以防止金属浮栅层顶部区域的氧化,降低擦除电压,提升擦除速度。

技术特征:

1.一种金属浮栅存储器的制造方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述第一氮化硅层的顶部和所述金属浮栅层的顶部平齐。

3.根据权利要求1所述的方法,其特征在于,在所述衬底内形成所述沟槽的步骤包括:在所述衬底上依次形成第一氧化层、字线材料层、第二氧化层和硬掩膜层;依次刻蚀所述衬底的存储区上的所述硬掩膜层、所述第二氧化层、所述字线材料层和所述第一氧化层,直至形成露出所述衬底的开口;沿所述开口向下继续刻蚀部分所述衬底,以使所述开口延伸至所述衬底内,所述开口位于所述衬底内的部分构成所述沟槽。

4.根据权利要求3所述的方法,其特征在于,所述硬掩膜层的厚度为1750埃-1950埃。

5.根据权利要求1所述的方法,其特征在于,形成所述源线层之后,在形成所述第二氮化硅层之前还包括在所述源线层的顶部形成第一介质层的步骤,所述第一介质层的顶部和所述第一氮化硅层的顶部平齐。

6.根据权利要求5所述的方法,其特征在于,采用原子层沉积工艺形成所述第一氮化硅层、所述第一介质层和所述第二氮化硅层。

7.根据权利要求6所述的方法,其特征在于,所述原子层沉积工艺的温度为250℃~350℃。

8.根据权利要求1所述的方法,其特征在于,形成所述字线层之后,还包括在所述衬底上依次形成第二介质层和擦除栅的步骤。

9.一种根据权利要求1-8中任一项所述的方法制备的金属浮栅存储器,其特征在于,所述金属浮栅存储器中的金属浮栅层朝向源线层的一侧侧壁上形成有第一氮化硅层,所述第一氮化硅层的顶部和所述金属浮栅层的顶部平齐,所述金属浮栅层的顶部形成有第二氮化硅层。

10.根据权利要求9所述的金属浮栅存储器,其特征在于,所述金属浮栅层的材料为氮化钛。

技术总结

本申请提供一种金属浮栅存储器及其制造方法,所述方法包括:步骤S1,提供一衬底,在衬底内形成沟槽;步骤S2,依次形成位于沟槽内并向上延伸的金属浮栅层和覆盖金属浮栅层侧壁的第一氮化硅层;步骤S3,形成位于沟槽内并向上延伸的源线层;步骤S4,形成覆盖金属浮栅层顶部的第二氮化硅层;步骤S5,在衬底上形成字线层,字线层覆盖金属浮栅层远离源线层的一侧。通过形成覆盖金属浮栅层侧壁的第一氮化硅层和覆盖金属浮栅层顶部的第二氮化硅层,可以防止金属浮栅层顶部区域的氧化,降低擦除电压,提升擦除速度。

技术研发人员:顾珍,张磊,陈昊瑜

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!