基于FPGA的LDPC编译码准循环构造改进方法

本发明涉及信息通信,尤其涉及一种基于fpga的ldpc编译码准循环构造改进方法。

背景技术:

1、随着科技的发展,编解码技术应用广泛,低密度奇偶校验ldpc码技术始终是研究与应用的热点。其校验矩阵具有稀疏性,性能逼近香农极限,且描述和实现简单,易于进行理论分析和研究,译码简单且可实行并行操作,适合硬件实现。

2、ldpc码的构造方法包括随机生成和结构化生成两大类:

3、随机矩阵没有明显的结构。这类构造方法比较适合较长的码块,当码长在百万级别,采用非规则ldpc码,可以很好地逼近香农容量。但是随机生成的矩阵由于没有特别的结构特征,译码实现没有简便算法,使其在实际系统中的算法复杂度高、吞吐量低,难以推广。

4、结构化矩阵相比之下更具优越性。目前最为广泛应用的是准循环结构,该种结构最初在规则ldpc码中使用,并被推广到非规则ldpc码,其设计的自由度更大,性能优化的空间也有所提高。虽然结构性设计对性能有一定的影响,不一定能十分逼近香农容量,但译码算法得到大量的简化,复杂度降低。另外,准循环结构可以降低译码时延以增加数据吞吐量,因此在实际系统中获得广泛应用。

5、然而,现有技术的编译码方案较少地综合考虑纠错性能和硬件实现复杂度之间的关系,在实际应用中仍旧存在复杂度高,性能较差的问题,缺少一种高效精准的ldpc编译码准循环构造改进方法。

技术实现思路

1、有鉴于此,本发明实施例提出基于fpga的ldpc编译码准循环构造改进方法,纠错性强、复杂度低、可靠性高,具有良好的应用前景。

2、本发明实施例提出的基于fpga的ldpc编译码准循环构造改进方法,包括:

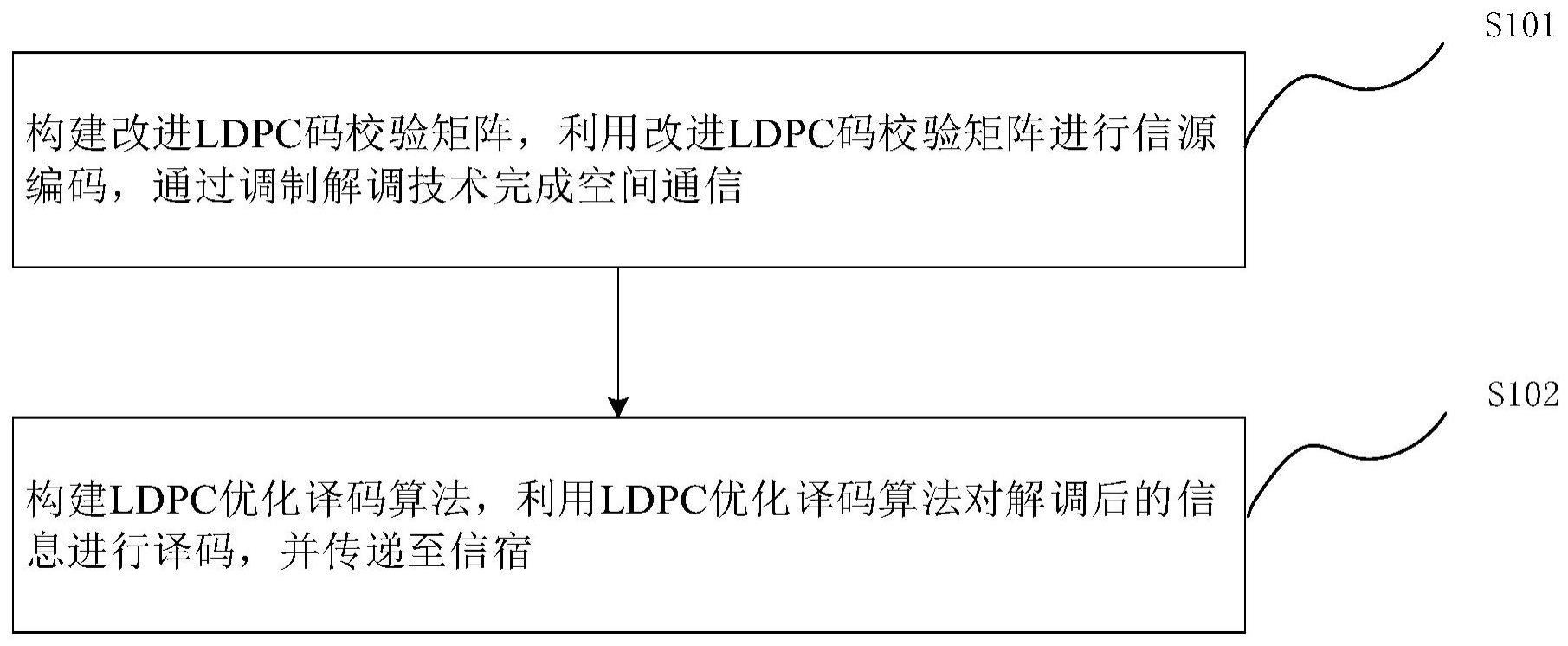

3、构建改进ldpc码校验矩阵,利用所述改进ldpc码校验矩阵进行信源编码,通过调制解调技术完成空间通信;

4、构建ldpc优化译码算法,利用所述ldpc优化译码算法对解调后的信息进行译码,并传递至信宿。

5、示范性地,所述改进ldpc码校验矩阵包括π旋转信息位矩阵和双角线校验位矩阵。

6、示范性地,所述π旋转信息位矩阵包括第一π旋转子阵、第二π旋转子阵、第三π旋转子阵和第四π旋转子阵,所述第二π旋转子阵、第三π旋转子阵和第四π旋转子阵由所述第一π旋转子阵按顺时针方向分别旋转90°、180°和270°得到;所述双角线校验位矩阵的主对角线和与主对角线平行紧挨的对角线元素为1,其余元素为0。

7、示范性地,所述构建ldpc优化译码算法,利用所述ldpc优化译码算法对解调后的信息进行译码包括:

8、更新计算每个变量节点从信道获取的初始化信息,并计算校验节点从相邻变量节点获取的信息值;

9、利用信息值进行迭代更新计算,所述迭代更新计算包括第一迭代计算过程和第二迭代计算过程;

10、进行译码判决校验以判断是否译码成功。

11、示范性地,所述利用信息值进行迭代更新计算包括:

12、分别进行所述第一迭代计算和第二迭代计算,所述第一迭代计算为水平迭代过程,所述第二迭代计算为垂直迭代过程;

13、计算所有变量节点的后验概率似然比。

14、示范性地,所述进行译码判决校验以判断是否译码成功包括:

15、利用所述后验概率似然比判定节点信息值,若所述后验概率似然比大于0,则变量节点对应的节点信息值为0,若所述后验概率似然比小于0,则所述节点信息值为1,并生成信息序列;

16、将生成的所述信息序列进行校验方程检验,判断译码是否成功;

17、若不成功,则继续进行变量节点信息与校验节点信息迭代,直到满足迭代次数要求。

18、根据权利要求4所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,改进ldpc码的信道编码码长为2400、码率为1/2、迭代次数为15次。

19、本发明提出了基于fpga的ldpc编译码准循环构造改进方法,该方法包括:构建改进ldpc码校验矩阵,利用改进ldpc码校验矩阵进行信源编码,通过调制解调技术完成空间通信;构建ldpc优化译码算法,利用ldpc优化译码算法对解调后的信息进行译码,并传递至信宿。本发明基于fpga硬件开发平台实现ldpc编译码,系统纠错性强、复杂度低、可靠性高,具有良好的应用前景。

技术特征:

1.一种基于fpga的ldpc编译码准循环构造改进方法,其特征在于,包括:

2.根据权利要求1所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,所述改进ldpc码校验矩阵包括π旋转信息位矩阵和双角线校验位矩阵。

3.根据权利要求2所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,所述π旋转信息位矩阵包括第一π旋转子阵、第二π旋转子阵、第三π旋转子阵和第四π旋转子阵,所述第二π旋转子阵、第三π旋转子阵和第四π旋转子阵由所述第一π旋转子阵按顺时针方向分别旋转90°、180°和270°得到;所述双角线校验位矩阵的主对角线和与主对角线平行紧挨的对角线元素为1,其余元素为0。

4.根据权利要求3所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,所述构建ldpc优化译码算法,利用所述ldpc优化译码算法对解调后的信息进行译码包括:

5.根据权利要求4所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,所述利用信息值进行迭代更新计算包括:

6.根据权利要求5所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,所述进行译码判决校验以判断是否译码成功包括:

7.根据权利要求4所述的基于fpga的ldpc编译码准循环构造改进方法,其特征在于,改进ldpc码的信道编码码长为2400、码率为1/2、迭代次数为15次。

技术总结

本发明提出了基于FPGA的LDPC编译码准循环构造改进方法,该方法包括:构建改进LDPC码校验矩阵,利用改进LDPC码校验矩阵进行信源编码,通过调制解调技术完成空间通信;构建LDPC优化译码算法,利用LDPC优化译码算法对解调后的信息进行译码,并传递至信宿。本发明基于FPGA硬件开发平台实现LDPC编译码,系统纠错性强、复杂度低、可靠性高,具有良好的应用前景。

技术研发人员:常峻铭,王昊

受保护的技术使用者:长春理工大学

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!