数字成形滤波方法、装置、数字成形滤波器及电子设备与流程

本技术涉及信号处理,尤其涉及一种数字成形滤波方法、装置、数字成形滤波器及电子设备。

背景技术:

1、在现代通信系统中,数字成形滤波器在收发设备中一般有两种放置方式,一种为放置在发射端,另一种为分别放置在发射端和接收端,又称为发射成形滤波器和接收匹配滤波器以实现信号最佳接收。以发射成形滤波器为例,其采用有限长单位冲激响应(finiteimpulse response,fir)滤波器架构实现,fir滤波器的系数即来自于平方根升余弦的冲激响应曲线;从平方根升余弦曲线中获取系数时,会有span(跨符号个数)、sps(每个符号的采样点数)两个参数,当实现一个span为m,sps为p的成形滤波器时,其滤波器抽头个数即为n=m*p+1。fir滤波器的处理过程的表达式如下所示:

2、

3、其中,x(k)为输入信号,hn为滤波器系数。其实现结构如图1所示。

4、传统的成形滤波器实现时,为了得到n个符号的成形滤波结果,需要将原始的m个符号在滤波前,先插值到m*p个数据样本,然后再进行上述的m*p阶的fir滤波处理。对于给定的跨符号个数m,当符号速率与系统采样速率之前的差异越大时,即p值越大,则滤波器所需的阶数则越大,则需要消耗的乘法器和加法器个数将成倍的增加,使得实现滤波器所需资源和成本倍增。为了解决此问题,传统的做法有两种:第一种是变采样时钟方式,即通过设计数字模拟转换器(digital to analog converter,dac)、模拟数字转换器(analog todigital converter,adc)的采样速率,使其工作在4倍或8倍符号速率;通过动态配置系统的工作时钟,使得所需的插值倍数控制在4倍或8倍,滤波器的阶数处于一个可以接受的范围内。第二种是在成形滤波器之后,再级联插值滤波器,通过插值滤波器来实现变采样速率。

5、但无论采用哪种方式,其适应的范围较窄;例如,通过控制dac、adc的采样速率方式,当符号速率跨越度较大时,比如从bps~几百mbps范围变化时,则会导致硬件的采样时钟同样需要具备此等大范围程度的变化,这对硬件上产生高精度、低相噪的采样时钟提出了严峻的挑战,通常需要使用复杂的时钟网络来进行频带选择和模拟带通滤波,造成硬件设计的复杂度和成本的巨大增加。又例如,采用专用插值滤波器级联的方式则需要额外的插值滤波器来实现,且插值的倍数时需要动态可变的,将同样的插值倍数问题转移给了插值滤波器,问题本质并未得到解决,同样增加了系统的复杂度。同时对于这两种实现方式,均需要其插值倍数为整数,对于任意码率下的通信应用中,其插值倍数可能为非整数,进一步缩小了传统成形滤波器的应用范围;此外,对于进行超高码率的通信时,比如gbps级别通信速率需求时,传统做法为将滤波器进行并行实现,当并行度为x时,其所需的资源将变为原来的x倍(即乘法器和加法器将均需要x*n个),更加导致需要巨大的资源。

6、综上所述,传统的成形滤波方式有如下缺点:适应码率范围窄,无法适应符号速率跨度较大的应用场景;插值倍数需要额外的变速率插值滤波来实现;无法适应插值倍数为非整数的情况;无法适应超高码率通信系统。

7、针对上述的问题,尚未提出有效地解决方案。

技术实现思路

1、本技术实施例提供了一种数字成形滤波方法、装置、数字成形滤波器及电子设备,以至少解决相关技术中的数字成形滤波方式适应码率范围窄,无法适应符号速率跨度较大的应用场景的技术问题。

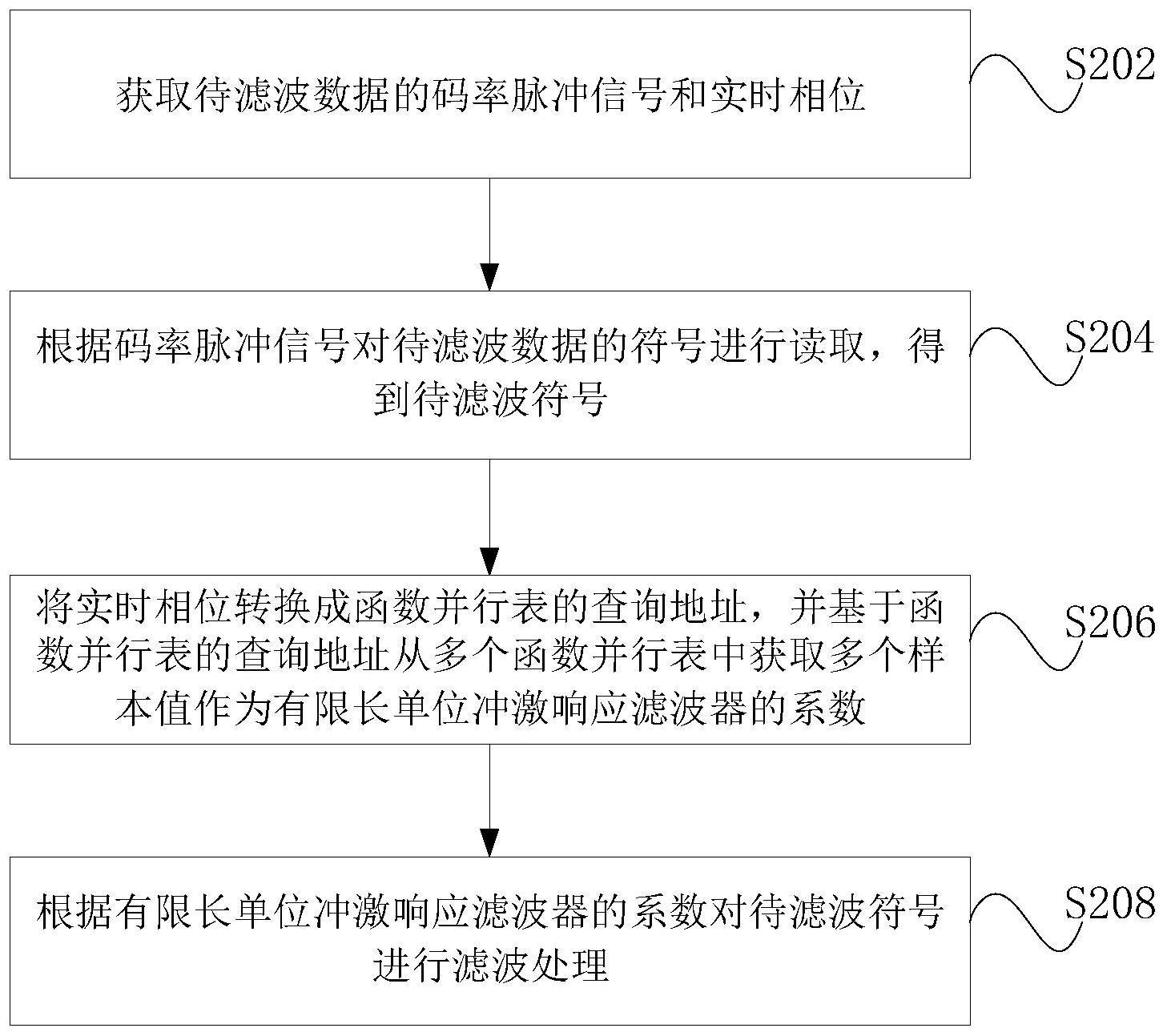

2、根据本技术实施例的一个方面,提供了一种数字成形滤波方法,包括:获取待滤波数据的码率脉冲信号和实时相位;根据所述码率脉冲信号对所述待滤波数据的符号进行读取,得到待滤波符号;将所述实时相位转换成函数并行表的查询地址,并基于所述函数并行表的查询地址从多个函数并行表中获取多个样本值作为有限长单位冲激响应滤波器的系数;根据所述有限长单位冲激响应滤波器的系数对所述待滤波符号进行滤波处理。

3、可选地,所述函数并行表的数量是根据所述有限长单位冲激响应滤波器的跨符号个数确定。

4、可选地,在所述有限长单位冲激响应滤波器的跨符号个数为m时,构建m+1个函数并行表,并将预定数量的样本值按照顺序分别存储到m+1个函数并行表中。

5、可选地,将预定数量的样本值按照顺序分别存储到m+1个函数并行表中,包括:将成形滤波函数以所述有限长单位冲激响应滤波器的跨符号个数m,每个符号的采样点数p进行抽样,获取成形滤波函数的m*p个样本值;将m*p个样本值按照顺序等分成m份,分别存储在前m个函数并行表中,并将第1个函数并行表存储的样本值重复存储在第m+1个函数并行表中。

6、可选地,获取待滤波数据的码率脉冲信号和实时相位,包括:按照码率的频率控制字进行相位累加,当相位溢出时,则循环到下一个相位初始值后继续进行相位累加,同时得到所述待滤波数据的码率脉冲信号和实时相位,其中,所述相位初始值是根据码率的频率相位控制字确定。

7、可选地,所述方法还包括:通过设置相位累加器的位宽,控制相位识别精度和频率控制精度。

8、可选地,在根据所述码率脉冲信号对所述待滤波数据的符号进行读取之前,所述方法还包括:预先缓存所述待滤波数据。

9、根据本技术实施例的另一个方面,还提供了一种数字成形滤波装置,包括:第一处理单元,用于获取待滤波数据的码率脉冲信号和实时相位;第二处理单元,用于根据所述码率脉冲信号对所述待滤波数据的符号进行读取,得到待滤波符号;第三处理单元,用于将所述实时相位转换成函数并行表的查询地址,并基于所述函数并行表的查询地址从多个函数并行表中获取多个样本值作为有限长单位冲激响应滤波器的系数;第四处理单元,用于根据所述有限长单位冲激响应滤波器的系数对所述待滤波符号进行滤波处理。

10、根据本技术实施例的另一个方面,还提供了一种数字成形滤波器,该滤波器包括上述中所述的数字成形滤波装置。

11、根据本技术实施例的另一个方面,还提供了一种电子设备,包括:处理器;用于存储处理器可执行指令的存储器;其中,所述处理器被配置为执行上述中任一项所述的方法步骤。

12、在本技术实施例中,采用获取待滤波数据的码率脉冲信号和实时相位;根据码率脉冲信号对待滤波数据的符号进行读取,得到待滤波符号;将实时相位转换成函数并行表的查询地址,并基于函数并行表的查询地址从多个函数并行表中获取多个样本值作为有限长单位冲激响应滤波器的系数;根据有限长单位冲激响应滤波器的系数对待滤波符号进行滤波处理。也就是说,本技术实施例通过码率脉冲信号读取对待滤波数据中的待滤波符号;同时将实时相位转换成函数并行表的查询地址,以及基于函数并行表的查询地址从多个函数并行表中获取多个样本值作为有限长单位冲激响应滤波器的系数;然后利用有限长单位冲激响应滤波器的系数对该待滤波符号进行滤波处理,进而解决了相关技术中的数字成形滤波方式适应码率范围窄,无法适应符号速率跨度较大的应用场景的技术问题,达到了满足任意采样率下的任意码率成形滤波需求的技术效果。

- 还没有人留言评论。精彩留言会获得点赞!