一种误差放大器输出高低钳位电路

本发明涉及开关电源,具体涉及一种误差放大器输出高低钳位电路。

背景技术:

1、随着近些年计算机和通信领域的飞速发展,人工智能、物联网等快速普及,便携式智能终端产品和通信设备的数量迅速增长,而这些产品与设备都需要开关电源,所以开关电源成为了近几年重要的发展热门之一,而稳定高效的dc-dc变换器对长时间有效维持设备的正常工作至关重要,可以保证设备的安全性,同时在市场竞争中具有一定的优势,所以dc-dc必须要具有足够的稳定性,高效率等优点。

2、在dc-dc电路的设计过程中,误差放大器(ea)的输出通常连接到pwm比较器的负端,而pwm比较器的正端则是电感电流的采样信号和斜坡补偿信号的叠加,然后再与负端的误差放大器的输出进行比较,而pwm比较器的输出便是来控制功率管的关断和续流管的打开。但是如果误差放大器的输出出现了较大的波动,很可能会导致电路功能出现问题,影响了芯片的正常工作,使得芯片的安全性和工作效率大大降低。

3、当负载从轻载变为重载时,输出电压降低,导致vfb电压降低,误差放大器的输出电压升高,输出接到pwm比较器上,使得pwm比较器控制功率管关断时间延迟,这个时候电感的充电时间会增加,使得电感电流变大。但是当电感电流过大时,容易将芯片烧毁。所以需要高钳位电平使得误差放大器的输出不大于此电平,保证电感电流不会因为过大而对芯片造成损坏。

4、当负载从重载变为轻载时,充电时误差放大器输出下降较快,而功率管很快就关闭,电感电流较小,因为放电的时间较短,使得功率管开关次数增加,而开关损耗随之增加,导致工作效率降低。为了能保证dc-dc芯片的高效率,在轻载时可以选择脉冲跳周期调制模式(psm),直到输出电压低于一定值时芯片恢复工作,此时需要低钳位电平,保证使得误差放大器的输出不会低于此电平。

5、目前输出钳位惯用mos管的二极管连接方法,将mos管的漏断接在输出信号上,但是存在很大的问题,不能够精准实现所要求的钳位电压,且线性度差。

技术实现思路

1、针对现有技术中的上述不足,本发明提供的一种误差放大器输出高低钳位电路解决了输出钳位不能够精准实现所要求的钳位电压,且线性度差的问题。

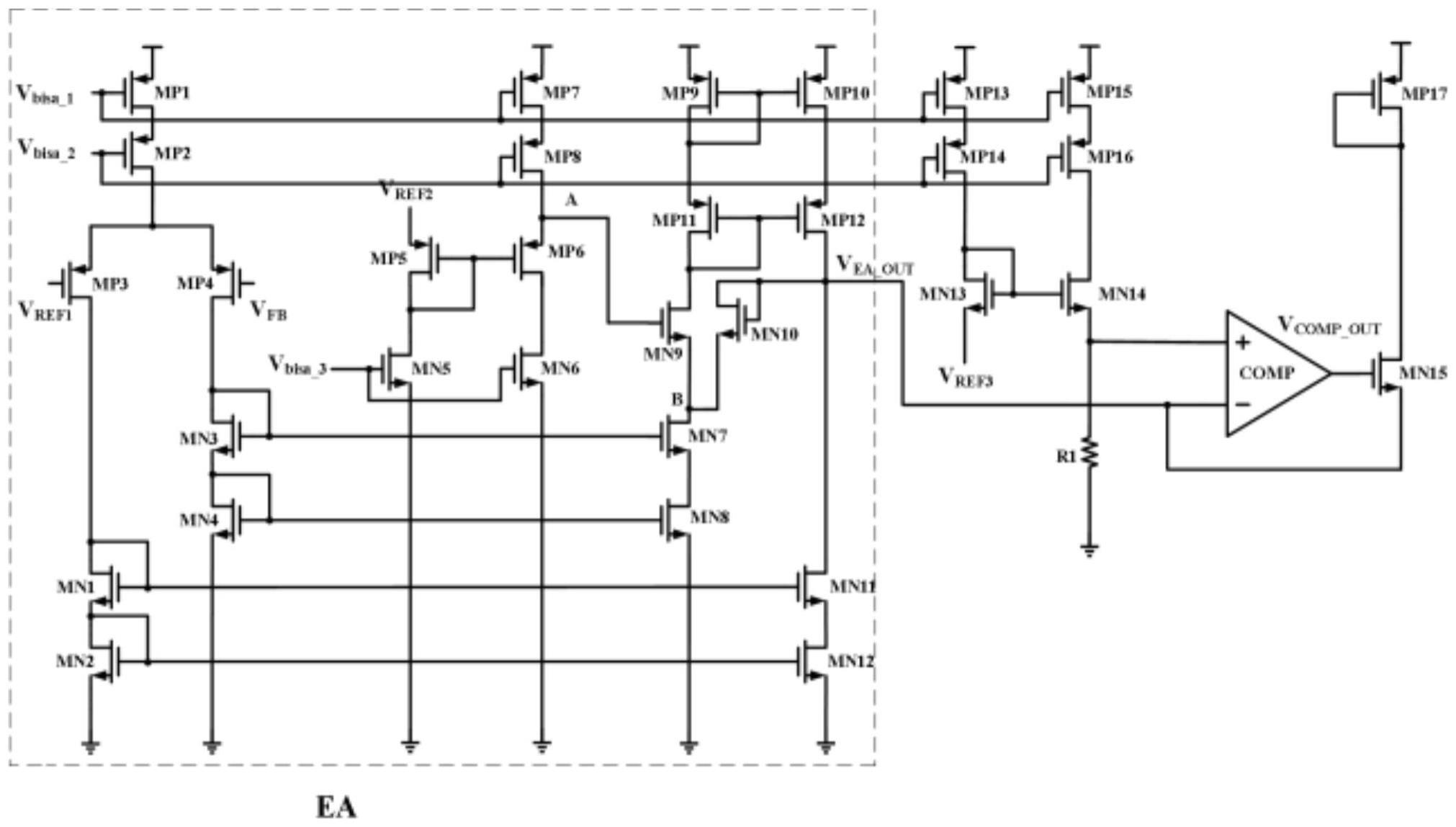

2、为了达到上述发明目的,本发明采用的技术方案为:一种误差放大器输出高低钳位电路,所述电路包括误差放大器ea、比较器comp、pmos管mp13、pmos管mp14、pmos管mp15、pmos管mp16、pmos管mp17、nmos管mn13、nmos管mn14和nmos管mn15,所述误差放大器ea输出电压vea_out与比较器comp输入负端连接,所述比较器comp的输入正端分别与接地电阻r1和nmos管mn14的源极连接,所述nmos管mn14的栅极分别与nmos管mn13的栅极、nmos管mn13的漏极和mos管mp14的漏极连接,所述nmos管mn13的源极与基准电压vref3连接,所述pmos管mp14的栅极与偏置电压vbisa_2连接,其源极与pmos管mp13的漏极连接,所述pmos管mp13的栅极与偏置电压vbisa_1连接,其源极与电源连接,所述nmos管mn14的漏极与pmos管mp16的漏极连接,所述pmos管mp16的栅极与偏置电压vbisa_2连接,其源极与pmos管mp15的漏极连接,所述pmos管mp15的栅极与偏置电压vbisa_1连接,其源极与电源连接,所述比较器comp的输出端vcomp_out与nmos管mn15的栅极连接,所述nmos管mn15的源极与比较器comp的输入负端连接,其漏极分别与pmos管mp17的栅极和pmos管mp17的漏极连接,所述pmos管mp17的源极与电源连接。

3、上述方案的有益效果是:通过上述技术方案,将误差放大器的输出与钳位电压的最小值进行比较,保证了整体环路的稳定性,解决了输出钳位不能够精准实现所要求的钳位电压,且线性度差的问题。

4、进一步地,误差放大器ea包括pmos管mp1、pmos管mp2、pmos管mp3、pmos管mp4、pmos管mp5、pmos管mp6、pmos管mp7、pmos管mp8、pmos管mp9、pmos管mp10、pmos管mp11、pmos管mp12、nmos管mn1、nmos管mn2、nmos管mn3、nmos管mn4、nmos管mn5、nmos管mn6、nmos管mn7、nmos管mn8、nmos管mn9、nmos管mn10、nmos管mn11和nmos管mn12,所述pmos管mp1的栅极与偏置电压vbisa_1连接,其源极与电源连接,其漏极与pmos管mp2的源极连接,所述pmos管mp2的栅极与偏置电压vbisa_2连接,其漏极分别与pmos管mp3的源极和pmos管mp4的源极连接,所述pmos管mp3的栅极与基准电压vref1连接,其漏极分别与nmos管mn1的漏极、nmos管mn1的栅极和nmos管mn11的栅极连接,所述nmos管mn1的源极分别与nmos管mn2的漏极、nmos管mn2的栅极和nmos管mn12的栅极连接,所述nmos管mn2的源极接地,所述pmos管mp4的栅极与dc-dc芯片输出电压的反馈分压vfb连接,其漏极分别与nmos管mn3的漏极、nmos管mn3的栅极和nmos管mn7的栅极连接,所述nmos管mn3的源极分别与nmos管mn4的漏极、nmos管mn4的栅极和nmos管mn8的栅极连接,所述nmos管mn4的源极接地,所述pmos管mp5的源极与基准电压vref2连接,其漏极分别与nmos管mn5的漏极、pmos管mp5的栅极和pmos管mp6的栅极连接,所述nmos管mn5的栅极分别与偏置电压vbisa_3和nmos管mn6的栅极连接,其源极接地,所述nmos管mn6的源极接地,其漏极与pmos管mp6的漏极连接,所述pmos管mp6的源极分别与pmos管mp8的漏极和nmos管mn9的栅极连接,所述pmos管mp8的栅极与偏置电压vbisa_2连接,其源极与pmos管mp7的漏极连接,所述pmos管mp7的栅极与偏置电压vbisa_1连接,其源极与电源连接,所述nmos管mn9的源极分别与nmos管mn7的漏极和nmos管mn10的源极连接,所述nmos管mn7的源极与nmos管mn8的漏极连接,所述nmos管mn8的源极接地,所述nmos管mn9的漏极分别与pmos管mp11的漏极、pmos管mp11的栅极和pmos管mp12的栅极连接,所述pmos管mp11的源极分别与pmos管mp9的漏极、pmos管mp9的栅极和pmos管mp10的栅极连接,所述pmos管mp9的源极与电源连接,所述pmos管mp10的源极与电源连接,其漏极与pmos管mp12的源极连接,所述pmos管mp12的漏极分别与nmos管mn10的漏极、nmos管mn10的栅极和nmos管mn11的漏极连接,所述pmos管mp12的漏极产生误差放大器ea输出电压vea_out,所述nmos管mn11的源极与nmos管mn12的漏极连接,所述nmos管mn12的源极接地。

5、上述进一步方案的有益效果是:通过上述技术方案,实现误差放大器ea的电路结构,误差放大器ea得输出端用于与比较器comp连接。

6、进一步地,比较器comp中包括pmos管mp18、pmos管mp19、pmos管mp20、nmos管mn16、nmos管mn17和nmos管mn18,所述pmos管mp18的栅极与偏置电压vbisa_4连接,其源极与电源连接,其漏极分别与pmos管mp19的源极和pmos管mp20的源极连接,所述pmos管mp19的栅极为比较器comp的输入正端,其漏极分别与nmos管mn16的漏极、nmos管mn16的栅极和nmos管mn17的栅极连接,所述nmos管mn16的源极接地,所述nmos管mn17的源极接地,其漏极分别与pmos管mp20的漏极和nmos管mn18的栅极连接,所述pmos管mp20的栅极作为误差放大器ea输出电压vea_out,所述nmos管mn18的栅极作为比较器comp的输出端vcomp_out,其源极和漏极均接地。

7、上述进一步方案的有益效果是:通过上述技术方案,实现比较器comp的电路结构,用于与误差放大器输出端连接。

8、进一步地,误差放大器ea输出电压vea_out具体包括以下情况:

9、(1)当误差放大器ea输出电压vea_out比nmos管mn10的源极电压高vthn4时,则nmos管mn4导通,误差放大器ea输出电压vea_out电压下降,拉低误差放大器ea的输出,当误差放大器ea输出电压vea_out下降使得nmos管mn10关闭时,则vea_out正常输出;

10、(2)当误差放大器ea输出电压vea_out下降值低于比较器comp的正端电压vref3+vgsn13-vgsn14时,则比较器comp翻转输出高电平,nmos管mn15导通,nmos管mn15的源极电压升高,导致误差放大器ea输出电压vea_out升高,比较器comp输出变回低电平,nmos管mn15关闭,误差放大器ea输出电压vea_out输出正常;

11、其中,vref3为基准电压,vgsn13为nmos管mn13的栅极相对于源极电压,vgsn14为nmos管mn14的栅极相对于源极电压。

12、上述进一步方案的有益效果是:通过上述技术方案,根据所需要的高低钳位电平,设置合适的vref,可以准确做到需要的高低钳位电平。

13、进一步地,电路中的p型mos管和n型mos管的偏置电流和宽长比根据以下公式确定:

14、

15、其中,vgs为mos管栅极相对于源极电压,id为mos管漏极电流,μn为mos管表面电子迁移率,cox为单位面积mos管栅极电容,w为mos管的宽,l为mos管的长,vth为mos管阈值电压。

16、上述进一步方案的有益效果是:根据上式选择mos管合适的偏置电流和宽长比,用于抵消相加相减的vgs,因为电路中vref电压几乎不受温度、电压、工艺的影响,而设置合理的vgs可以相互抵消,所以减小了温度、电压和工艺对电路的影响,提高了精度和准确度。

17、进一步地,比较器comp采用经典五管ota结构,所述nmos管mn16用作电容。

18、上述进一步方案的有益效果是:比较器comp采用经典五管ota结构,面积小,成本低,nmos管mn16用作电容,起到延时的作用。

- 还没有人留言评论。精彩留言会获得点赞!