用于相位插值器的INL检测及校准的制作方法

本公开一般来说涉及用于解决由相位插值器中的非线性引入的误差的方法、系统及设备。

背景技术:

1、通常也称为“相位旋转器”的相位插值器(pi)是实现例如时钟及数据恢复(cdr)、环路时序模式及扩频时钟(ssc)等基本收发器功能的核心组件。收发器性能受到pi中的积分非线性(inl)的影响,这会给所恢复时钟带来抖动。

2、在采用例如脉冲幅度调制4级(pam4)及正交幅度调制16级(qam16)/正交幅度调制64级(qam64)等高级调制的系统中,抖动是重要,所述调制是具有100千兆位及以上速度的链路的主要调制方案。所调制信号的时序及噪声限度明显小于不归零(nrz)信号。对于基于模/数转换器(adc)的具有高级调制的接收器,不准确的采样时钟时序会使adc性能降级。高速输入信号的降级效果变得更大。

3、因此,提供用于inl检测及校准的方法、系统及设备。

技术实现思路

1、在一个方面中,本公开涉及一种方法,其包括:确定相位插值器的输出信号的第一相位,其中所述输出信号是由所述相位插值器基于第一代码来产生的;经由可调整延迟电路来调整具有第二相位的参考信号的延迟,直到所述第二相位与所述第一相位匹配为止,其中所述参考信号的所述延迟可以步长的增量来调整;当所述第二相位与所述第一相位匹配时经由控制逻辑来测量所述参考信号的所述延迟,其中所述延迟是以步长来测量的;至少部分地基于所述延迟来确定所述第一代码下所述相位插值器的积分非线性;及经由所述控制逻辑,至少部分地基于所述积分非线性来校准所述第一代码。

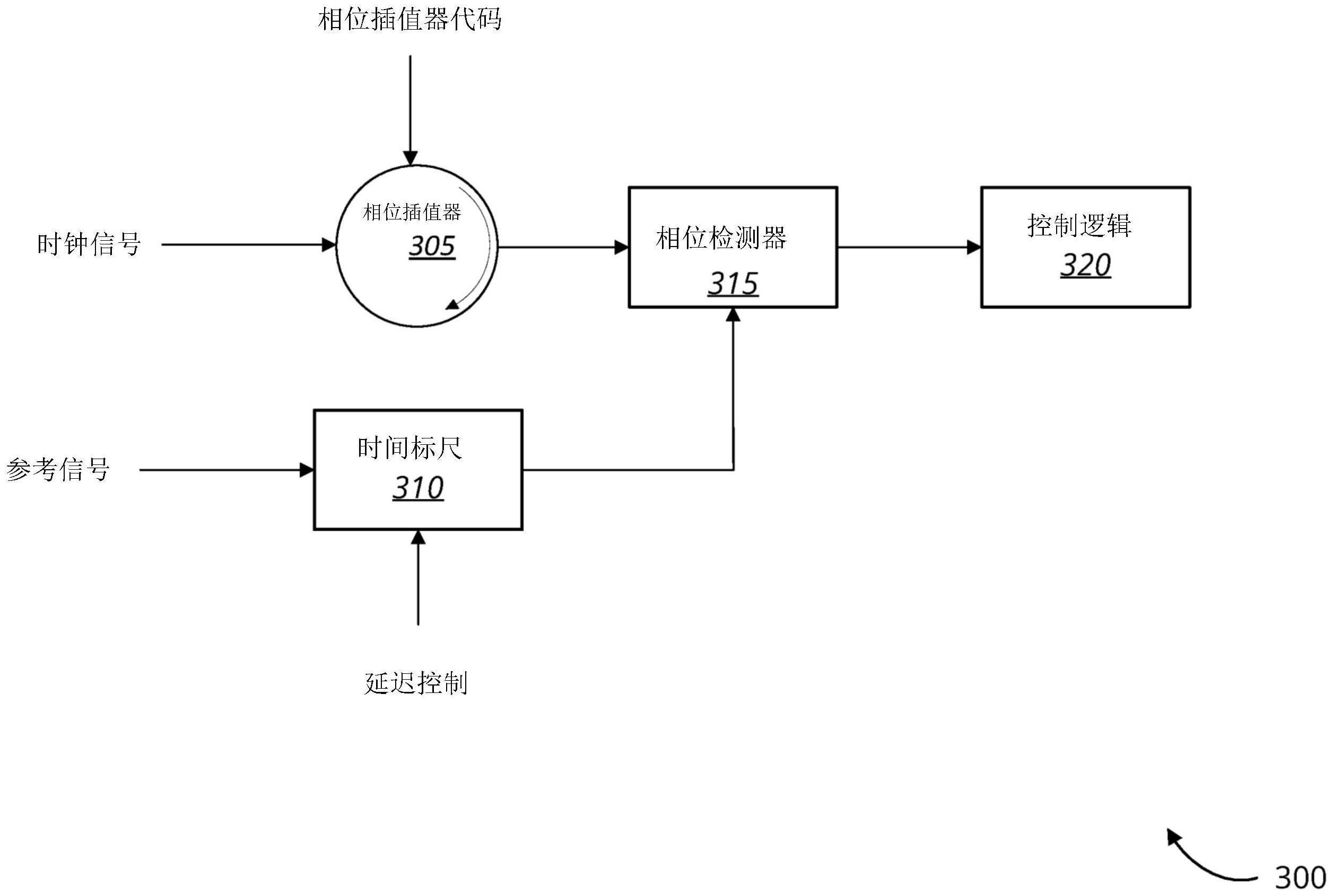

2、在另一方面中,本公开涉及一种电路,其包括:相位检测器电路,其经配置以:确定相位插值器的输出信号的第一相位,其中所述输出信号是由所述相位插值器基于第一代码来产生的;确定参考信号的第二相位;确定所述第一相位相对于所述第二相位的状态,其中所述状态指示所述第一相位是领先于还是滞后于所述第二相位;可调整延迟电路,其耦合到所述相位检测器电路,所述可调整延迟电路经配置以调整所述参考信号的延迟,直到所述第二相位与所述第一相位匹配为止,其中所述参考信号的所述延迟可以步长的增量来调整;控制逻辑,其耦合到所述相位检测器电路及所述可调整延迟电路,所述控制逻辑经配置以:当所述第二相位与所述第一相位匹配时测量所述参考信号的总延迟,其中所述总延迟是以步长来测量的;基于所述总延迟来确定所述第一代码下所述相位插值器的积分非线性;且至少部分地基于所述积分非线性来校准所述第一代码。

3、在又一方面中,本公开涉及一种设备,其包括:控制逻辑,其耦合到相位检测器电路及可调整延迟电路,所述控制逻辑经配置以:经由所述相位检测器电路获得相位插值器的输出信号的第一相位相对于参考信号的第二相位的状态,其中所述状态指示所述第一相位是领先于还是滞后于所述第二相位,其中所述输出信号是由相位插值器基于第一代码来产生的;经由所述可调整延迟电路来调整所述参考信号的延迟,直到所述第二相位与所述第一相位匹配为止,其中所述参考信号的所述延迟可以步长的增量来调整;当所述第二相位与所述第一相位匹配时测量所述参考信号的总延迟,其中所述总延迟是以步长来测量的;基于所述总延迟来确定所述第一代码下所述相位插值器的积分非线性;且至少部分地基于所述积分非线性来校准所述第一代码。

技术特征:

1.一种方法,其包括:

2.根据权利要求1所述的方法,其中确定所述第一代码下所述相位插值器的积分非线性进一步包括:

3.根据权利要求1所述的方法,其中校准所述第一代码进一步包含:

4.根据权利要求3所述的方法,其中所述第二代码是最接近于经调整相位插值器代码的相位插值器代码,其中所述经调整相位插值器代码是基于所述相位差来调整的所述第一代码。

5.根据权利要求1所述的方法,其中所述相位插值器包含一或多个数/模转换器dac单元,每一dac单元对应于相应代码,其中校准所述第一代码进一步包含:

6.根据权利要求1所述的方法,其进一步包括:

7.根据权利要求6所述的方法,其进一步包括:

8.根据权利要求1所述的方法,其进一步包括:

9.一种电路,其包括:

10.根据权利要求9所述的电路,其中所述控制逻辑进一步经配置以将所述总延迟从步长转换成以所述第一代码的最低有效位来测量的相位差,其中所述相位插值器的所述积分非线性是基于所述相位差来确定的。

11.根据权利要求9所述的电路,其中校准所述第一代码进一步包含产生第二代码,其中所述第二代码是通过基于所述相位差调整所述第一代码来产生的,其中所述控制逻辑进一步经配置以将所述第一代码映射到所述第二代码。

12.根据权利要求11所述的电路,其中所述第二代码是最接近于经调整相位插值器代码的相位插值器代码,其中所述经调整相位插值器代码是基于所述相位差来调整的所述第一代码。

13.根据权利要求9所述的电路,其中所述控制逻辑进一步经配置以基于所述相位差来调整所述相位插值器的至少一个数/模dac单元的权重,其中所述相位插值器包含一或多个dac单元,每一dac单元对应于相应代码。

14.根据权利要求9所述的电路,其中测量所述总延迟进一步包含当所述第一相位相对于所述第二相位的所述状态发生转变时测量所述总延迟,其中所述转变是所述第一相位相对于所述第二相位的所述状态的改变。

15.一种设备,其包含:

16.根据权利要求15所述的设备,其中所述控制逻辑进一步经配置以将所述总延迟从步长转换成以所述第一代码的最低有效位来测量的相位差,其中基于所述相位差来确定所述相位插值器的所述积分非线性。

17.根据权利要求15所述的设备,其中校准所述第一代码进一步包含产生第二代码,其中所述第二代码是通过基于所述相位差调整所述第一代码来产生的,其中所述控制逻辑进一步经配置以将所述第一代码映射到所述第二代码。

18.根据权利要求17所述的设备,其中所述第二代码是最接近于经调整相位插值器代码的相位插值器代码,其中所述经调整相位插值器代码是基于所述相位差来调整的所述第一代码。

19.根据权利要求15所述的设备,其中所述控制逻辑进一步经配置以基于所述相位差来调整所述相位插值器的至少一个数/模dac单元的权重,其中所述相位插值器包含一或多个dac单元,每一dac单元对应于相应代码。

20.根据权利要求15所述的设备,其中测量所述总延迟进一步包含当所述第一相位相对于所述第二相位的所述状态发生转变时测量所述总延迟,其中所述转变是所述第一相位相对于所述第二相位的所述状态的改变。

技术总结

本公开涉及用于相位插值器的INL检测及校准。一种设备包含耦合到相位检测器电路及可调整延迟电路的控制逻辑。所述控制逻辑经配置以获得相位插值器的输出信号的第一相位相对于参考信号的第二相位的状态,并调整所述参考信号的延迟,直到所述第二相位与所述第一相位匹配为止。所述控制逻辑进一步经配置以当所述第二相位与所述第一相位匹配时测量所述参考信号的总延迟,并基于所述总延迟来确定第一代码下所述相位插值器的积分非线性。所述控制逻辑可进一步至少部分地基于所述积分非线性来校准相位插值器的第一代码。

技术研发人员:S-H·李,S·钟,全亨俊,V·米利鲁德,W·张,A·唐

受保护的技术使用者:安华高科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!