一种用于高压功率芯片端口控制的迟滞电路的制作方法

本技术涉及芯片,尤其是涉及一种用于高压功率芯片端口控制的迟滞电路。

背景技术:

1、在芯片外部端口上,经常会出现一些使能控制端口,用于对芯片进行功能控制,例如:使能控制端口可以控制芯片处于工作状态还是非工作状态。

2、在低电压(例如,供电电压在:1.8v,3.3v,5v)类芯片领域,这种使能控制端口可以借助io的三态门,完成对输入电平信号的高电平(大于90%*vcc)、低电平(小于10%*vcc)、浮空电平(芯片内部有上拉电阻或下拉电阻)的处理,从器件使用的角度讲,低电压类芯片领域的晶体管的驱动电压ugs(栅极源极之间电压差)与控制电压uds接近,可以实现驱动电压与控制电压的逐级传递,相对容易。

3、但在高电压(例如供电电压为上百伏)类(高压功率)芯片领域,由于晶体管的栅源电压不能做到很高,因此,当供电电压远高于晶体管的驱动电压时,直接接入高电平对芯片的使能控制端口进行控制,极易导致晶体管损坏。并且,在高电压类芯片领域,使能控制端口若直接接入浮空电平或者负电平(输入电平低于接地电平),则可能会导致芯片漏电。因此,现有技术中急需一种能够同时适应多种输入电平(即包括高电平、负电平、接地电平、低电平、浮空电平)的高压功率芯片端口。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种用于高压功率芯片端口控制的迟滞电路,以适应多种输入电平,使用方便,提高高压功率芯片端口的可靠性和运行稳定性。

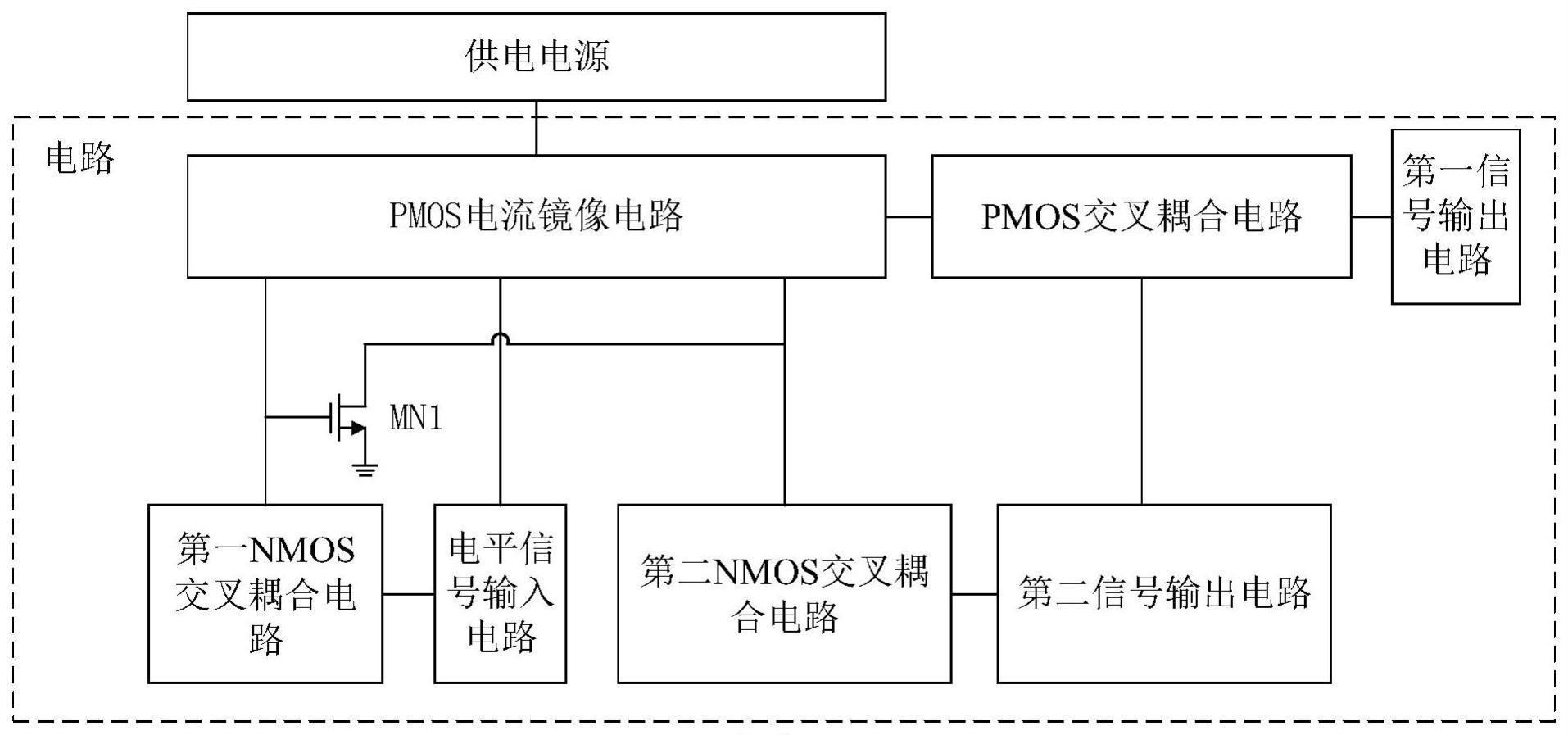

2、第一方面,本技术实施例提供了一种用于高压功率芯片端口控制的迟滞电路,所述迟滞电路应用于高压功率芯片端口,所述迟滞电路包括:电平信号输入电路、第一nmos交叉耦合电路、第一nmos晶体管、pmos电流镜像电路、pmos交叉耦合电路、第一信号输出电路、第二信号输出电路、第二nmos交叉耦合电路;

3、所述电平信号输入电路分别连接所述第一nmos交叉耦合电路和所述pmos电流镜像电路;所述第一nmos晶体管的栅极分别连接所述第一nmos交叉耦合电路和所述pmos电流镜像电路;所述第一nmos晶体管的漏极分别连接所述pmos电流镜像电路、所述第二nmos交叉耦合电路;所述第一nmos晶体管的源极与地连接;所述第二nmos交叉耦合电路分别连接所述pmos电流镜像电路、所述第二信号输出电路;所述pmos交叉耦合电路分别连接所述pmos电流镜像电路、所述第一信号输出电路、所述第二信号输出电路;所述pmos电流镜像电路连接供电电源。

4、结合第一方面,本技术实施例提供了第一方面的第一种可能的实施方式,其中,所述电平信号输入电路包括:电阻、二极管和电平信号输入端;所述电阻的一端连接所述电平信号输入端,另一端连接所述二极管的负极,所述二极管的正极与地连接。

5、结合第一方面的第一种可能的实施方式,本技术实施例提供了第一方面的第二种可能的实施方式,其中,所述第一nmos交叉耦合电路包括:第二nmos晶体管、第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第六nmos晶体管、第七nmos晶体管;

6、所述第二nmos晶体管的漏极分别连接所述二极管的负极、所述电阻的另一端、所述第二nmos晶体管的栅极以及所述第五nmos晶体管的漏极;所述第二nmos晶体管的源极分别连接所述第三nmos晶体管的漏极、所述第三nmos晶体管的栅极以及所述第四nmos晶体管的栅极;所述第二nmos晶体管的栅极分别连接所述二极管的负极、所述电阻的另一端以及所述第五nmos晶体管的漏极;

7、所述第三nmos晶体管的源极与地链接;所述第三nmos晶体管的栅极分别连接所述第三nmos晶体管的漏极和所述第四nmos晶体管的栅极;所述第三nmos晶体管的漏极还连接所述第四nmos晶体管的栅极;

8、所述第四nmos晶体管的漏极分别连接所述第七nmos晶体管的栅极、所述第七nmos晶体管的漏极以及所述第一nmos晶体管的栅极;所述第四nmos晶体管的源极与地链接;

9、所述第五nmos晶体管的源极与地链接;所述第五nmos晶体管的漏极还分别连接所述二极管的负极、所述电阻的另一端;所述第五nmos晶体管的栅极分别连接所述第六nmos晶体管的栅极、所述第六nmos晶体管的漏极以及所述第七nmos晶体管的源极;

10、所述第六nmos晶体管的栅极分别连接所述第六nmos晶体管的漏极和所述第七nmos晶体管的源极;所述第六nmos晶体管的源极与地链接;所述第六nmos晶体管的漏极还连接所述第七nmos晶体管的源极;

11、所述第七nmos晶体管的漏极分别连接所述第七nmos晶体管的栅极、所述第一nmos晶体管的栅极和所述pmos电流镜像电路;

12、所述第三nmos晶体管、所述第四nmos晶体管、所述第五nmos晶体管和所述第六nmos晶体管之间的长度比为1:1:2:1。

13、结合第一方面,本技术实施例提供了第一方面的第三种可能的实施方式,其中,所述pmos电流镜像电路包括:第一pmos晶体管、第二pmos晶体管、第三pmos晶体管、第四pmos晶体管和第五pmos晶体管;所述第一pmos晶体管的源极、所述第二pmos晶体管的源极、所述第三pmos晶体管的源极、所述第四pmos晶体管的源极和所述第五pmos晶体管的源极共同连接所述供电电源以及所述pmos交叉耦合电路;

14、所述第一pmos晶体管的栅极、所述第二pmos晶体管的栅极、所述第三pmos晶体管的栅极、所述第四pmos晶体管的栅极和所述第五pmos晶体管的栅极之间顺序连接;

15、所述第一pmos晶体管的漏极分别连接所述第一pmos晶体管的栅极和所述第二pmos晶体管的栅极;所述第二pmos晶体管的漏极分别连接所述第一nmos晶体管的栅极和所述第一nmos交叉耦合电路;所述第三pmos晶体管的漏极分别连接所述第一nmos交叉耦合电路和所述电平信号输入电路;所述第四pmos晶体管的漏极分别连接所述第一nmos晶体管的漏极和所述第二nmos交叉耦合电路;所述第五pmos晶体管的漏极连接所述第二nmos交叉耦合电路。

16、结合第一方面,本技术实施例提供了第一方面的第四种可能的实施方式,其中,所述pmos交叉耦合电路包括:第六pmos晶体管、第七pmos晶体管、第八pmos晶体管、第九pmos晶体管、第十pmos晶体管、第十一pmos晶体管;

17、所述第六pmos晶体管的源极、所述第七pmos晶体管的源极、所述第八pmos晶体管的源极、所述第九pmos晶体管的源极依次连接,且共同连接所述pmos电流镜像电路;

18、所述第六pmos晶体管的漏极分别连接所述第六pmos晶体管的栅极、所述第七pmos晶体管的栅极和所述第十一pmos晶体管的源极;

19、所述第七pmos晶体管的漏极分别连接所述第十pmos晶体管的栅极、所述第十pmos晶体管的漏极和所述第二信号输出电路;

20、所述第八pmos晶体管的漏极分别连接所述第十一pmos晶体管的栅极、所述第十一pmos晶体管的漏极和所述第一信号输出电路;所述第八pmos晶体管的栅极连接所述第九pmos晶体管的栅极;

21、所述第九pmos晶体管的漏极分别连接所述第九pmos晶体管的栅极和所述第八pmos晶体管的栅极;所述第九pmos晶体管的源极连接所述第一信号输出电路;

22、所述第十pmos晶体管的源极分别连接所述第九pmos晶体管的漏极、所述第九pmos晶体管的栅极、所述第八pmos晶体管的栅极;所述第十pmos晶体管的漏极分别连接所述第十pmos晶体管的栅极、所述第二信号输出电路;

23、所述第十一pmos晶体管的源极还分别连接所述第六pmos晶体管的栅极和第七pmos晶体管的栅极;所述第十一pmos晶体管的栅极分别连接所述第十一pmos晶体管的漏极、所述第一信号输出电路;所述第十一pmos晶体管的漏极还分别连接所述第一信号输出电路和第二信号输出电路。

24、结合第一方面的第四种可能的实施方式,本技术实施例提供了第一方面的第五种可能的实施方式,其中,所述第一信号输出电路包括第一信号输出端和第十二pmos晶体管;所述第十二pmos晶体管的栅极分别连接所述第十一pmos晶体管的漏极、所述第十一pmos晶体管的栅极、所述第八pmos晶体管的漏极、所述第二信号输出电路;所述第十二pmos晶体管的源极连接所述第九pmos晶体管的源极;所述第十二pmos晶体管的漏极连接所述第一信号输出端。

25、结合第一方面的第三种可能的实施方式,本技术实施例提供了第一方面的第六种可能的实施方式,其中,所述第二nmos交叉耦合电路包括:第八nmos晶体管、第九nmos晶体管、第十nmos晶体管、第十一nmos晶体管、第十二nmos晶体管、第十三nmos晶体管;

26、所述第八nmos晶体管的漏极分别连接所述第一nmos晶体管的漏极、所述第四pmos晶体管的漏极、所述第八nmos晶体管的栅极、所述十一nmos晶体管的漏极和所述第二信号输出电路;所述第八nmos晶体管的栅极连接所述第十一nmos晶体管的漏极;所述第八nmos晶体管的源极分别连接所述第九nmos晶体管的漏极、所述第九nmos晶体管的栅极、所述第十nmos晶体管的栅极;

27、所述第九nmos晶体管的源极与地链接;所述第九nmos晶体管的栅极连接所述第十nmos晶体管的栅极;

28、所述第十nmos晶体管的源极与地链接;所述第十nmos晶体管的漏极分别连接所述第十三nmos晶体管的栅极、所述第十三nmos晶体管的漏极和所述第五pmos晶体管的漏极;

29、所述第十一nmos晶体管的源极与地链接;所述第十一nmos晶体管的漏极分别连接所述第八nmos晶体管的漏极、所述第四pmos晶体管的漏极和所述第一nmos晶体管的漏极;所述第十一nmos晶体管的栅极分别连接所述第十二nmos晶体管的栅极、所述第十二nmos晶体管的漏极和所述第十三nmos晶体管的源极;

30、所述第十二nmos晶体管的栅极还分别连接所述第十二nmos晶体管的漏极、所述第十三nmos晶体管的源极;所述第十二nmos晶体管的源极与地链接;所述第十二nmos晶体管的漏极连接所述第十三nmos晶体管的源极;

31、所述第十三nmos晶体管的漏极还分别连接所述第十三nmos晶体管的栅极、所述第五pmos晶体管的漏极;所述第十三nmos晶体管的栅极还分别连接所述第五pmos晶体管的漏极和所述第二信号输出电路;

32、所述第九nmos晶体管、所述第十nmos晶体管、所述第十一nmos晶体管和所述第十二nmos晶体管之间的长度比为1:1:1:1。

33、结合第一方面的第六种可能的实施方式,本技术实施例提供了第一方面的第七种可能的实施方式,其中,所述第二信号输出电路包括:第十四nmos晶体管、第十五nmos晶体管、第十六nmos晶体管、第二信号输出端、第十七nmos晶体管和第十八nmos晶体管;所述第十四nmos晶体管的栅极分别连接所述第十三nmos晶体管的栅极和所述第十五nmos晶体管的栅极;所述第十四nmos晶体管的源极与地链接;所述第十四nmos晶体管的漏极连接第二信号输出端;

34、所述第十五nmos晶体管的漏极连接所述pmos交叉耦合电路;所述第十五nmos晶体管的源极连接所述第十六nmos晶体管的漏极;所述第十六nmos晶体管的源极与地链接;所述第十六nmos晶体管的栅极连接所述第十八nmos晶体管的栅极;所述第十七nmos晶体管的漏极连接所述pmos交叉耦合电路;所述第十七nmos晶体管的栅极连接所述第八nmos晶体管的漏极;所述第十七nmos晶体管的源极连接所述第十八nmos晶体管的漏极;所述第十八nmos晶体管的源极与地链接。

35、结合第一方面,本技术实施例提供了第一方面的第八种可能的实施方式,其中,所述电平信号输入电路中输入的电平信号包括以下中的任意一种或多种:高电平、低电平、接地电平、浮空电平以及负电平。

36、本技术实施例提供的一种用于高压功率芯片端口控制的迟滞电路,该迟滞电路应用于高压功率芯片端口,该迟滞电路包括:电平信号输入电路、第一nmos交叉耦合电路、第一nmos晶体管、pmos电流镜像电路、pmos交叉耦合电路、第一信号输出电路、第二信号输出电路、第二nmos交叉耦合电路;电平信号输入电路分别连接第一nmos交叉耦合电路和pmos电流镜像电路;第一nmos晶体管的栅极分别连接第一nmos交叉耦合电路和pmos电流镜像电路;第一nmos晶体管的漏极分别连接pmos电流镜像电路、第二nmos交叉耦合电路;第一nmos晶体管的源极与地连接;第二nmos交叉耦合电路分别连接pmos电流镜像电路、第二信号输出电路;pmos交叉耦合电路分别连接pmos电流镜像电路、第一信号输出电路、第二信号输出电路;pmos电流镜像电路连接供电电源。该电路允许外部输入信号以:高电平、负电平、接地电平、低电平、浮空电平中的任意情形对芯片端口进行控制,使用方便,有利于提高高压功率芯片端口控制的可靠性和运行稳定性。

37、为使本技术的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

- 还没有人留言评论。精彩留言会获得点赞!