一种基于钟控电荷泵的高精度差分电路的制作方法

本发明涉及模拟集成电路,特别涉及一种基于钟控电荷泵的高精度差分电路。

背景技术:

1、随着现代电子技术的飞速发展,不同的电子系统对模数转换器的需求也越来越多:模数转换器能将连续模拟信号转化为离散的数字信号,在电子系统中扮演着重要的角色。

2、在流水线模数转换器系统设计中,提供基准电压的参考源的精度、稳定性、建立时间和噪声等指标会直接影响整个流水线模数转换器系统的性能。由于传统基准电压源的驱动能力是有限的,直接驱动流水线负载很难保证参考电压的稳定,所以需要片内产生基准电压并增加缓冲电路来提供稳定的参考电压。

3、参考电压源的实现形式多样,有输出单端参考电压和输出差分参考电压形式之分。由于差分结构相对单端结构有很多优势,目前流水线模数转换器系统多采用差分参考电压源,同时提供给mdac(乘法dac,(multiplyingdac)和subadc(子模数转化器)。subadc中噪声会通过电压源来影响mdac,所以高速流水线模数转换器系统对电压精度的要求非常高,并且高速流水线模数转换器系统需要参考电压源具有较强的驱动能力。

技术实现思路

1、本发明的目的在于提供一种基于钟控电荷泵的高精度差分电路,以满足流水线模数转换器系统中差分参考电压的需求。

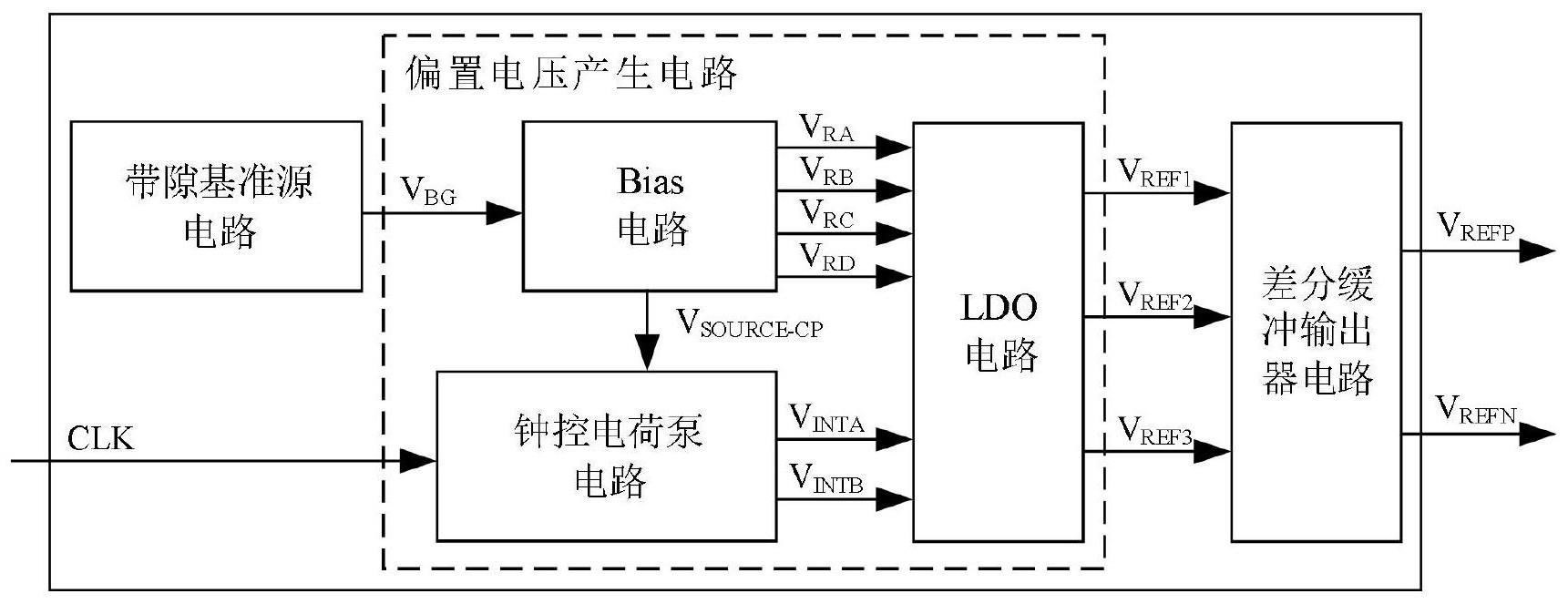

2、为解决上述技术问题,本发明提供了一种基于钟控电荷泵的高精度差分电路,应用于流水线模数转换器系统中,包括带隙基准源电路、偏置电压产生电路和差分缓冲输出器电路;

3、所述带隙基准源电路由两个相互匹配的基准电路构成,两个基准电路的输出共同产生带隙基准电压vbg;

4、所述偏置电压产生电路包括bias电路、钟控电荷泵电路和ldo电路;其中,

5、所述bias电路包括内部ldo模块、vr参考电压电路和vsource参考电压电路;所述内部ldo模块根据带隙基准电压vbg产生所述vr参考电压电路所需的电压;所述vr参考电压电路产生参考电压vra、vrb、vrc、vrd;所述vsource参考电压电路产生稳定的电源信号vsource_cp;

6、所述钟控电荷泵电路根据输入的电源信号vsource_cp产生电压信号vinta和vintb;

7、所述ldo电路包括三个小ldo电路和一个双支路反馈电路,三个小ldo电路分别产生三个稳定的参考电压vref1、vref2、vref3;所述双支路反馈电路产生三个小ldo电路所需要的反馈信号vt1、vt2、vt3;

8、所述差分缓冲输出器电路根据三个稳定的参考电压vref1、vref2、vref3产生稳定的差分参考电压vrefp和vrefn,供流水线模数转换器系统使用。

9、在一种实施方式中,单个所述基准电路包括bg核心电路以及曲率补偿电路;所述bg核心电路包括pmos管一、pmos管二、pmos管四、nmos管一、nmos管二、电阻一、电阻四、三极管一~三极管三;所述曲率补偿电路包括pmos管三、nmos管五、电阻二和电阻三;

10、pmos管一~pmos管四的栅极互连、源极共同接电源vdd,pmos管一的漏极连接nmos管一的漏极,pmos管二的漏极连接nmos管二的漏极,nmos管一的栅极同时连接自身漏极和nmos管二的栅极;nmos管一的源极连接三极管一的发射极,nmos管二的源极通过电阻一连接三极管二的发射极;

11、pmos管三的漏极通过电阻二连接电阻三的第一端,pmos管四的漏极通过电阻四连接三极管三的发射极;nmos管五的栅极连接电阻三的第一端,漏极连接三极管二的发射极,源极与三极管一的集电极、三极管二的集电极、电阻三的第二端、三极管三的基极和集电极共同接地。

12、在一种实施方式中,所述三极管一和所述三极管二均为双极型晶体管,两者的个数比值为1:8。

13、在一种实施方式中,所述内部ldo模块包括运放器一、pmos管九~pmos管十二、nmos管七、nmos管八,电阻九、电阻十;所述vr参考电压电路包括pmos管十三~pmos管二十、pmos管三十,nmos管九、nmos管十,电阻十一~电阻十四以及电容一、电容二;所述vsource参考电压电路包括pmos管二十一~pmos管二十九,nmos管十一~nmos管十七以及电容三、电容四;

14、pmos管九、pmos管十一、pmos管十三、pmos管十五、pmos管十七和pmos管十九的源极均接电源vdd,栅极均接运放器一的输出端,运放器一的负输入端输入带隙基准电压vbg;pmos管九的漏极接nmos管七的漏极,pmos管十的源极接电源vdd,漏极同时接自身栅极和nmos管八的漏极,nmos管七的漏极同时接自身栅极和nmos管八的栅极,nmos管七和nmos管八的源极均接地;

15、pmos管十二、pmos管十四、pmos管十六、pmos管十八和pmos管二十的源极分别连接pmos管十一、pmos管十三、pmos管十五、pmos管十七和pmos管十九的漏极,pmos管十二、pmos管十四、pmos管十六、pmos管十八和pmos管二十的栅极共同连接pmos管十的栅极;pmos管十二的漏极依次通过电阻九和电阻十接地,运放器一的正输入端接在电阻九和电阻十之间;pmos管十四和pmos管十六的漏极分别通过电阻十一和电阻十二连接电阻十三的第一端,电阻十三的第二端通过电阻十四接地,电容一的一端接电阻十三的第一端,另一端接地;电容二的一端接电阻十三的第二端,另一端接地;pmos管三十的源极接pmos管十八的漏极,栅极接电阻十三的第二端,漏极接地;nmos管九的漏极同时接自身栅极和pmos管二十的漏极,nmos管十的漏极同时接自身栅极和nmos管九的源极,nmos管十的源极接地;

16、pmos管二十一、pmos管二十三、pmos管二十五、pmos管二十七的源极均接电源vdd,漏极分别连接pmos管二十二、pmos管二十四、pmos管二十六、pmos管二十八的源极;pmos管二十二、pmos管二十四、pmos管二十六、pmos管二十八的栅极共同连接至pmos管二十一的栅极和pmos管二十二的漏极;pmos管二十三、pmos管二十五、pmos管二十七的栅极共同连接pmos管二十四的漏极;

17、pmos管二十二、pmos管二十四和pmos管二十六的漏极分别连接nmos管十一、nmos管十三和nmos管十五的漏极,nmos管九、nmos管十一、nmos管十三的栅极互连;nmos管十一、nmos管十三的源极分别连接nmos管十二、nmos管十四的漏极,nmos管十、nmos管十二、nmos管十四的栅极互连;

18、pmos管二十九的源极连接pmos管二十八的漏极,栅极连接pmos管三十的栅极,漏极同时连接nmos管十六的漏极和nmos管十七的栅极,nmos管十六的栅极同时连接nmos管十五的栅极和漏极;nmos管十七的栅极通过电容三连接pmos管二十九的源极,漏极连接pmos管二十九的源极,漏极和源极直接连接电容四;nmos管十二、nmos管十四~nmos管十七的源极均接地。

19、在一种实施方式中,所述钟控电荷泵电路包括两组相同的钟控电路和电荷泵电路,每组分别产生电压信号vinta和vintb;

20、单个钟控电路包括反相器一~反相器四、缓冲器一和缓冲器二;其中反相器一~反相器四依次串联,缓冲器一的输入端连接在反相器一和反相器二之间,缓冲器二的输入端连接在反相器三和反相器四之间;

21、单个电荷泵电路包括nmos管十八~nmos管二十五、pmos管三十一、pmos管三十二以及电容五~电容十;nmos管十八的漏极同时连接自身栅极和nmos管二十的漏极,源极通过电容五接反相器二的输出端;nmos管二十的源极同时接电容六的第一端和nmos管二十二的栅极,栅极同时接nmos管十八的源极和nmos管二十一的栅极;nmos管二十一的漏极接nmos管二十的漏极,源极接电容七的第二端;电容六的第二端和电容七的第一端共同接缓冲器一的输出端;nmos管二十二的漏极同时接pmos管三十一的源极和电容七的第二端,源极接pmos管三十一的漏极;

22、nmos管十九的漏极同时连接自身栅极和nmos管二十四的漏极,源极通过电容八接反相器四的输出端;nmos管二十五的源极同时接电容十的第一端和nmos管二十三的栅极,栅极同时接nmos管十九的源极和nmos管二十四的栅极;nmos管二十四的漏极接nmos管二十五的漏极,源极接电容九的第二端;电容十的第二端和电容九的第一端共同接缓冲器二的输出端;nmos管二十三的漏极同时接pmos管三十二的源极和电容九的第二端,源极接pmos管三十二的漏极;

23、pmos管三十一的栅极接nmos管二十三的栅极,pmos管三十二的栅极接nmos管二十二的栅极;pmos管三十一的漏极和pmos管三十二的漏极共同输出电压信号。

24、在一种实施方式中,所述三个小ldo电路为小ldo电路一、小ldo电路二、小ldo电路三;

25、小ldo电路一包括运放器二、pmos管三十三、pmos管三十四、nmos管二十六、nmos管二十七、电容十一~电容十三以及电阻十五,小ldo电路二包括运放器三、pmos管三十五、nmos管二十九~nmos管三十一、电容十四~电容十六以及电阻十七,小ldo电路三包括运放器四、nmos管三十三~nmos管三十五,双支路反馈电路包括pmos管三十六、nmos管二十八、nmos管三十二以及电阻十六、电阻十八~电阻二十一;

26、pmos管三十四的栅极接运放器二的输出端,源极接pmos管三十三的漏极和栅极,漏极接nmos管二十六的漏极和nmos管二十七的栅极;电容十一的第一端接pmos管三十三的源极,第二端接nmos管二十七的栅极;nmos管二十七的漏极接电容十一的第一端,源极接地;电容十二的第一端同时接nmos管二十七的漏极和电阻十五的第一端,电容十三的第一端同时接电阻十五的第二端和nmos管二十八的栅极,电容十二和电容十三的第二端均接nmos管二十六的源极;

27、pmos管三十五的栅极接运放器三的输出端,源极接nmos管二十九的源极,漏极接nmos管三十一的漏极和nmos管三十的栅极;电容十四的第一端接nmos管二十九的栅极,第二端接nmos管三十的栅极;nmos管三十的漏极接电容十四的第一端,源极接地;电容十五的第一端同时接nmos管三十的漏极和电阻十七的第一端,电容十六的第一端同时接电阻十七的第二端和nmos管三十二的栅极,电容十五和电容十六的第二端均接nmos管三十一的源极;

28、nmos管三十四的栅极接运放器四的输出端,源极同时接nmos管三十五的漏极和pmos管三十六的栅极,漏极接nmos管三十三的源极;nmos管三十三的漏极接电源vdd,nmos管三十五的源极接地;

29、nmos管二十八的漏极通过电阻十六接电源vdd,源极同时接电阻十八的第一端和nmos管三十二的漏极,电阻十八的第二端同时接运放器二的负输入端和电阻十九的第一端;nmos管三十二的源极接电阻二十的第一端,电阻二十的第二端同时接运放器三的负输入端和电阻二十一的第一端,电阻二十一的第二端同时接运放器四的负输入端和pmos管三十六的源极,pmos管三十六的漏极和电阻十九的第二端均接地。

30、在一种实施方式中,运放器二和运放器三的正输入端均接电阻十三的第一端,运放器四的正输入端接pmos管三十的栅极,nmos管二十六、nmos管三十一和nmos管三十五的栅极均接nmos管十的栅极,nmos管三十三的栅极接pmos管三十的源极。

31、在一种实施方式中,所述差分缓冲输出器电路包括pmos管三十七、nmos管三十六、nmos管三十七以及电阻二十二、电阻二十三;

32、nmos管三十六的漏极通过电阻二十二接电源vdd,栅极接nmos管二十八的栅极,源极接nmos管三十七的漏极;nmos管三十七的栅极接nmos管三十二的栅极,源极通过电阻二十三接pmos管三十七的源极;pmos管三十七的栅极接pmos管三十六的栅极,漏极接地。

33、本发明提供的一种基于钟控电荷泵的高精度差分电路,应用于流水线模数转换器系统,包括带隙基准源电路、偏置电压产生电路和差分缓冲输出器电路。带隙基准源电路由两个相互匹配的基准电路构成,两个基准电路的输出共同产生带隙基准电压vbg,有更强的环境适应能力,且有更好的温度系数和更高精度;偏置电压产生电路根据带隙基准电压vbg产生稳定的三个参考电压;差分缓冲输出器电路根据三个参考电压产生稳定的差分参考电压,供流水线模数转换器系统使用。本发明结构简单,驱动力强,能为高速高精度模数转换器系统提供稳定的差分参考电压,提高了电压源应用的灵活性。

- 还没有人留言评论。精彩留言会获得点赞!