一种时钟同步电路及方法与流程

本发明属于短波无线通信频率合成,具体涉及一种时钟同步电路及方法。

背景技术:

1、短波电台是一种无线电通信设备,主要用于传送话音、等幅报和移频报等。在传送电话信号时,采用振幅调制和单边带调制。由发信机、收信机、天线、电源和终端设备等组成。一般分为便携式、车载式和固定式电台,在通信中占有重要地位,但是短波通信容量小,传播信道不稳定,传输可靠性较低。为提高短波通信的可靠性,采取了实时选频、分集接收、电报终端采用时频编码和差错控制、电话终端采用压缩扩展设备等措施;为提高抗干扰能力,采用了跳频等技术。跳频电台是按全网预设的程序,自动操控网内所有台站在一秒钟内同步改变频率多次,并在每个跳频信道上短暂停留。周期性的同步信令从主站发出,指令所有的从站同时跳跃式更换工作频率。跳频电台的目的是增强抗干扰能力和通信隐蔽性,是电子对抗技术发展的产物。因此在短波数字化跳频电台中,当使用两个标称频率一样的恒温晶体振荡器时,由于频率及相位有差异,导致电台数据通信时出现掉数据、噪声变差等现象。

技术实现思路

1、为了解决现有技术中的问题,本发明提供了一种时钟同步电路及方法,将两个恒温晶体振荡器相位和频率同步,解决了电台数据通信中出现的掉数据和噪声差的问题。

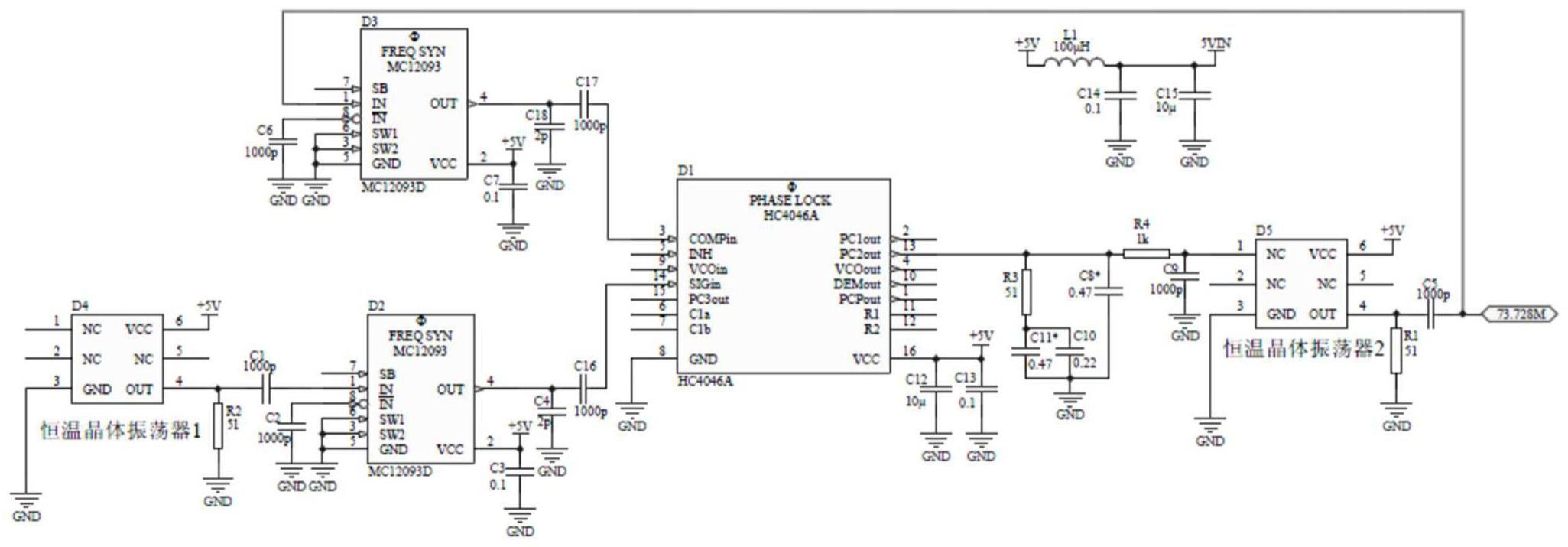

2、为了实现以上目的,本发明提供了一种时钟同步电路,包括两个恒温晶体振荡器d4和d5、两个分频器d2和d3,及一个锁相环芯片d1,所述恒温晶体振荡器d4的输出端经过所述分频器d2连接所述锁相环芯片d1的参考输入端,所述锁相环芯片d1具有鉴相器和电荷泵,所述锁相环芯片d1的输出端连接所述恒温晶体振荡器d5的nc端,所述恒温晶体振荡器d5的输出端经所述分频器d3连接所述锁相环芯片d1的鉴相器的可变输入端,所述锁相环芯片d1的电荷泵的直流电压输出端连接至所述恒温晶体振荡器d5的压控端。

3、进一步地,两个所述分频器d2和d3采用mc12093d。

4、进一步地,两个所述分频器d2和d3的sw1端和sw2端均为低电平0,输出八分频。

5、进一步地,所述分频器d2的输出端依次连接有电容c4和电容c16,且所述电容c4接地,所述电容c16连接所述锁相环芯片d1的参考输入端;所述分频器d3的输出端依次连接有电容c18和电容c17,且所述电容c18接地,所述电容c17连接所述锁相环芯片d1的鉴相器的可变输入端。

6、进一步地,所述锁相环芯片d1采用hc4046a。

7、进一步地,所述锁相环芯片d1的电荷泵的直流电压输出端通过外部环路滤波器连接至所述恒温晶体振荡器d5的压控端。

8、进一步地,所述外部环路滤波器包括依次连接的电阻r3、电容c8、电阻r4和电容c9,所述电阻r3和所述电容c8并联且接地,所述电阻r3连接有电容c11,所述电容c11并联有电容c10,所述电容c9接地。

9、进一步地,两个所述恒温晶体振荡器d4和d5、两个所述分频器d2和d3,及所述锁相环芯片d1均连接+5v电源。

10、进一步地,所述恒温晶体振荡器d4的输出端依次连接有电阻r2和电容c1,所述电阻r2接地,所述电容c1连接所述分频器d2;所述恒温晶体振荡器d5的输出端依次连接有电阻r1和电容c5,所述电阻r1接地,所述电容c5连接所述分频器d3。

11、本发明还提供了一种时钟同步方法,采用上述的一种时钟同步电路,包括:恒温晶体振荡器d4的输出频率经过分频器d2八分频后作为锁相环芯片d1的参考输入,恒温晶体振荡器d5的输出频率经过分频器d3八分频后作为锁相环芯片d1的鉴相器的可变输入,两个信号在锁相环芯片d1进行鉴频鉴相,利用锁相环芯片d1的电荷泵将频率和相位误差信号转化为直流电压,直流电压滤波后送入恒温晶体振荡器d5的压控端,当环路锁定后,两个恒温晶体振荡器d4和d5的频率和相位同步。

12、与现有技术相比,本发明的电路主要由两个完全一样的恒温晶体振荡器、两个分频器和一个锁相环芯片组成。其中一个恒温晶体振荡器d4作为参考振荡器,恒温晶体振荡器d5作为锁相环压控振荡器,环路锁定时,恒温晶体振荡器d5的相位和频率锁定到恒温晶体振荡器d4的参考相位和频率,实现两个恒温晶体振荡器频率和相位完全同步。将两个恒温晶体振荡器的频率通过锁相环的方式实现相位和频率同步后,解决了电台数据通信中出现的掉数据和噪声差等问题。

技术特征:

1.一种时钟同步电路,其特征在于,包括两个恒温晶体振荡器(d4,d5)、两个分频器(d2,d3)和一个锁相环芯片(d1),所述恒温晶体振荡器(d4)的输出端经过所述分频器(d2)连接所述锁相环芯片(d1)的参考输入端,所述锁相环芯片(d1)具有鉴相器和电荷泵,所述锁相环芯片(d1)的输出端连接所述恒温晶体振荡器(d5)的nc端,所述恒温晶体振荡器(d5)的输出端经所述分频器(d3)连接所述锁相环芯片(d1)的鉴相器的可变输入端,所述锁相环芯片(d1)的电荷泵的直流电压输出端连接至所述恒温晶体振荡器(d5)的压控端。

2.根据权利要求1所述的一种时钟同步电路,其特征在于,两个所述分频器(d2,d3)采用mc12093d。

3.根据权利要求2所述的一种时钟同步电路,其特征在于,两个所述分频器(d2,d3)的sw1端和sw2端均为低电平0,输出八分频。

4.根据权利要求2或3所述的一种时钟同步电路,其特征在于,所述分频器(d2)的输出端依次连接有电容(c4)和电容(c16),且所述电容(c4)接地,所述电容(c16)连接所述锁相环芯片(d1)的参考输入端;所述分频器(d3)的输出端依次连接有电容(c18)和电容(c17),且所述电容(c18)接地,所述电容(c17)连接所述锁相环芯片(d1)的鉴相器的可变输入端。

5.根据权利要求1所述的一种时钟同步电路,其特征在于,所述锁相环芯片(d1)采用hc4046a。

6.根据权利要求5所述的一种时钟同步电路,其特征在于,所述锁相环芯片(d1)的电荷泵的直流电压输出端通过外部环路滤波器连接至所述恒温晶体振荡器(d5)的压控端。

7.根据权利要求6所述的一种时钟同步电路,其特征在于,所述外部环路滤波器包括依次连接的电阻(r3)、电容(c8)、电阻(r4)和电容(c9),所述电阻(r3)和所述电容(c8)并联且接地,所述电阻(r3)连接有电容(c11),所述电容(c11)并联有电容(c10),所述电容(c9)接地。

8.根据权利要求1所述的一种时钟同步电路,其特征在于,两个所述恒温晶体振荡器(d4,d5)、两个所述分频器(d2,d3)和所述锁相环芯片(d1)均连接+5v电源。

9.根据权利要求1所述的一种时钟同步电路,其特征在于,所述恒温晶体振荡器(d4)的输出端依次连接有电阻(r2)和电容(c1),所述电阻(r2)接地,所述电容(c1)连接所述分频器(d2);所述恒温晶体振荡器(d5)的输出端依次连接有电阻(r1)和电容(c5),所述电阻(r1)接地,所述电容(c5)连接所述分频器(d3)。

10.一种时钟同步方法,采用如权利要求1至9中任一项所述的一种时钟同步电路,其特征在于,包括:恒温晶体振荡器(d4)的输出频率经过分频器(d2)八分频后作为锁相环芯片(d1)的参考输入,恒温晶体振荡器(d5)的输出频率经过分频器(d3)八分频后作为锁相环芯片(d1)的鉴相器的可变输入,两个信号在锁相环芯片(d1)进行鉴频鉴相,利用锁相环芯片(d1)的电荷泵将频率和相位误差信号转化为直流电压,直流电压滤波后送入恒温晶体振荡器(d5)的压控端,当环路锁定后,两个恒温晶体振荡器(d4,d5)的频率和相位同步。

技术总结

本发明公开了一种时钟同步电路及方法,电路包括两个恒温晶体振荡器(D4,D5)、两个分频器(D2,D3)和一个锁相环芯片(D1),恒温晶体振荡器(D4)的输出端经过分频器(D2)连接锁相环芯片(D1)的参考输入端,锁相环芯片(D1)具有鉴相器和电荷泵,锁相环芯片(D1)的输出端连接恒温晶体振荡器(D5)的NC端,恒温晶体振荡器(D5)的输出端经分频器(D3)连接锁相环芯片(D1)的鉴相器的可变输入端,锁相环芯片(D1)的电荷泵的直流电压输出端连接至恒温晶体振荡器(D5)的压控端,将两个恒温晶体振荡器相位和频率同步,解决了电台数据通信中出现的掉数据和噪声差的问题。

技术研发人员:赵玉振,李关策,杨俊英,张雪华

受保护的技术使用者:陕西烽火电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!