SOT-MRAM存储单元及其制备方法

本申请属于存储器件,具体涉及一种sot-mram存储单元及其制备方法。

背景技术:

1、随着自旋电子学的迅猛发展,自旋轨道耦合效应(spin-orbit coupling,soc)越来越受到人们的广泛关注,主要包括自旋霍尔效应和界面edelstein效应及其逆效应,可实现电压可控的电流和自旋流的相互转化。而自旋轨道矩(spin-orbit torque,sot)基于soc效应,利用电荷流诱导的自旋流产生自旋转移力矩,从而达到调控磁性存储单元的目的。由于其读写路径分开化,因此具有能耗低,写入速度快,磁矩翻转性强,效率高,稳定性高等优良性能,在磁存储器件等领域展现出巨大的前景。

2、自旋轨道矩型磁随机存储器(sot-mram)是利用自旋流产生的sot作为信息写入方式,既保持了mram高速度和低功耗等优异特性,又实现了读写路径的分离,更有利于提高器件的抗击穿和长寿命等性能。

3、目前对于采用性能优异的具有垂直磁各向异性的磁性隧道结作为基本存储单元的sot-mram来说,单独的自旋轨道矩无法实现确定性的定向磁化翻转,一般需要在特定方向上的外加磁场帮助下,才能够实现磁性隧道结中垂直自由层的确定性磁矩翻转和信息写入。但是外加磁场的引入增加了电路复杂度和可靠性风险,不利于器件的集成。

技术实现思路

1、本申请的技术目的是至少解决了sot-mram器件在无外加磁场下无法在有效集成下实现驱动自由层磁化翻转的问题。

2、该目的是通过以下技术方案实现的:

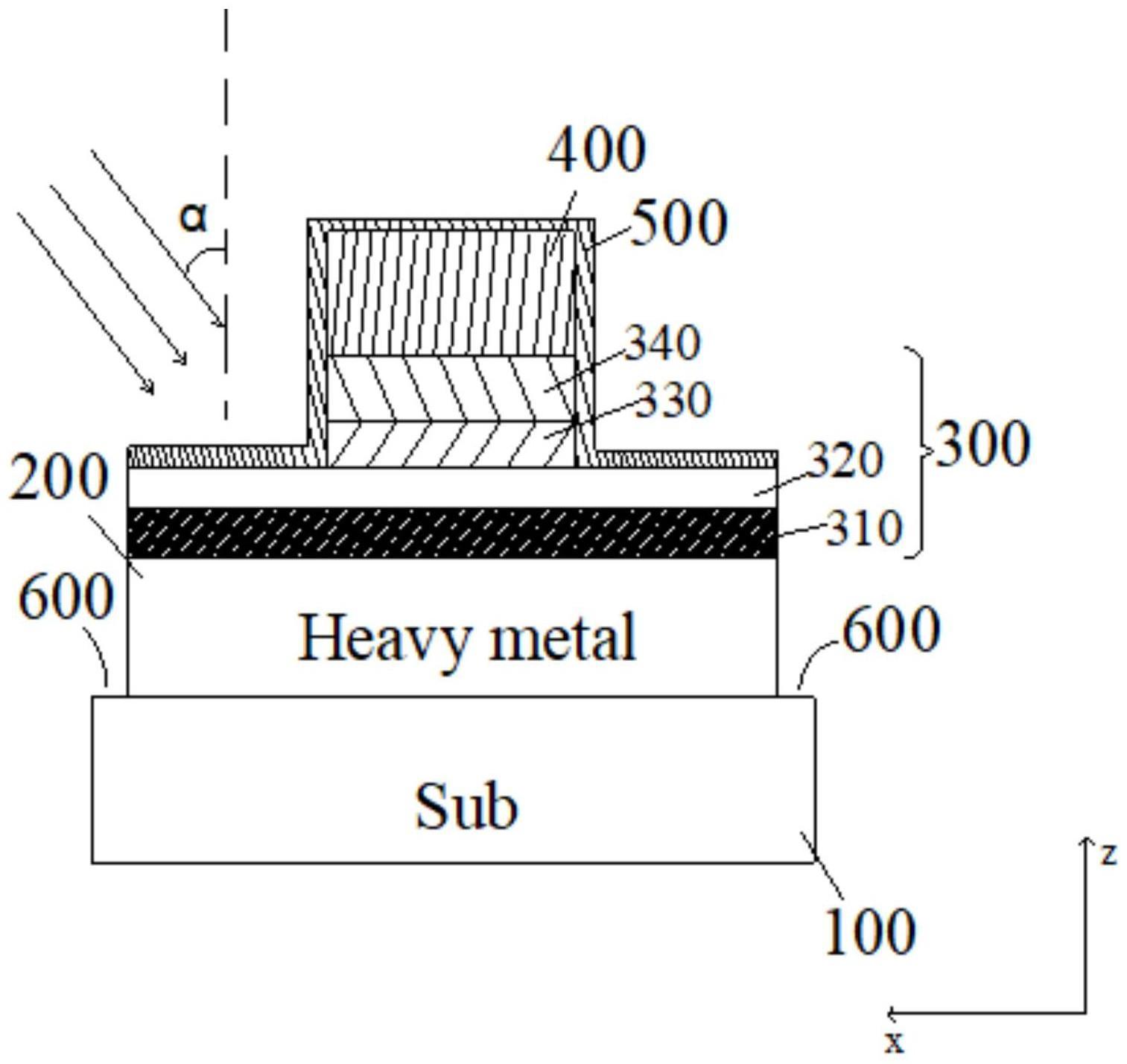

3、第一方面,本申请提供了一种sot-mram存储单元,包括:

4、衬底;

5、重金属层,设于所述衬底表面;

6、硬掩膜,位于所述重金属层上方;

7、磁性隧道结,设于所述重金属层与所述硬掩膜之间;

8、所述磁性隧道结包含层叠的自由层、势垒层、参考层及钉扎参考层;

9、所述参考层、钉扎参考层及硬掩膜构成柱体,所述柱体外周形成有保护层。

10、该存储单元具备大面积的不被硬掩膜遮盖的自由层,方便注入掺杂离子,更易驱动自由层的磁化翻转。

11、在本申请的一些实施方式中,所述柱体为圆柱、椭圆柱或多边形棱柱中的至少一种;

12、优选为圆柱。

13、在本申请的一些实施方式中,所述磁性隧道结中存在缺陷,所述缺陷沿重金属层中电流方向在磁性隧道结一侧的含量多于另一侧。

14、在本申请的一些实施方式中,所述缺陷由注入掺杂离子产生。

15、在本申请的一些实施方式中,所述掺杂离子包含氮、砷、氩、磷、硼或铍中的至少一种。

16、在本申请的一些实施方式中,所述存储单元还包括在衬底上设置用于容纳外电路的通道。

17、在本申请的一些实施方式中,所述自由层与参考层为磁性层,所述磁性层材料包含钴、铁、钴钯、铁钯、锰镓、钴铁硼、铁铂中的一种或两种以上组合;

18、所述势垒层为氧化层,所述氧化层材料包含氧化镁;

19、所述钉扎参考层采用锰基反铁磁性材料或多层膜人工反铁磁材料,所述锰基反铁磁性材料包含铱锰和/或铁锰,所述多层膜人工反铁磁材料包含钴、钯、铜、钌、钴钯、钴铜或钴钌中的一种或两种以上组合。

20、在本申请的一些实施方式中,所述重金属层为金属层或拓扑绝缘体层;

21、所述金属层材料包含钽、铂、钨、铪、铱、铜铋、铜铱或金钨中的一种或两种以上组合;

22、所述拓扑绝缘体层材料包含铋锡、锡碲或铋硒中的一种或两种以上组合;

23、所述硬掩膜材料包含钽和/或钌;

24、所述保护层材料包含氮化硅、碳化硅、氮氧化硅、氮碳化硅中的一种或两种以上组合。

25、第二方面,本申请提供了一种sot-mram存储单元的制备方法,包括:

26、提供衬底;

27、在所述衬底上形成重金属层;

28、在所述重金属层上形成自由层、势垒层、参考层及钉扎参考层;

29、在所述钉扎参考层表面形成硬掩膜;

30、自所述硬掩膜表面朝自由层方向图案化至势垒层表面停止,以形成磁性隧道结;

31、沿所述磁性隧道结一侧注入掺杂离子;

32、在所述参考层、钉扎参考层及硬掩膜外周形成保护层。

33、本申请设计的制备方法在势垒层表面停止图案化处理,有效缓解了由于势垒层附着金属进而容易引起器件短路的概率,有利于器件集成,与此同时,由于具备大面积的不被硬掩膜遮盖的自由层,该自由层方便完成注入掺杂离子,离子注入后磁性隧道结一侧缺陷会多余另一侧缺陷,从而在垂直于电流源方向上形成横向不对称的磁性隧道结结构,当重金属层中通入电流时,容易实现驱动自由层的磁化翻转。

34、在本申请的一些实施方式中,所述掺杂离子的注入方向与所述衬底的垂直方向之间具备夹角α,优选为0°<α<90°。

35、在本申请的一些实施方式中,所述衬底的垂直方向为坐标轴z方向。

36、在本申请的一些实施方式中,所述图案化包含光刻工艺,所述光刻工艺包含在硬掩膜表面形成光刻胶,光刻至势垒层表面停止。

37、在本申请的一些实施方式中,所述自由层、势垒层、参考层及钉扎参考层的形成方式包含溅射法、沉积法中的任意一种;所述沉积法包含原子层沉积或物理气相沉积。

38、在本申请的一些实施方式中,所述制备方法还包括自所述保护层表面朝重金属层方向刻蚀用于形成用于容纳外电路的通道。

39、本申请公开技术方案的有益效果主要体现在如下:

40、1、本申请提供的存储单元具备大面积的不被硬掩膜遮盖的自由层,方便注入掺杂离子,更易实现驱动自由层的磁化翻转。

41、2、本申请提供的存储单元制备方法在势垒层表面停止图案化处理,有效缓解了由于势垒层附着金属进而容易引起器件短路的概率,更方便器件集成。

技术特征:

1.一种sot-mram存储单元,其特征在于,包括:

2.根据权利要求1所述存储单元,其特征在于,所述柱体为圆柱、椭圆柱或多边形棱柱中的至少一种;

3.根据权利要求1所述存储单元,其特征在于,所述磁性隧道结中存在缺陷,所述缺陷沿重金属层中电流方向在磁性隧道结一侧的含量多于另一侧;

4.根据权利要求3所述存储单元,其特征在于,所述掺杂离子包含氮、砷、氩、磷、硼或铍中的至少一种。

5.根据权利要求1~4中任一项所述存储单元,其特征在于,所述存储单元还包括在衬底上设置用于容纳外电路的通道。

6.根据权利要求1~4中任一项所述存储单元,其特征在于,所述自由层与参考层为磁性层,所述磁性层材料包含钴、铁、钴钯、铁钯、锰镓、钴铁硼、铁铂中的一种或两种以上组合;

7.根据权利要求1~4中任一项所述存储单元,其特征在于,所述重金属层为金属层或拓扑绝缘体层;

8.一种sot-mram存储单元的制备方法,其特征在于,包括:

9.根据权利要求8所述存储单元的制备方法,其特征在于,所述掺杂离子的注入方向与所述衬底的垂直方向之间具备夹角α,优选为0°<α<90°。

10.根据权利要求8~9中任一项所述存储单元的制备方法,其特征在于,

技术总结

本申请属于存储器件技术领域,具体涉及一种SOT‑MRAM存储单元及其制备方法。本申请中的存储单元包含衬底,设于衬底表面的重金属层,在重金属层上形成的磁性隧道结,以及位于磁性隧道结上方的硬掩膜,该磁性隧道结包含层叠的自由层、势垒层、参考层及钉扎参考层,其中,参考层、钉扎参考层及硬掩膜构成柱体,在柱体外周还形成有保护层。该存储单元具备大面积的不被硬掩膜遮盖的自由层,方便注入掺杂离子,在不需要额外增加电路复杂度及不易造成器件短路前提下,能够有效驱动自由层的磁化翻转。

技术研发人员:杨美音,舒敬坤,罗军,李彦如

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!