用于电流隔离的电容耦合堆叠D类振荡器的制作方法

本公开大体上涉及电子电路,且在特定实施例中,涉及适用于半导体封装中的电流隔离的振荡器电路。

背景技术:

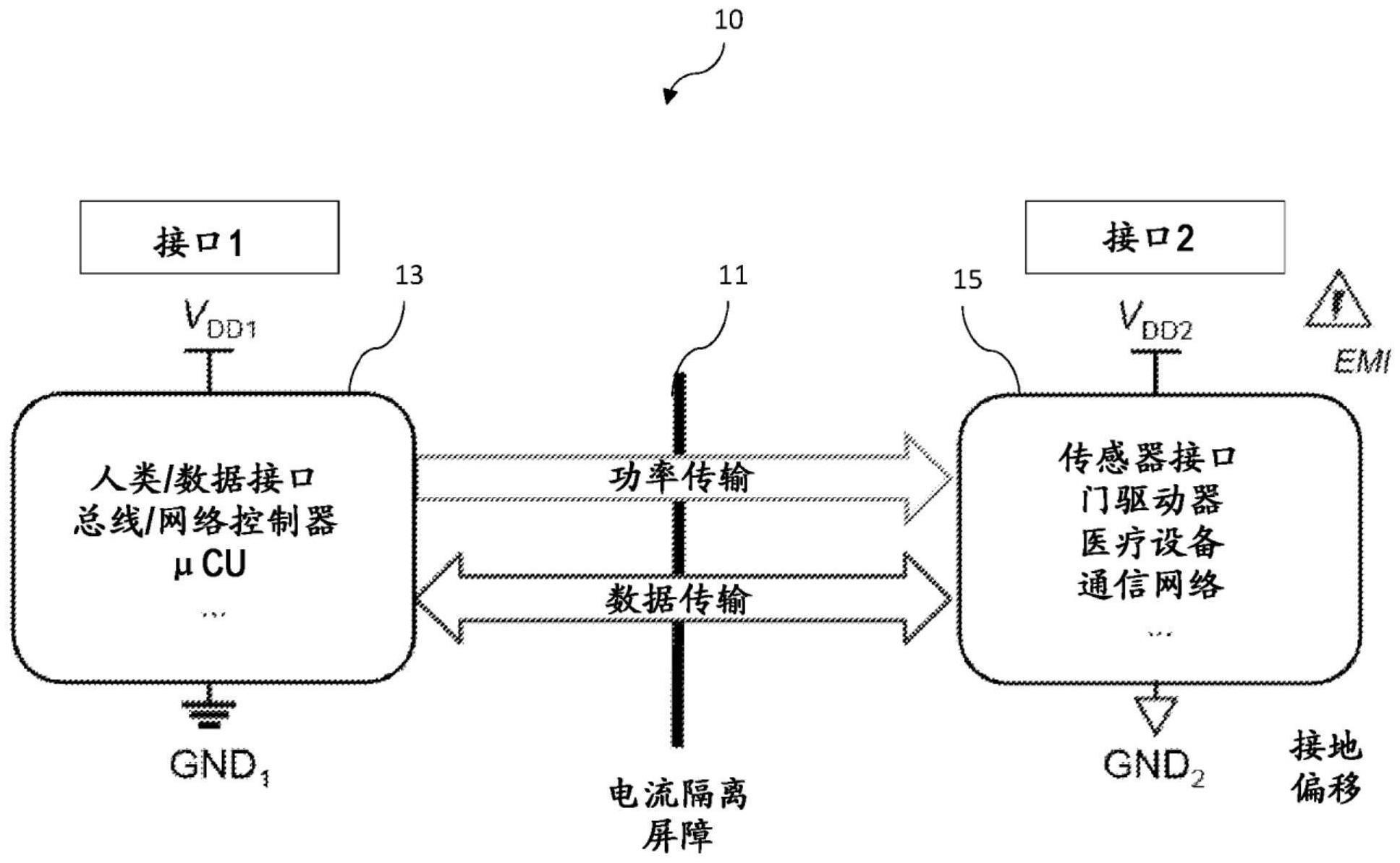

1、电流隔离技术通常用于电气系统中以改善各种应用(例如,工业传感器,医疗器件,用于电动机控制的栅极驱动器等)的安全性和可靠性。通常,电流隔离系统包括两个电流隔离的功率域,因为例如一个功率域受到危险电压,或者功率域具有不同的接地参考。电流隔离通常用于隔离不同的功率域以防止电流在隔离的功率域之间流动。能量或信息仍然可以通过其它手段在隔离的功率域之间交换,例如电容,电感或光学手段。

2、电流隔离的重要性能参数是最大浪涌隔离电压vsurge。最大浪涌隔离电压vsurge量化了隔离器承受某一瞬态曲线的非常高的电压脉冲的能力,该瞬态曲线可能由直接或间接雷击,故障或短路事件引起。如果单个隔离阻挡层通过10-kv浪涌测试,则最高级别的隔离,即加强的隔离被证明。用于电流隔离的另一重要参数是共模瞬态抗扰度(cmti),其测量隔离器件经受接地的快速移位(例如,高dv/dt)的能力,且其典型值在50kv/μs到200kv/μs范围内。通常,cmti性能与伽伐尼势垒的寄生电容效应有关。电流隔离有利于改善隔离等级,同时仍然保持在数据速率和cmti方面的竞争性能。

3、在不久的将来,诸如工业,汽车或医疗领域的应用领域可能需要高达20kv的vsurge。此外,由诸如氮化镓高电子迁移率晶体管(gan hemt)和碳化硅(sic)mosfet的宽带功率器件实现的较高开关频率可能需要超过200kv/μ的cmti。常规的芯片级隔离器(其中通过使用半导体芯片的一个或多个电介质层分离不同的功率域来实现电流隔离)基于电容器,变压器或lc混合网络,其利用例如厚的二氧化硅或聚酰亚胺层作为隔离阻挡层。这些方法分别由于最大可制造电介质厚度和相关的电容寄生效应而在隔离等级和cmti方面具有固有的限制。在本领域中需要具有改进的隔离等级和cmti性能的电流隔离技术。

技术实现思路

1、在一些实施例中,一种器件包括第一振荡器电路和第二振荡器电路。第一振荡器电路,包括:第一晶体管和第二晶体管,其中所述第一晶体管的栅极端子和所述第二晶体管的栅极端子耦合到第一节点,其中所述第一晶体管的第一负载路径端子和所述第二晶体管的第一负载路径端子耦合到参考电压节点;耦合在所述第一晶体管的第二负载路径端子与所述第二晶体管的第二负载路径端子之间的第一线圈;以及与所述第一线圈并联耦合的第一电容器。第二振荡器电路,包括:第三晶体管和第四晶体管,其中所述第三晶体管的栅极端子和所述第四晶体管的栅极端子耦合到第二节点,其中所述第三晶体管的第一负载路径端子和所述第四晶体管的第一负载路径端子耦合到所述第一线圈的中心抽头;耦合在所述第三晶体管的第二负载路径端子与所述第四晶体管的第二负载路径端子之间的第二线圈;以及与所述第二线圈并联耦合的第二电容器。该器件还包括:第三电容器,其耦合在所述第一晶体管的所述第二负载路径端子与所述第三晶体管的所述第二负载路径端子之间;以及第四电容器,其耦合在所述第二晶体管的所述第二负载路径端子与所述第四晶体管的所述第二负载路径端子之间。

2、在一些实施例中,一种器件包括第一振荡器电路和与所述第一振荡器电路级联的第二振荡器电路,其中所述第一振荡器电路和所述第二振荡器电路被配置为耦合在电源电压与电接地之间,其中所述第一振荡器电路和所述第二振荡器电路中的每一者是d类振荡器电路,其中所述d类振荡器电路包括:第一晶体管,其耦合在所述d类振荡器电路的参考电压节点与所述d类振荡器电路的第一输出之间;耦合在所述d类振荡器电路的参考电压节点和所述d类振荡器电路的第二输出之间的第二晶体管,其中所述第一晶体管的栅极端子和所述第二晶体管的栅极端子耦合到所述d类振荡器电路的偏置电压节点;耦合在所述d类振荡器电路的所述第一输出与所述第二输出之间的第一线圈;以及与所述第一线圈并联耦合的第一电容器。该器件还包括:第二电容器,其耦合在所述第一振荡器电路的所述第一输出与所述第二振荡器电路的所述第一输出之间;以及第三电容器,其耦合在所述第一振荡器电路的所述第二输出与所述第二振荡器电路的所述第二输出之间。

3、在一些实施例中,集成电路(ic)器件包括第一振荡器电路,该第一振荡器电路包括:第一晶体管和第二晶体管,其中第一晶体管的栅极端子通过第一电阻耦合到第一节点,第二晶体管的栅极端子通过第二电阻耦合到第一节点;耦合在所述第一晶体管的漏极端子与所述第二晶体管的漏极端子之间的第一电容器;以及与所述第一电容器并联耦合的第一线圈。该ic器件还包括第二振荡器电路,其中第二振荡器电路与第一振荡器电路相同,其中第一振荡器电路的第一晶体管的源极端子和第一振荡器电路的第二晶体管的源极端子耦合到参考电压节点,其中第二振荡器电路的第一晶体管的源极端子和第二振荡器电路的第二晶体管的源极端子耦合到第一振荡器电路的第一线圈的中心抽头,其中第二振荡器电路的第一线圈的中心抽头耦合到电源电压节点。所述ic器件还包括:第二电容器,其耦合在所述第一振荡器电路的所述第一晶体管的所述漏极端子与所述第二振荡器电路的所述第一晶体管的所述漏极端子之间;以及第三电容器,其耦合在所述第一振荡器电路的所述第二晶体管的所述漏极端子与所述第二振荡器电路的所述第二晶体管的所述漏极端子之间。

技术特征:

1.一种器件,包括:

2.根据权利要求1所述的器件,还包括:

3.根据权利要求2所述的器件,其中所述第一节点被配置为接收用于所述第一晶体管和所述第二晶体管的第一偏置电压,其中所述第一偏置电压具有第一固定值。

4.根据权利要求3所述的器件,其中所述第一晶体管和所述第二晶体管被配置为通过断开所述第一可控开关和所述第二可控开关而接通,其中所述第一晶体管和所述第二晶体管被配置为通过闭合所述第一可控开关和所述第二可控开关而被关断。

5.根据权利要求4所述的器件,还包括:

6.根据权利要求5所述的器件,其中所述第二节点被配置为接收用于所述第三晶体管和所述第四晶体管的第二偏置电压,其中所述第二偏置电压具有高于所述第一固定值的第二固定值。

7.根据权利要求6所述的器件,其中所述第三晶体管和所述第四晶体管被配置为通过断开所述第三可控开关和所述第四可控开关而被接通,其中所述第三晶体管和所述第四晶体管被配置为通过闭合所述第三可控开关和所述第四可控开关而被关断。

8.根据权利要求7所述的器件,其中所述第一可控开关、所述第二可控开关、所述第三可控开关和所述第四可控开关被配置为同时被接通和关断。

9.根据权利要求1所述的器件,其中所述第二线圈的中心抽头耦合到电源电压节点。

10.根据权利要求1所述的器件,其中所述第一振荡器电路还包括:

11.根据权利要求10所述的器件,其中所述第二振荡器电路还包括:

12.一种器件,包括:

13.根据权利要求12所述的器件,其中所述第一振荡器电路的所述lc谐振电路被配置为生成第一振荡器信号,并且所述第二振荡器电路的所述lc谐振电路被配置为生成第二振荡器信号,其中所述第一振荡器信号和所述第二振荡器信号具有相同频率和相同相位。

14.根据权利要求12所述的器件,其中所述第一振荡器电路的所述参考电压节点被配置为耦合到所述电接地,其中所述第二振荡器电路的所述参考电压节点耦合到所述第一振荡器电路的所述第一线圈的中心抽头,其中所述第二振荡器电路的所述第一线圈的中心抽头被配置为耦合到所述电源电压。

15.根据权利要求12所述的器件,其中所述第一振荡器电路的所述偏置电压节点被配置为被提供有第一偏置电压,其中所述第二振荡器电路的所述偏置电压节点被配置为被提供有高于所述第一偏置电压的第二偏置电压。

16.根据权利要求15所述的器件,其中所述第一偏置电压和所述第二偏置电压具有相应固定值,其中所述d类振荡器电路还包括:

17.一种集成电路ic器件,包括:

18.根据权利要求17所述的ic器件,其中所述第一振荡器电路的所述第一节点被配置为被提供有第一偏置电压,并且所述第二振荡器电路的所述第一节点被配置为被提供有不同于所述第一偏置电压的第二偏置电压。

19.根据权利要求17所述的ic器件,其中所述第一振荡器电路的所述第一线圈和所述第二振荡器电路的所述第一线圈包括所述ic器件的一个或多个电介质层中的金属图案,其中在顶视图中,所述第一振荡器电路的所述第一线圈与所述第二振荡器电路的所述第一线圈间隔开。

20.根据权利要求17所述的ic器件,其中所述第一振荡器电路的所述第一线圈和所述第二振荡器电路的所述第一线圈包括在所述ic器件的不同电介质层中的金属图案,其中在顶视图中,所述第一振荡器电路的所述第一线圈与所述第二振荡器电路的所述第一线圈重叠。

技术总结

本公开涉及用于电流隔离的电容耦合堆叠D类振荡器。振荡器电路包括在电源电压节点和参考电压节点之间堆叠在一起的总共N(N≥2)个D类振荡器电路。所公开的振荡器电路中的相邻D类振荡器电路的输出端口通过电容器耦合在一起,以确保D类振荡器电路生成的频率信号的频率和相位同步。与由单个D类振荡器电路形成的参考振荡器电路相比,所公开的振荡器电路中的每个D类振荡器电路的振荡幅度是参考振荡器电路的振荡幅度的1/N,并且所公开的振荡器电路的电流消耗是参考振荡器电路的电流消耗的1/N。

技术研发人员:S·斯帕塔罗,S·科法,E·拉哥奈瑟

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!