三维存储器器件和方法与流程

本公开总体涉及三维存储器器件和方法。

背景技术:

1、半导体存储器用于电子应用的集成电路中,例如包括收音机、电视、手机和个人计算设备。半导体存储器包括两大类。一类是易失性存储器;另一类是非易失性存储器。易失性存储器包括随机存取存储器(ram),ram可以进一步分为两个子类:静态随机存取存储器(sram)和动态随机存取存储器(dram)。sram和dram两者都是易失性的,因为它们在断电时会丢失其存储的信息。

2、另一方面,非易失性存储器可以保持其存储的数据。一种类型的非易失性半导体存储器是铁电随机存取存储器(feram)。feram的优点包括其快速的写入/读取速度和小尺寸。

技术实现思路

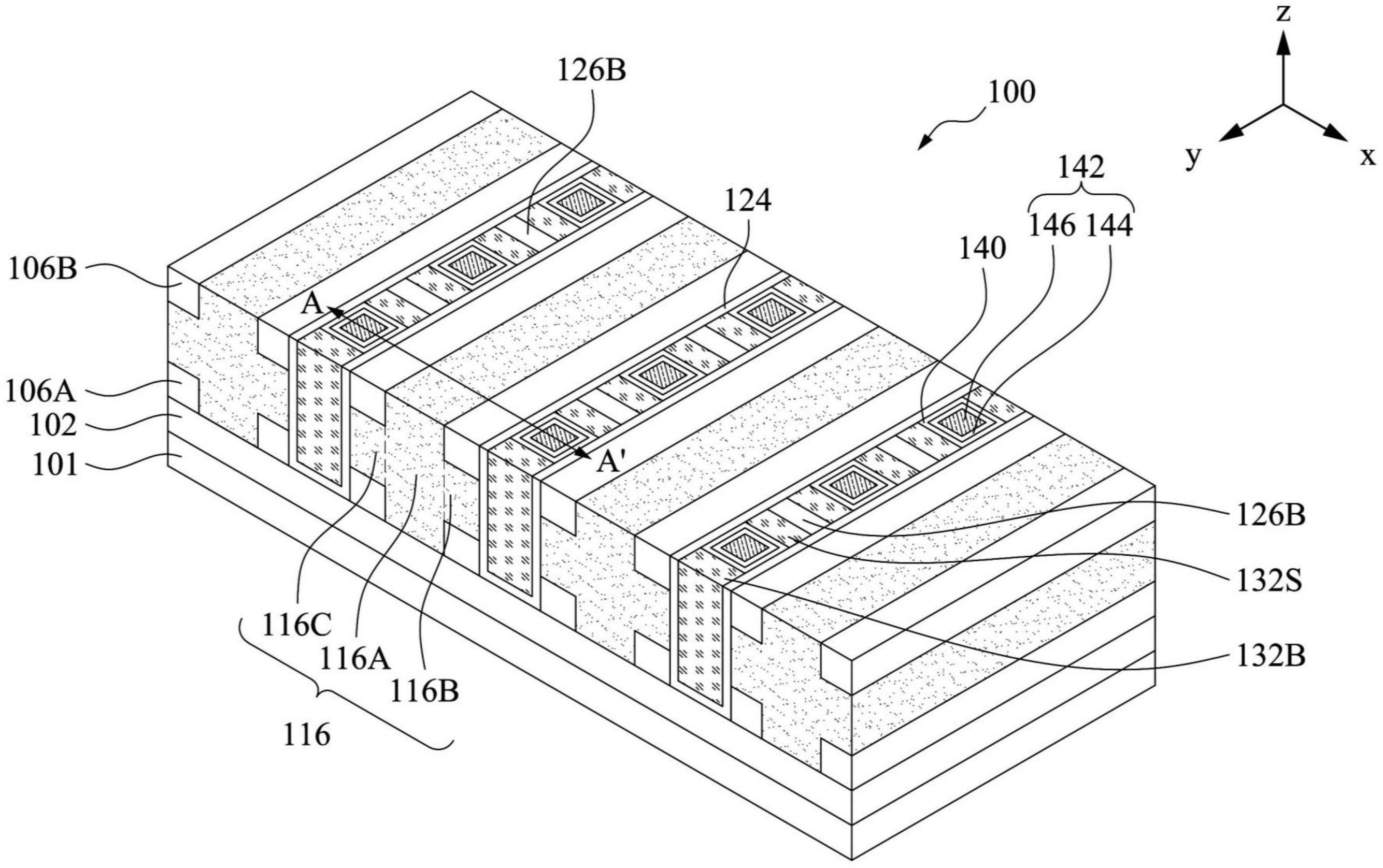

1、根据本公开的第一实施例,提供了一种半导体器件,包括:第一栅极结构,位于衬底之上,所述第一栅极结构包括位于第一栅极电介质的第一侧之上的第一栅极电极;第一电极,设置在所述第一栅极电介质的与所述第一侧相反的第二侧之上;第二电极,设置在所述第一栅极电介质的第二侧之上;第二栅极结构,设置在所述第一电极和所述第二电极之间,所述第二栅极结构包括第二栅极电极和第二栅极电介质,所述第二栅极电介质至少在侧面包围所述第二栅极电极;以及半导体膜,设置在所述第一电极和所述第二电极之间,并且至少在侧面包围所述第二栅极结构,其中,所述第一栅极电介质或所述第二栅极电介质中的至少一者为存储器膜。

2、根据本公开的第二实施例,提供了一种半导体器件,包括:第一栅极电介质,在第一方向上延伸;字线,在第二方向上设置在所述第一栅极电介质的第一侧之上并在所述第一方向上延伸,所述第二方向垂直于所述第一方向;第一电极,在所述第二方向上设置在所述第一栅极电介质的与所述字线相反的第二侧之上,所述第一电极是第一位线的一部分或电耦合到第一位线;第二电极,设置在所述第一栅极电介质的第二侧之上,所述第二电极是第一源极线的一部分或电耦合到第一源极线;半导体膜,设置在所述第一电极和所述第二电极之间;以及第一栅极结构,在所述第一方向上设置在所述半导体膜的一部分之上,使得所述半导体膜的该部分夹在所述第一栅极电介质和所述第一栅极结构之间,其中,所述字线和所述第一栅极结构的顶表面彼此齐平。

3、根据本公开的第三实施例,提供了一种形成半导体器件的方法,所述方法包括:在衬底之上形成多层堆叠,所述多层堆叠包括第一电介质层、第二电介质层和夹在所述第一电介质层和所述第二电介质层之间的第三电介质层,所述第三电介质层具有不同于所述第一电介质层和所述第二电介质层的材料;形成延伸穿过所述多层堆叠的第一沟槽;使所述第二电介质层的侧壁从所述第一沟槽凹陷,以在所述第一电介质层和所述第二电介质层之间形成侧壁凹部;在所述第一沟槽和所述侧壁凹部中形成导电线;去除所述第一电介质层的一部分、所述第二电介质层的一部分以及所述第三电介质层的至少一部分,以形成邻近所述导电线的第二沟槽;在所述第二沟槽中形成第一栅极电介质;以及在所述第一栅极电介质之上和所述第二沟槽中形成第一电极、第二电极、半导体膜和栅极结构,所述半导体膜和所述栅极结构设置在所述第一电极和所述第二电极之间。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的器件,其中,所述第一栅极电极包括在第二部分和第三部分之间的第一部分,其中,所述第一部分具有不同于所述第二部分和所述第三部分的厚度。

3.根据权利要求2所述的器件,还包括第一电介质层,所述第一电介质层设置在所述第一栅极电极的第二部分下方,并且位于所述第一栅极电极的第一部分与所述第一栅极电介质之间。

4.根据权利要求2所述的器件,还包括第二电介质层,所述第二电介质层设置在所述第一栅极电极的第二部分上方,并且位于所述第一栅极电极的第一部分与所述第一栅极电介质之间。

5.根据权利要求1所述的器件,其中,所述第二栅极电介质在所述第二栅极电极下方延伸。

6.根据权利要求1所述的器件,其中,所述半导体膜在所述第二栅极结构下方延伸。

7.根据权利要求1所述的器件,其中,所述第一栅极电极和所述第二栅极电极由不同的材料形成。

8.根据权利要求1所述的器件,其中,所述第一电极电耦合到位线,并且所述第二电极电耦合到源极线。

9.一种半导体器件,包括:

10.一种形成半导体器件的方法,所述方法包括:

技术总结

本公开总体涉及三维存储器器件和方法。在一个实施例中,一种器件包括:第一栅极结构,位于衬底之上,第一栅极结构包括位于第一栅极电介质的第一侧之上的第一栅极电极;第一电极和第二电极,设置在第一栅极电介质的与第一侧相反的第二侧之上;第二栅极结构,设置在第一电极和第二电极之间,第二栅极结构包括第二栅极电极和第二栅极电介质,第二栅极电介质至少在侧面包围第二栅极电极;以及半导体膜,设置在第一电极和第二电极之间,并且至少在侧面包围第二栅极结构,其中,第一栅极电介质或第二栅极电介质中的至少一者为存储器膜。

技术研发人员:林孟汉,杨世海,黄家恩,徐志安

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!