晶振起振电路、集成芯片封装方法、集成芯片及电子设备与流程

本技术涉及芯片,具体涉及一种晶振起振电路、集成芯片封装方法、集成芯片及电子设备。

背景技术:

1、传统的双端口晶振电路包括输入端口in和输出端口out两个连接端口,当将其与集成芯片进行封装时,需要占用集成芯片的两个引脚进行封装。

2、由于集成芯片的引脚个数受封装规范的严格限制,例如,8pin、16pin等,随着微电子和通讯技术的迅速发展,芯片功能越来越丰富,其集成规模也越来越大,相应地,芯片需要设置有更多用以连接具体的应用功能的引脚。因此,为了减少振荡电路占用的引脚数量,降低芯片的封装成本,在一些集成芯片中,采用单端晶振起振电路。然而,现有的单端晶振起振电路在性能和稳定性方面相较于双端晶振起振电路更低,对于一些性能要求较高的运用需求仍需要采用双端晶振起振电路。导致了现有的晶振起振电路采用双端晶振起振电路以满足晶振起振电路的性能要求,或者采用单端晶振起振电路以满足芯片的封装要求,从而导致了集成芯片在封装时仅能根据需求采用固定封装方式进行封装,导致了集成芯片在应用时的灵活性较低。

技术实现思路

1、本技术实施例的一个目的旨在提供一种晶振起振电路、集成芯片封装方法、集成芯片及电子设备,旨在改善现有集成芯片在封装时仅能根据需求采用固定封装方式进行封装,导致了集成芯片在应用时的灵活性较低的问题。

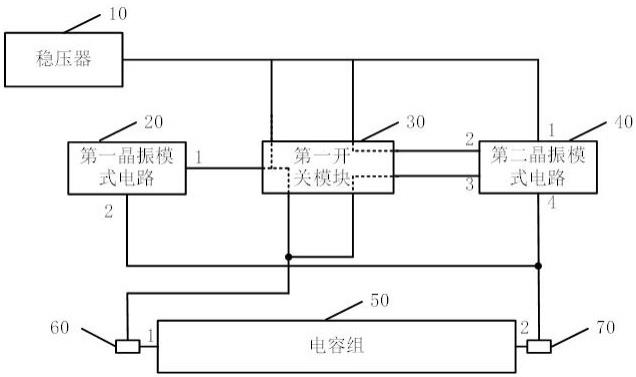

2、在第一方面,本技术实施例提供一种晶振起振电路,所述晶振起振电路应用于集成芯片,所述晶振起振电路包括:稳压器、第一晶振模式电路、开关组件、第二晶振模式电路、电容组件、第一端口和第二端口,其中,

3、所述第一晶振模式电路通过所述开关组件与所述稳压器的输出端连接,所述第一晶振模式电路的第一端通过所述开关组件与所述电容组件的第一端连接,所述第一晶振模式电路的第二端与所述电容组件的第二端连接;

4、所述第二晶振模式电路的第一端与所述稳压器的输出端连接,所述第二晶振模式电路的第二端通过所述开关组件与所述稳压器的输出端连接,所述第二晶振模式电路的第三端通过所述开关组件与所述电容组件的第一端连接,所述第二晶振模式电路的第四端与所述电容组件的第二端连接,所述电容组件的第一端与所述第一端口连接,所述电容组件的第二端与所述第二端口连接;

5、根据所述集成芯片的类型,所述晶振起振电路在所述集成芯片封装时将所述第一端口和/或所述第二端口与所述集成芯片的第一晶振引脚和/或第二晶振引脚连接。

6、在一个可能的实现方式中,所述第一晶振模式电路包括:第三电阻、第一mos管、第二mos管、第一电容,

7、所述第三电阻的第一端通过所述开关组件与所述稳压器的输出端连接,所述第三电阻的第二端与所述第一mos管的源极、所述第一电容的第一端连接,所述第一电容的第一端通过所述开关组件与所述稳压器的输出端连接,所述第一电容的第二端接地,

8、所述第一mos管的栅极通过所述开关组件分别与所述稳压器的输出端、所述电容组件的第一端、所述第二mos管的栅极、所述第一mos管的漏极连接;

9、所述第二mos管的漏极与所述第一mos管的漏接连接后与所述电容组件的第二端连接,所述第二mos管的源极通过所述开关组件接地。

10、在一个可能的实现方式中,所述第二晶振模式电路包括:第四电阻、第三mos管、第五电阻,其中,

11、所述第四电阻的第一端通过所述开关组件与所述稳压器的输出端连接,所述第四电阻的第二端与所述第三mos管的栅极连接且通过所述开关组件接地;

12、所述第三mos管的漏极与所述稳压器的输出端连接,所述第三mos管的源极分别与所述第五电阻的第一端、所述电容组件的第二端连接,所述第三mos管的栅极与所述第四电阻的第二端连接,且所述第三mos管的栅极通过所述开关组件与所述电容组件的第一端连接;

13、所述第五电阻的第二端通过所述开关组件接地。

14、在一个可能的实现方式中,所述电容组件包括第二电容、第三电容、第十一开关和第十二开关,其中,

15、所述第二电容的第一端为所述电容组件的第一端,所述第二电容的第二端分别与所述第十一开关、所述第十二开关的第一端连接,所述第十一开关的第二端与所述第三电容的第一端连接后的连接端为所述电容组件的第二端,所述第三电容的第二端与所述第十二开关的第二端连接后接地。

16、在一个可能的实现方式中,所述开关组件包括第一开关、第二开关、第三开关、第四开关、第五开关、第六开关、第七开关、第八开关、第九开关、第十开关、第一电阻和第二电阻,其中,

17、所述第四开关的第一端、所述第五开关的第一端、所述第六开关的第一端、所述第七开关的第一端分别与所述稳压器的输出端连接;

18、所述第四开关的第二端分别与所述第一mos管的栅极、所述第一电阻的第一端、所述第一开关的第一端、所述第二mos管的栅极连接;

19、所述第一电阻的第二端通过所述第二开关与所述第二电阻的第一端连接,所述第二电阻的第二端与所述第二mos管的漏极连接;

20、所述第一开关的第二端分别与所述电容组件的第一端、所述第八开关的第二端连接;

21、所述第八开关的第一端分别与所述第九开关的第一端、所述第四电阻的第二端、所述第三mos管的栅极连接,所述第九开关的第二端与所述第十开关的第二端连接后接地,所述第十开关的第一端与所述第五电阻的第二端连接后与所述第三mos管的源极连接;

22、所述第五开关的第二端通过所述第三电阻与所述第一mos管的源极连接;

23、所述第六开关的第二端分别与所述第一mos管的源极和所述第一电容连接,且与所述第一电容连接后接地;

24、所述第七开关的第二端与所述第四电阻的第一端连接;所述第二mos管的源极通过所述第三开关接地。

25、在一个可能的实现方式中,所述第三电阻、所述第五电阻包括可变电阻,所述第二电容、所述第三电容包括可变电容。

26、在一个可能的实现方式中,所述稳压器包括第六电阻、第七电阻、第八电阻、第九电阻、第十电阻、第四mos管、第五mos管、第六mos管、第一三极管、第二三极管、第四电容和第五电容,其中,

27、所述第七电阻的第一端、所述第六电阻的第一端、所述第六mos管的漏极分别与参考电压端连接,所述第七电阻的第二端与所述第四mos管的源极连接;

28、所述第四mos管的栅极与所述第五mos管的栅极连接,所述第四mos管的漏极与所述第四mos管的栅极连接;

29、所述第一三极管的集电极与所述第四mos管的漏极连接,所述第一三极管的基极与所述第二三极管的基极连接,所述第一三极管的发射极与所述第八电阻的第一端连接,所述第八电阻的第二端与所述第九电阻连接后接地;

30、所述第五mos管的源极与所述第六电阻的第二端连接,所述第五mos管的漏极分别与所述第二三极管的集电极和所述第六mos管的栅极连接;

31、所述第二三极管的发射极与所述第九电阻连接后接地;

32、所述第六mos管的源极与所述第十电阻连接后接地,且所述第六mos管的源极为所述稳压器的输出端;

33、所述第四电容的第一端连接在所述第五mos管漏极和所述第六mos管栅极的连接端,所述第四电容的第二端接地;

34、所述第五电容的第一端分别连接在所述第一三极管基极与所述第二三极管基极的连接端和所述第六mos管与所述第十电阻的连接端。

35、在一个可能的实现方式中,所述稳压器的温度系数通过所述第八电阻和所述第九电阻的阻值比例进行调节。

36、在一个可能的实现方式中,所述晶振起振电路还包括:第十一电阻,所述第十一电阻的第一端连接在所述第五mos管漏极和所述第六mos管栅极的连接端,所述第十一电阻的第二端与所述第四电容连接后接地。

37、在一个可能的实现方式中,所述晶振起振电路还包括:第一二极管和第十二电阻,其中,

38、所述第一二极管的负极与所述稳压器的输出端连接,所述第一二极管的正极与所述第十二电阻连接后接地。

39、在一个可能的实现方式中,所述晶振起振电路还包括:第六电容,所述第六电容的第一端与所述第四电阻的第二端连接,所述第六电容的第二端接地。

40、在一个可能的实现方式中,所述根据所述集成芯片的类型,所述晶振起振电路在所述集成芯片封装时将所述第一端口和/或所述第二端口与所述集成芯片的第一晶振引脚和/或第二晶振引脚连接,包括:

41、若所述集成芯片为第一晶振模式集成芯片,则所述集成芯片在封装时所述第一晶振模式电路通过所述第一端口与所述集成芯片的第一晶振引脚连接,所述第一晶振模式电路通过所述第二端口与所述集成芯片的第二晶振引脚连接;或者,

42、若所述集成芯片为第二晶振模式集成芯片,则所述集成芯片在封装时所述第二晶振模式电路通过所述第一端口或所述第二端口与所述集成芯片的第一晶振引脚连接或第二晶振引脚连接。

43、在第二方面,本技术实施例提供一种集成芯片的封装方法,所述集成芯片的封装方法应用于如第一方面中任一项所述的晶振起振电路,所述方法包括:

44、提供封装模具;

45、根据集成芯片的类型,该晶振起振电路在集成芯片封装时将该第一端口和/或该第二端口与该集成芯片的第一晶振引脚和/或第二晶振引脚连接;

46、通过封装模具进行封装,得到集成芯片。

47、在第三方面,本技术实施例提供一种集成芯片,所述集成芯片通过如第二方面所述的集成芯片的封装方法制得。

48、在第四方面,本技术实施例提供一种电子设备,所述电子设备包括壳体和如第三方面所述的集成芯片,所述集成芯片设置于所述壳体内。

49、在本技术实施例提供的晶振起振电路中,可以根据所述集成芯片的类型,晶振起振电路在集成芯片封装时将所述第一端口和/或第二端口与集成芯片的第一晶振引脚和/或第二晶振引脚连接,因此,在集成芯片进行封装时,可以根据不同集成芯片的类型采用不同的封装方式进行封装,从而提升了集成芯片在应用时的灵活性。

- 还没有人留言评论。精彩留言会获得点赞!