一种小数分频锁相环和数字时间转换器控制方法

本技术涉及射频,特别是一种小数分频锁相环和数字时间转换器控制方法。

背景技术:

1、锁相环电路中使用的数字时间转换器(digital-to-time converter,dtc)可以消除微分积分调制器(dsm)在分数n模式下工作时引入的量化误差,有利于改善锁相环(phase-locked loop,pll)的相位噪声(pn)水平。因此,在需要高质量频率综合器的技术领域,基于数字时间转换器的小数分频锁相环被广泛采用。

2、然而,数字时间转换器的增益准确性会影响相位噪声,非线性的矫正效果会影响杂散,所以需要对增益误差和非线性误差进行矫正。同时,数字时间转换器的增益和非线性对工艺、电源电压、温度变化十分敏感,在电路运行过程中,数字时间转换器的增益也可能随着时间发生变化。在现有技术中,数字时间转换器矫正技术主要在电压域完成,需要配合电压域采样器、电压比较器才能完成矫正,该方法对传统的模拟锁相环的兼容性较差,并且矫正效果不够理想。

3、因此,有必要开发一种小数分频锁相环和数字时间转换器控制方法,以实现在锁相环运行过程中,对数字时间转换器的增益误差和非线性误差进行修正。

技术实现思路

1、鉴于上述问题,本技术实施例提供了一种小数分频锁相环和数字时间转换器控制方法,以便克服上述问题或者至少部分地解决上述问题。

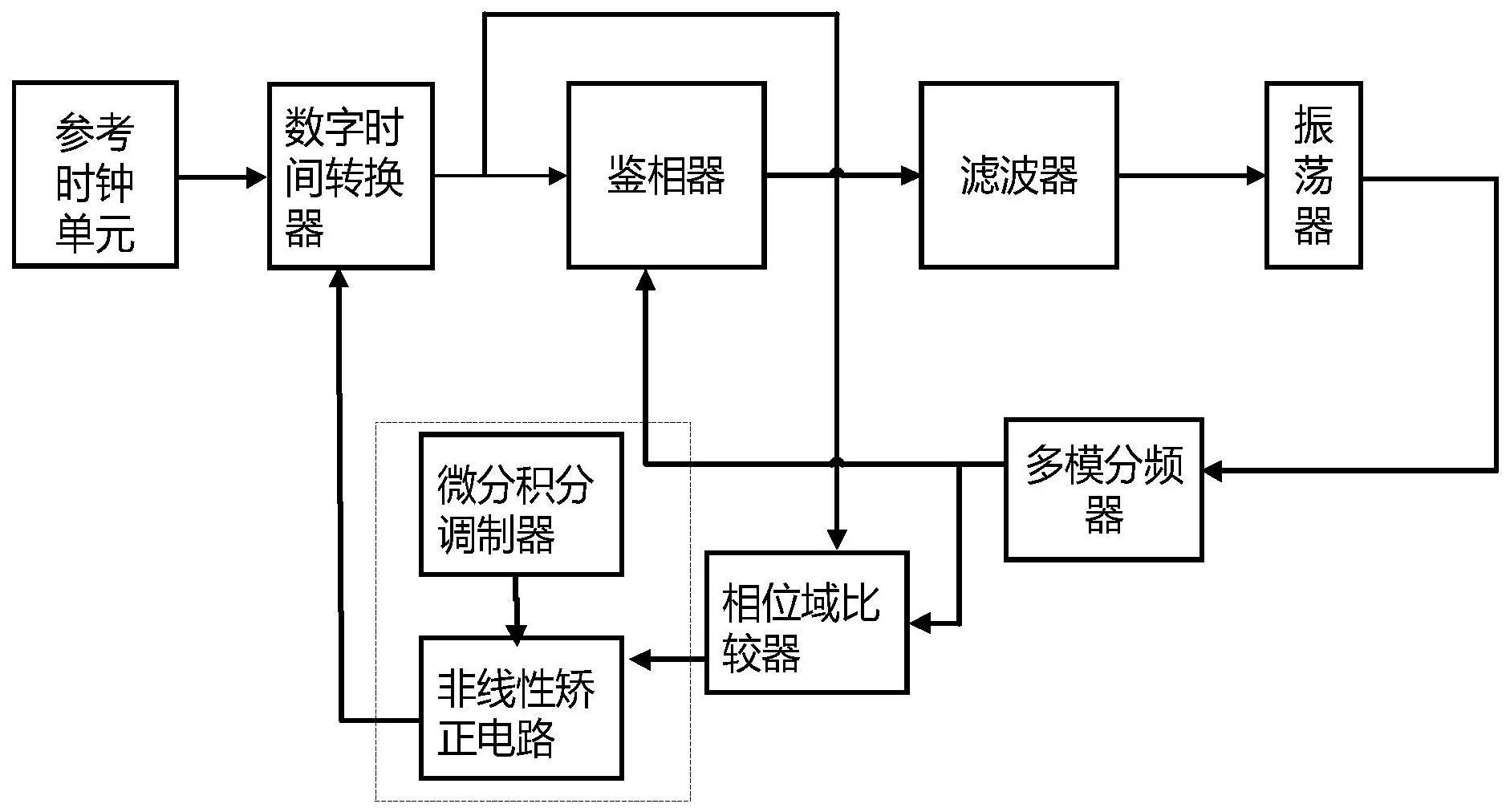

2、本技术实施例的第一方面,提供了一种小数分频锁相环,所述锁相环包括:第一电路、参考时钟单元、数字时间转换器、相位域比较器、微分积分调制器和非线性矫正电路;所述第一电路包括:鉴相器、滤波器、振荡器和多模分频器;

3、所述多模分频器和所述数字时间转换器的输出分别连接至所述相位域比较器;所述相位域比较器被配置用于根据所述多模分频器输出的分频信号,和,所述数字时间转换器输出的调制后时钟信号,输出相位误差信号;

4、所述相位域比较器的输出连接至所述非线性矫正电路;所述微分积分调制器的输出连接至所述非线性矫正电路,所述微分积分调制器被配置用于向所述非线性矫正电路输出量化误差信号;

5、所述非线性矫正电路的输出连接至所述数字时间转换器;所述非线性矫正电路被配置用于根据所述相位误差信号和所述量化误差信号,向所述数字时间转换器输出控制信号,以对所述数字时间转换器进行控制。

6、可选地,所述相位域比较器还包括:第一压控延时链、第二压控延时链、bang-bang鉴相器、压控单元;

7、所述多模分频器的输出一路连接至所述第一压控延时链,另一路连接至所述鉴相器;所述多模分频器向所述第一压控延时链发送所述分频信号,所述第一压控延时链被设置用于对所述分频信号进行延时,输出延时分频信号;

8、所述数字时间转换器的输出一路连接至所述第二压控延时链,另一路连接至所述鉴相器;所述数字时间转换器向所述第二压控延时链发送所述调制后时钟信号,所述第二压控延时链被设置用于对所述调制后时钟信号进行延时,输出延时时钟信号;

9、所述第一压控延时链和所述第二压控延时链的输出连接至所述bang-bang鉴相器;所述bang-bang鉴相器被设置用于根据所述延时分频信号和所述延时时钟信号,输出所述相位误差信号;

10、所述bang-bang鉴相器的输出还连接至所述压控单元,所述压控单元的输出一路连接至所述第一压控延时链,另一路连接至所述第二压控延时链,所述压控单元被配置用于根据所述相位误差信号,对第一压控延时链和所述第二压控延链进行控制。

11、可选地,所述微分积分调制器的另一路输出连接至所述多模分频器,向所述多模分频器输出分频控制字信号;

12、所述多模分频器根据所述分频控制字信号输出所述分频信号。

13、可选地,所述非线性矫正电路包括:

14、误差提取模块,用于对所述量化误差信号进行提取,得到分段控制信号和残余误差信号;

15、n+1条查找表路径,每条所述查找表路径根据所述分段控制信号和所述残余误差信号,得到输出值,其中,n为任意大于1的常数;每条所述查找表路径的输出连接至拟合模块,所述n+1条查找表路径表示0至n阶非线性函数所对应查找表路径;

16、所述拟合模块,用于拟合所述n+1条查找表路径的输出值,得到所述控制信号。

17、可选地,所述误差提取模块,包括:

18、量化元件和减法元件;

19、所述量化元件根据所述量化误差信号,进行量化处理,得到所述分段控制信号;所述量化元件的输出一路连接至所述减法元件;

20、所述减法元件根据所述量化误差信号和所述分段控制信号,得到所述残余误差信号。

21、可选地,每条所述查找表路径包括:

22、矫正参数提取模块和查找表模块;

23、所述减法元件的输出连接至每条所述查找表路径中的所述矫正参数提取模块,向所述矫正参数提取模块输入所述残余误差信号;

24、所述相位域比较器的输出连接至每条所述查找表路径中的所述矫正参数提取模块,向所述矫正参数提取模块输入所述相位误差信号;

25、所述矫正参数提取模块被配置用于根据所述相位误差信号和所述残余误差信号,提取矫正参数;

26、所述量化元件的输出还连接至每条所述查找表路径中的所述查找表模块,向所述查找表模块输入所述分段控制信号,所述查找表模块根据所述分段控制信号和所述矫正参数,得到输出值。

27、可选地,每条所述查找表路径的所述查找表模块包括m条通道,m为任意大于1的常数;每条通道表示所述数字时间转换器的非线性函数的一个区间;

28、所述查找表模块根据所述分段控制信号,从所述m条通道中确定出目标通道;

29、所述目标通道根据所述矫正参数,计算得到所述输出值。

30、可选地,所述数字时间转换器的另一路输出连接至所述鉴相器,向所述鉴相器发送所述调制后时钟信号;

31、所述多模分频器的另一路输出连接至所述鉴相器,向所述鉴相器发送所述分频信号;

32、所述鉴相器被配置用于根据所述调制后时钟信号和所述分频信号,输出误差信号;

33、所述鉴相器的输出连接至所述滤波器,所述滤波器对所述误差信号进行滤波,输出频率控制信号;

34、所述滤波器的输出连接至所述振荡器,所述振荡器根据所述滤波器发送的所述频率控制信号调整输出信号的频率;

35、所述振荡器的输出连接至所述多模分频器,所述多模分频器被配置用于对所述输出信号进行分频,得到所述分频信号。

36、本技术实施例第二方面提供了一种数字时间转换器控制方法,应用于第一方面任一项所述的小数分频锁相环,所述方法包括:

37、获取多模分频器输出的分频信号和数字时间转换器输出的调制后时钟信号;

38、通过相位域比较器,根据所述分频信号和所述调制后时钟信号,得到相位误差信号;

39、通过非线性矫正电路,根据所述相位误差信号和微分积分调制器输出的量化误差信号,向所述数字时间转换器输出控制信号,以对所述数字时间转换器进行控制。

40、可选地,所述相位域比较器还包括:第一压控延时链、第二压控延时链、bang-bang鉴相器、压控单元;

41、所述通过相位域比较器,根据所述分频信号和所述调制后时钟信号,得到相位误差信号,包括:

42、所述多模分频器向所述相位域比较器的所述第一压控延时链发送所述分频信号,所述第一压控延时链对所述分频信号进行延时,输出延时分频信号;

43、所述数字时间转换器向所述相位域比较器的所述第二压控延时链发送所述调制后时钟信号,所述第二压控延时链对所述调制后时钟信号进行延时,输出延时时钟信号;

44、所述bang-bang鉴相器根据所述延时分频信号和所述延时时钟信号,输出所述相位误差信号;

45、所述方法还包括:

46、根据所述相位误差信号,对第一压控延时链和所述第二压控延链进行控制。

47、可选地,所述方法,包括:

48、所述微分积分调制器向多模分频器输出分频控制字信号;

49、所述多模分频器根据所述分频控制字信号输出所述分频信号。

50、可选地,所述根据所述微分积分调制器发送的所述量化误差信号和所述相位域比较器发送的所述相位误差信号,向所述数字时间转换器输出控制信号,包括:

51、对所述量化误差信号进行提取,得到分段控制信号和残余误差信号;

52、利用n+1条查找表路径,根据所述分段控制信号和所述残余误差信号,得到每条所述查找表路径的输出值;

53、拟合所述n+1条查找表路径的输出值,得到所述控制信号。

54、可选地,所述根据所述量化误差信号,对所述量化误差信号进行提取,得到分段控制信号和残余误差信号,包括:

55、根据所述量化误差信号,进行量化处理,得到所述分段控制信号;

56、根据所述量化误差信号和所述分段控制信号,得到所述残余误差信号。

57、可选地,每条所述查找表路径包括:矫正参数提取模块和查找表模块;所述利用n+1条查找表路径,根据所述分段控制信号和所述残余误差信号,得到每条所述查找表路径的输出值,包括:

58、向所述矫正参数提取模块输入所述残余误差信号和所述相位误差信号,所述矫正参数提取模块根据所述相位误差信号和所述残余误差信号,提取矫正参数;

59、向所述查找表模块输入所述分段控制信号,所述查找表模块根据所述分段控制信号和所述矫正参数,得到输出值。

60、可选地,每条所述查找表路径的所述查找表模块包括m条通道,m为任意大于1的常数;每条通道表示所述数字时间转换器的非线性函数的一个区间,所述查找表模块根据所述分段控制信号和所述矫正参数,得到输出值,包括:

61、根据所述分段控制信号,从所述m条通道中确定出目标通道;

62、所述目标通道根据所述矫正参数,计算得到所述输出值。

63、可选地,所述方法还包括:

64、所述数字时间转换器向鉴相器发送所述调制后时钟信号;

65、所述多模分频器向所述鉴相器发送所述分频信号;

66、所述鉴相器根据所述调制后时钟信号和所述分频信号,输出误差信号;

67、滤波器对所述误差信号进行滤波,输出频率控制信号;

68、振荡器根据所述滤波器发送的所述频率控制信号调整输出信号的频率;

69、所述多模分频器对所述输出信号进行分频,得到所述分频信号。

70、本技术实施例提供了一种小数分频锁相环,所述锁相环包括:第一电路、参考时钟单元、数字时间转换器、相位域比较器、微分积分调制器和非线性矫正电路;所述第一电路包括:鉴相器、滤波器、振荡器和多模分频器;所述多模分频器和所述数字时间转换器的输出分别连接至所述相位域比较器;所述相位域比较器被配置用于根据所述多模分频器输出的分频信号,和,所述数字时间转换器输出的调制后时钟信号,输出相位误差信号;所述相位域比较器的输出连接至所述非线性矫正电路;所述微分积分调制器的输出连接至所述非线性矫正电路,所述微分积分调制器被配置用于向所述非线性矫正电路输出量化误差信号;所述非线性矫正电路的输出连接至所述数字时间转换器;所述非线性矫正电路被配置用于根据所述相位误差信号和所述量化误差信号,向所述数字时间转换器输出控制信号,以对所述数字时间转换器进行控制。本技术实施例在原有的模拟锁相环的电路结构(第一电路)基础上,增加相位域比较器和非线性矫正电路,利用相位域比较器提取相位误差信号,从而使非线性矫正电路能够根据该相位误差信号和量化误差信号,输出控制信号,对数字时间转换器进行实时控制,从而实现了,在锁相环的运行过程中,对数字时间转换器的增益和非线性进行矫正。并且,通过采集实时的相位误差信号,使生成的控制信号(数字时间转换器的控制字)自动适应于当前时刻的工艺、电源电压、温度等条件,能够自动进行相应调整,从而提升数字时间转换器工作的稳定性。

- 还没有人留言评论。精彩留言会获得点赞!