一种单电源供电的运算放大器及模拟集成电路的制作方法

本技术涉及模拟集成电路的,具体地涉及一种单电源供电的运算放大器及模拟集成电路。

背景技术:

1、目前运算放大器电路有单电源供电和双电源供电。双电源运算放大器电路其输入输出电压可以跨越正负电压,但基本都没有轨对轨能力,即输入电压范围正负对称,与正负电源电压有一定距离;输出电压范围正负对称,与正负电源电压有一定距离。而单电源供电运放电路对轨能力较好,即输入输出电压范围相比供电电源电压来说更大。输入从负电源起都可以实现线性放大、电路简单。

2、带有运算放大器的电子系统的工业趋势正朝着由电池电源提供的较低的工作电压的方向发展。这样,放大器在应用时,除了要求具有传统运算放大器的规定如高输入阻抗、低输入偏置电压、低噪声、宽带宽、高速度和充分的输出驱动能力以外,还要求低压单电源工作。虽然各种类型的输入级都由单电源电压源供电,但是放大器工作的低电压却因输入级的类型和集成电路的制造工艺而异。

3、轨到轨运算放大器是一种可以在共模电压范围(通常称为轨到轨的电压范围)内正常工作的运算放大器,轨到轨运算放大器可以用作模拟电路的输出缓冲级。但是传统的轨到轨运算放大器由于输出级晶体管本身存在阻抗,若有负载电流流过,输出级电压无法完全到参考电压,例如,当运算放大器的输入端的电压(参考电压)为零时,运算放大器输出无法达到零伏电压,这会导致后级处理电路引入较大的失调误差,需要进行系统上的校正,增加系统的复杂度和软硬件开销。如何解决输出晶体管导致的误差减小系统复杂度和软硬件开销是亟需解决的技术问题。

4、本背景技术描述的内容仅为了便于了解本领域的相关技术,不视作对现有技术的承认。

技术实现思路

1、因此,本发明实施例意图提供一种可以提供输出理想的轨到轨的电压的运算放大器。

2、在第一方面,本发明实施例提供了一种单电源供电的运算放大器,其特征在于,包括:

3、电源电压、电流源、偏置电压、pmos管、nmos管、电容、第一偏置电路、第二偏置电路以及参考电压,其中所述参考电压的阈值被预先设置为小于所述运算放大器能够输出的最小电压或者大于所述运算放大器能够输出的最大电压。

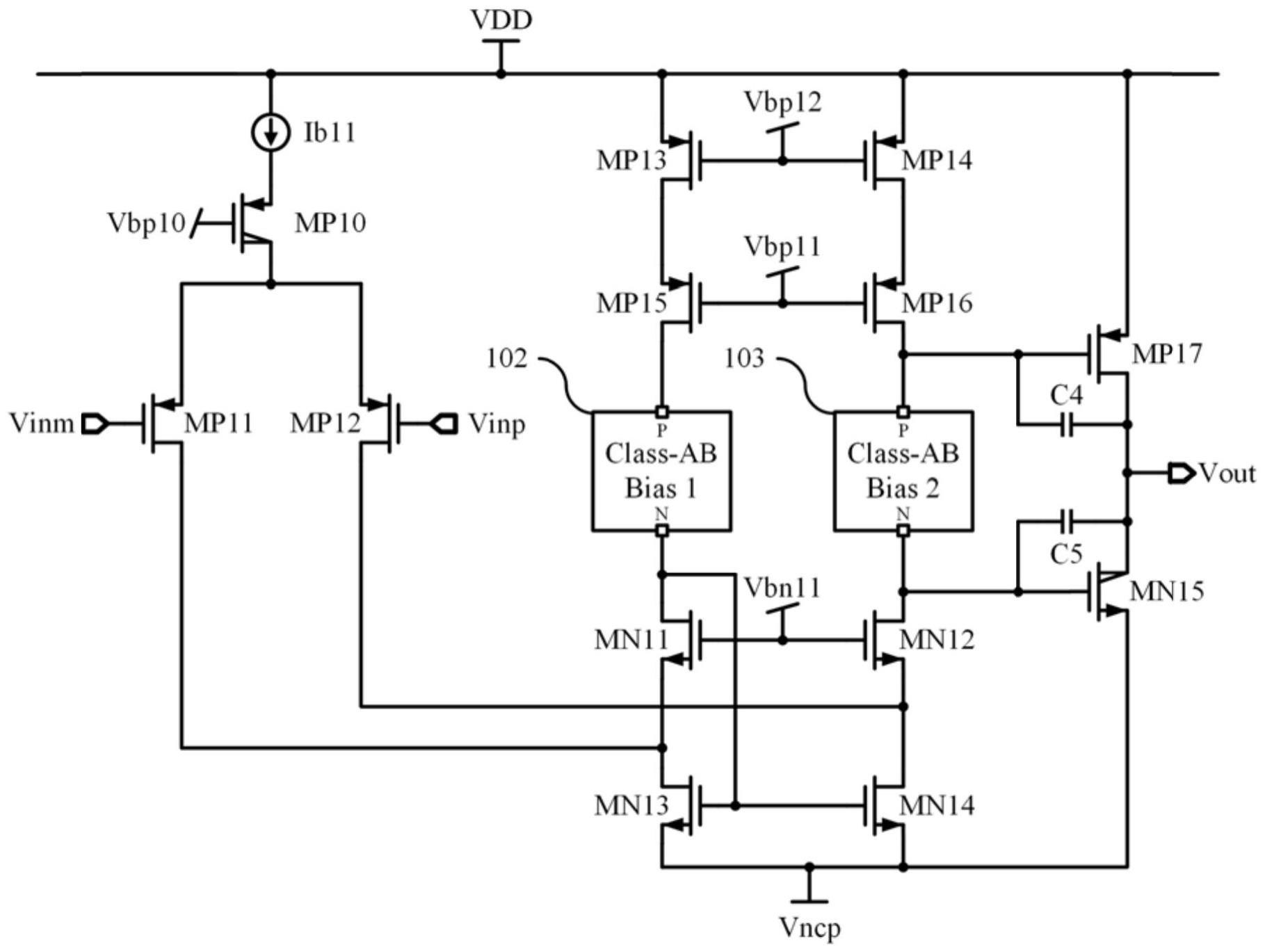

4、可选地,所述pmos管包括:第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第十五pmos管、第十六pmos管以及第十七pmos管;以及

5、所述nmos管包括:第十一nmos管、第十二nmos管、第十三nmos管、第十四nmos管以及第十五nmos管;所述偏置电压包括:第十p型栅极偏置电压、第十一p型栅极偏置电压、第十二p型栅极偏置电压以及第十一n型栅极偏置电压;所述电容包括:第四电容以及第五电容。

6、可选地,所述参考电压通过电荷泵电路产生,所述电荷泵电路包括:振荡器、分频器、时序产生电路、电容、输出电容、电阻以及开关控制电路。

7、可选地,所述电流源为第十一电流源,第十一电流源的一端连接至电源电压,另一端与所述第十pmos管的源极相连;

8、所述第十pmos管的栅极由所述第十p型栅极偏置电压偏置,所述第十pmos管的漏极和所述第十一pmos管的源极以及所述第十二pmos管的源极相连接。

9、可选地,所述第十一pmos管的栅极偏置电压为所述运算放大器的反相端输入电压;

10、所述第十二pmos管的栅极偏置电压为所述运算放大器的同相端输入电压。

11、可选地,所述第十一pmos管的漏极、所述第十三nmos管的漏极以及所述第十一nmos管的源极相连接;

12、所述第十二pmos管的漏极、所述第十四nmos管的漏极以及所述第十二nmos管的源极相连接;

13、所述第十三nmos管的源极、所述第十四nmos管的源极均与所述参考电压相连接,所述第十三nmos管的栅极、所述第十四nmos管的栅极均与所述第十一nmos管的漏极相连接;

14、所述第一偏置电路的一端连接至所述第十一nmos管的漏极;

15、所述第十二nmos管的漏极分别与所述第二偏置电路的一端、所述第五电容的一端以及所述第十五nmos管的栅极相连接;

16、所述第十一nmos管的栅极、所述第十二nmos管的栅极由所述第十一n型栅极偏置电压偏置;

17、所述第十五nmos管的源极连接至所述参考电压,所述第十五nmos管的漏极与所述第四电容的一端、所述第五电容的一端以及所述第十七pmos管的漏极连接在一起。

18、可选地,所述第十七pmos管的源极连接至所述电源电压,所述第十七pmos管的栅极与所述第四电容的一端、所述第二偏置电路的一端以及所述第十六pmos管的漏极相连接;

19、所述第十六pmos管的源极与所述第十四pmos管的漏极相连接,所述第十四pmos管的源极与所述电源电压相连接;

20、所述第十五pmos管的漏极与所述第一偏置电路的一端相连接,所述第十五pmos管的源极与所述第十三pmos管的漏极相连接,所述第十三pmos管的源极与所述电源电压相连接;以及

21、所述第十三pmos管的栅极、所述第十四pmos管的栅极均由所述第十二p型栅极偏置电压偏置,所述第十五pmos管的栅极、所述第十六pmos管的栅极均由所述第十一p型栅极偏置电压偏置。

22、可选地,所述开关控制电路包括:第十一开关、第十二开关、第十三开关、第十四开关、第二十一开关、第二十二开关、第二十三开关、第二十四开关、第一飞电容以及第二飞电容;以及

23、所述电阻包括:第十一电阻以及第十二电阻。

24、可选地,所述第十一开关的一端、所述第二十一开关的一端与输入电压相连接,所述第十二开关的一端、所述第二十二开关的一端与参考地gnd相连接;

25、所述第一飞电容的一端与所述第十一开关的一端以及所述第十三开关的一端相连接,所述第一飞电容的另一端与所述第十二开关的一端以及所述第十四开关的一端相连接;

26、所述第二飞电容的一端与所述第二十一开关的一端以及所述第二十三开关的一端相连接,所述第二飞电容的另一端与所述第二十二开关的一端以及所述第二十四开关的一端相连接;

27、所述第十三开关的另一端、所述第二十三开关的另一端与参考地gnd相连接;

28、所述第十四开关的另一端、所述第二十四开关的另一端与所述输出电容的一端以及所述第十二电阻的一端相连接,所述输出电容的另一端与参考地gnd相连接,所述第十二电阻的另一端与所述第十一电阻的一端、所述第十一电容的一端以及所述比较器的同相输入端连接,所述比较器的反相输入端与所述第十一电容的另一端连接到参考地gnd,所述第十一电阻的另一端同所述参考电压相连接;

29、所述比较器的输出连接至所述时序产生电路的置位端;

30、所述第十三开关、所述第十四开关、所述第二十一开关以及所述第二十二开关受所述时序产生电路的第一信号控制;

31、所述第十一开关、所述第十二开关、所述第二十三开关以及所述第二十四开关受所述时序产生电路的第二信号控制;

32、所述时序产生电路的第一信号与所述时序产生电路的第二信号相位相反。

33、在本发明实施例中,在第二方面,本发明实施例提供了一种模拟集成电路,其特征在于,所述模拟集成电路,使用如权利要求1-9中任一所述的运算放大器。

34、本发明实施例的其他可选特征和技术效果一部分在下文描述,一部分可通过阅读本文而明白。

- 还没有人留言评论。精彩留言会获得点赞!