宽输出电流范围的控制方法和实现电路与流程

本发明涉及led驱动电源,具体是宽输出电流范围的控制方法和实现电路。

背景技术:

1、在led调光照明应用中,希望led驱动电源的输出电流io能有宽范围变化来保证led输出光有宽范围变化。通常对led驱动开关电源而言,其输出电流是由led驱动开关电源中的输出电感电流的时间平均决定。对最小输出电流iomin时,led驱动开关电源中的输出电感电流il(t)已经进入断续模式。当输出最小输出电流iomin,这时led驱动开关电源中的输出电感电流il(t)的时间平均是由输出电感峰值电流ilpeak和输出电感重复开关周期ts确定。对最小的输出电感峰值电流ilpeak,最小输出电流iomin与输出电感重复开关周期ts成反比关系。要扩展输出电流变化范围,即减小输出电流iomin,从而使得重复开关周期ts进一步增加。为了避免led驱动电源出现音频噪音,led驱动开关电源的重复开关周期ts必须小于50us,即开关频率必须大于20khz。显然要保证led驱动开关电源的重复开关周期ts必须小于50us,即开关频率必须大于20khz,而输出电流iomin进一步减小的方向是进一步减小最小的输出电感峰值电流ilpeak;但是此导致的问题是电流比较器的最小分辨度、电流比较器的延迟响应时间以及消隐电路的限制而无法进一步减小最小的输出电感峰值电流ilpeak。因此需要提出一种进一步减小输出电感峰值电流ilpeak的可行方法。

技术实现思路

1、本发明要解决的技术问题是提供宽输出电流范围控制方法和实现电路,用以led驱动电源能够减小输出最小电感峰值电流ilpeak使得输出电流io能有宽范围变化,而使得开关频率可以始终高于音频频率。

2、为了解决上述技术问题,本发明提供一种宽输出电流范围控制方法,具体包括led驱动电源的输出电感电流的时间平均是由输出电感峰值电流ilpeak和输出电感重复开关周期ts确定,输出电感峰值电流ilpeak是通过调节电流参考电平vref的方式达到,输出电感峰值电流ilpeak值分为两段控制:其一是调节电流参考电平vref从最大值到零,而在这期间消隐时间是固定最大值;其二是当电流参考电平vref为零之后,保持电流参考电平vref为零,调节消隐时间从其固定最大值向最小值来使得输出电感峰值电流ilpeak值进一步减小。

3、作为本发明的宽输出电流范围的控制方法的改进:

4、所述电流参考电平vref和消隐时间的调节根据输出调光电流大小和开关频率大于音频频率与否要求进行;当输出调光电流大于预定电流时,如果电流参考电平vref大于零时,则减小电流参考电平vref;或如果电流参考电平vref已经为零,则减小消隐时间来减小实际输出调光电流;当对应的开关频率小于音频频率,如果电流参考电平vref大于零时,则进一步减小电流参考电平vref;或如果电流参考电平vref已经为零,则进一步减小消隐时间来保证开关频率大于音频频率。

5、本发明还同时提供了一种宽输出电流范围的控制方法的实现电路,包括:

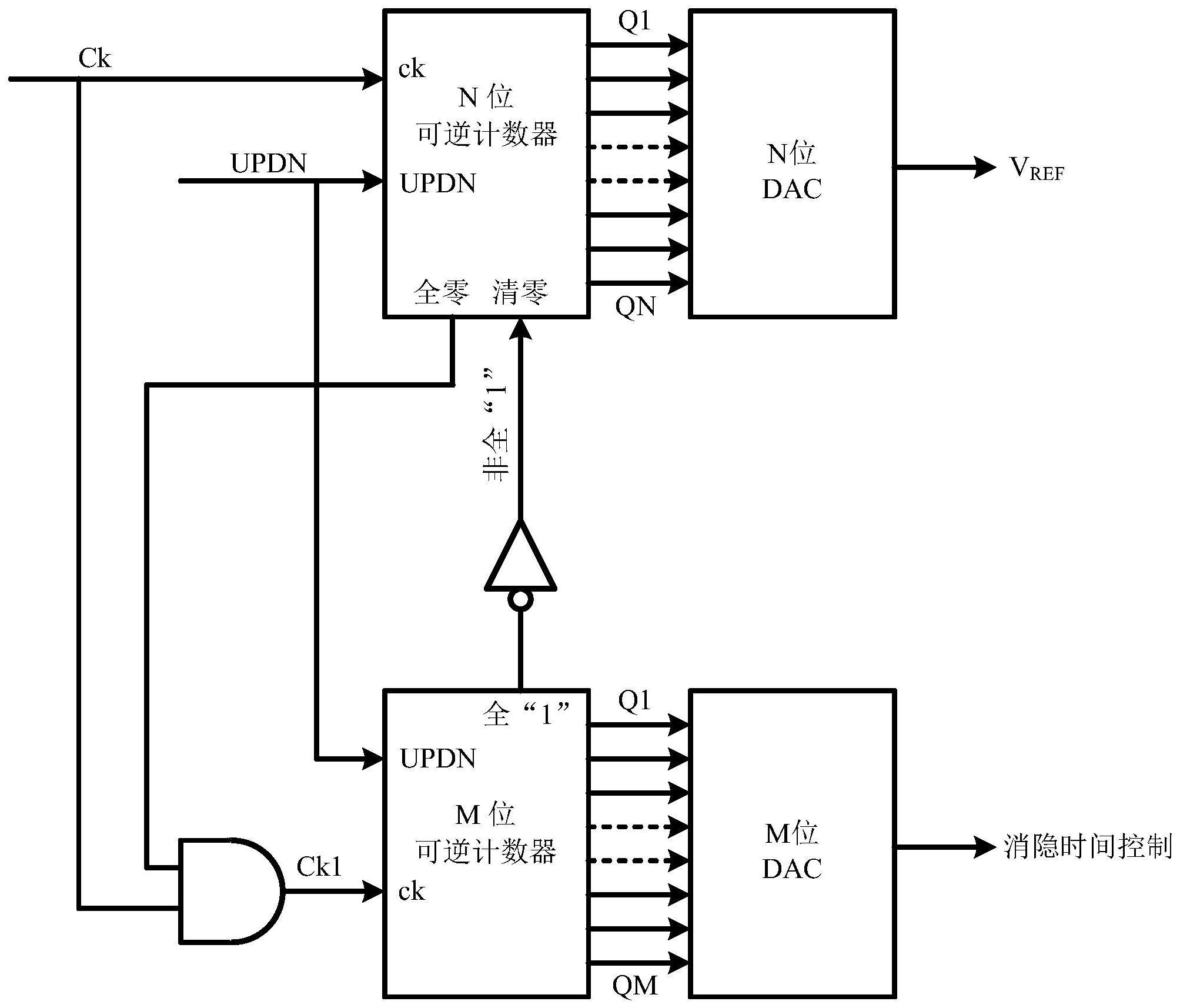

6、n位数字可逆加减计数器输出n位数字量和n位模数转换器dac的n位数字量输入端信号相连,m位数字可逆加减计数输出m位数字量和m位模数转换器dac的m位数字量输入端信号相连;n位模数转换器dac输出所述电流参考电平vref,m位模数转换器dac输出模拟电压用于控制所述消隐时间;

7、逻辑电平updn分别与n位数字可逆加减计数器的加减逻辑控制端updn、m位数字可逆加减计数器的加减逻辑控制端updn信号相连;时钟信号ck分别与n位数字可逆加减计数器的时钟ck输入端和逻辑与门的一个输入端信号相连,n位数字可逆加减计数器的全零输出逻辑端和逻辑与门的另一个输入端信号相连,逻辑与门的输出端ck1与m位数字可逆加减计数器的时钟ck输入端信号相连;m位数字可逆加减计数器的全“1”输出逻辑端经逻辑反相器与n位数字可逆加减计数器的清零置位端相连。

8、作为本发明的实现电路的改进:

9、所述逻辑电平updn为高电平时,随着对应时钟ck个数增加,电流参考电平vref模拟量和消隐时间模拟量增加;当逻辑电平updn为零电平,随着对应时钟ck个数增加,电流参考电平vref模拟量和消隐时间模拟量减小。

10、作为本发明的实现电路的进一步改进:

11、所述n位数字可逆加减计数器的清零置位端输出高电平时,保证电流参考电平vref达到零;

12、所述n位数字可逆加减计数器全零时,全零输出逻辑端输出高电平,所述逻辑与门导通,时钟信号ck经过所述逻辑与门进入m位数字可逆加减计数器。

13、作为本发明的实现电路的进一步改进:

14、所述m位数字可逆加减计数器为全“1”时,全“1”输出逻辑端为高电平,消隐时间达到固定最大值;所述m位数字可逆加减计数器非全“1”时,全“1”输出逻辑端为零电平,经逻辑反相器后变为高电平输入n位数字可逆加减计数器的清零置位端,即便有时钟ck,n位数字可逆加减计数器处于清零状态,直到m位可逆加减计数器全“1”时,n位可逆加减计数器根据updn逻辑电平进行可逆加减计数。

15、作为本发明的实现电路的进一步改进:

16、所述逻辑电平updn为零电平,如果n位数字可逆加减计数器或m位数字可逆加减计数器的初始状态为全“1”,消隐时间保持为固定最大时间,而电流参考电平vref自最大值随时钟ck个数增加而减小;当n位数字可逆加减计数器的数字量自全“1”减小到零,电流参考电平vref模拟量为零,由于n位数字可逆加减计数器的全零输出逻辑端输出高电平,m位数字可逆加减计数器有输入的时钟ck1;

17、对应的逻辑电平updn依旧为零电平,随时钟ck1个数增加,m位数字可逆加减计数器的数字量自全“1”减小到零,消隐时间模拟量达到最小值;当m位数字可逆加减计数器的数字量自全“1”减小时,m位可逆加减计数器的全“1”输出逻辑端输出零电平,经逻辑反相器使n位数字可逆加减计数器持续清零,对应输出电流参考电平vref模拟量保持为零。

18、作为本发明的实现电路的进一步改进:

19、所述逻辑电平updn为高电平,如果n位数字可逆加减计数器或m位数字可逆加减计数器的初始状态为全“0”,消隐时间为最小消隐时间,电流参考电平vref也为零;n位数字可逆加减计数器的全零输出逻辑端输出高电平,m位数字可逆加减计数器有输入的时钟ck1;随时钟ck1个数增加而增加,当m位数字可逆加减计数器的数字量自全“0”增加到全“1”,消隐时间模拟量自最小值增加到固定的最大值;在消隐时间模拟量自最小值增加到固定的最大值期间,m位可逆加减计数器的全“1”输出逻辑端输出高电平,经逻辑反相器使n位数字可逆加减计数器的清零置位端输入为零电平,n位数字可逆加减计数器清零结束,对应输出电流参考电平vref模拟量保持为零;

20、对应的逻辑电平updn依旧为高电平,随时钟ck个数增加,n位数字可逆加减计数器的数字量自全“0”增加到全“1”,电流参考电平vref模拟量自零增加到最大值;当n位数字可逆加减计数器的数字量非全“0”时,n位数字可逆加减计数器的全零输出逻辑端输出零电平使m位数字可逆加减计数器的时钟ck1消失,对应消隐时间模拟量保持为固定最大时间。

21、本发明的有益效果主要体现在:

22、1、本发明通过两段式调节输出电感峰值电流ilpeak值实现驱动电源的宽范围电流输出而使得开关频率可以始终高于音频频率。

23、2、本发明通过两段式调节输出电感峰值电流ilpeak值方法,即分别控制参考电流电平和消隐时间可以大大降低电流比较器的分辨度和延迟时间的要求;在消隐时间控制中,电流比较器已经不参与对输出电感峰值电流ilpeak值进行控制而是完全由消隐时间控制电路控制。

- 还没有人留言评论。精彩留言会获得点赞!