时钟校准电路的制作方法

本发明涉及半导体集成电路,具体地,涉及一种时钟校准电路。

背景技术:

1、集成电路在工作的时候,往往需要一个稳定的时钟。振荡器是系统必须的一个关键部件,能够给集成电路提供工作时钟。很多电子设备为了设计方便和节约成本,普遍使用内部的时钟振荡器作为时钟信号源。然而由于现有集成电路制造工艺的限制,芯片内部的时钟振荡器产生的时钟信号通常有±20%到±30%的偏差,有些工艺甚至可能产生±50%的偏差,这种具有巨大偏差的时钟信号如果直接用于内部电路,将极有可能使系统处于不稳定或不可预知的状态,无法正常工作。

2、针对芯片内部的时钟振荡器产生的时钟信号存在较大偏差的问题,通常采用配置内部的校准寄存器的方法来调整时钟信号的频率,例如,通过修调电路对可配置基准电流源进行调整,从而改变时钟振荡电路输出的时钟信号的频率。修调电路的校准值根据输出时钟信号的频率进行调整,通过多轮调整后才能得到符合要求的时钟信号。该种方法实现简单,但由于需要对时钟信号进行测量并调整校准值,因此整个校准过程耗费时间较长,测试成本较多。

技术实现思路

1、鉴于上述内容,本发明的目的在于提供一种时钟校准电路,能够实现电路本身的自动校准,不需要太多人工干预,降低了芯片测试环节的技术难度,同时能够降低测试成本。

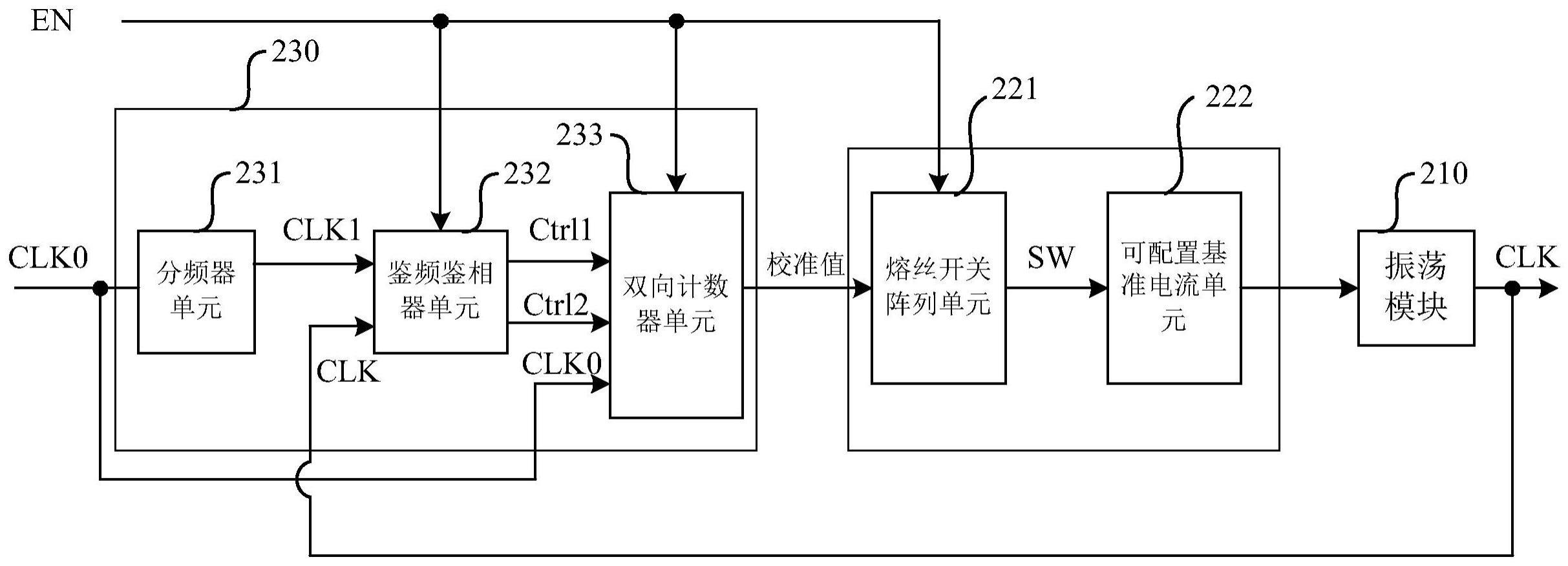

2、根据本发明的第一方面,提供一种时钟校准电路,包括:振荡模块,用于根据基准电流产生输出时钟信号;基准模块,用于根据校准使能信号以及校准值产生基准电流;校准模块,用于对参考时钟信号进行分频得到分频时钟信号,并对分频时钟信号的频率与输出时钟信号的频率进行比较以产生计数控制信号,根据所述计数控制信号对参考时钟周期内输出时钟信号的脉冲个数进行计数以得到校准值;其中,所述校准值为分频时钟信号的频率与输出时钟信号的频率相同时参考时钟周期内输出时钟信号的脉冲个数。

3、优选地,所述校准模块包括:分频器单元,用于对参考时钟信号进行分频处理以产生分频时钟信号;鉴频鉴相器单元,用于对分频时钟信号和输出时钟信号的频率进行比较以产生计数控制信号;双向计数器单元,用于根据所述计数控制信号对参考时钟周期内输出时钟信号的脉冲个数进行计数以得到校准值。

4、优选地,计数控制信号包括第一控制信号和第二控制信号,当所述输出时钟信号的相位超前所述分频时钟信号的相位时,第一控制信号为有效电平矩形脉冲,第二控制信号为无效电平,第一控制信号的脉冲宽度由所述输出时钟信号和所述分频时钟信号之间的相位差对应;当所述分频时钟信号的相位超前所述输出时钟信号的相位时,第二控制信号为有效电平矩形脉冲,第一控制信号为无效电平,第二控制信号的脉冲宽度由所述输出时钟信号和所述分频时钟信号之间的相位差对应;当所述分频时钟信号的相位和所述输出时钟信号的相位相同,第一控制信号和第二控制信号均为无效电平。

5、优选地,当所述输出时钟信号的频率小于所述分频时钟信号的频率时,第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度;当所述输出时钟信号的频率大于所述分频时钟信号的频率时,第二控制信号的脉冲宽度大于所述第一控制信号的脉冲宽度。

6、优选地,当第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度时,所述双向计数器单元对参考时钟周期内输出时钟信号的脉冲个数进行加法计数直至第一控制信号变为无效电平停止计数。

7、优选地,当第二控制信号的脉冲宽度大于所述第一控制信号的脉冲宽度时,所述双向计数器单元对参考时钟周期内输出时钟信号的脉冲个数进行减法计数直至第二控制信号变为无效电平停止计数。

8、优选地,当所述双向计数器单元停止计数时,校准使能信号从无效电平变为有效电平。

9、优选地,所述基准模块包括:熔丝开关阵列单元,根据校准使能信号将校准值存储为熔丝开关阵列状态,从而产生多个开关控制信号;可配置基准电流单元,根据多个开关控制信号产生基准电流。

10、优选地,双向计数器单元包括:逻辑门,用于将所述第一控制信号和所述参考时钟信号以产生第一计数脉冲或所述第二控制信号和所述参考时钟信号进行逻辑运算以产生第二计数脉冲;第一计数器,用于根据所述第一计数脉冲进行计数以得到第一计数值;第二计数器,用于根据所述第二计数脉冲进行计数以得到第二计数值;数值寄存器,用于将第一计数值和第二计数值中的一个存储作为校准值。

11、优选地,当第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度时,所述第一计数器根据所述第一计数脉冲进行加法计数以得到第一计数值;当第二控制信号的脉冲宽度大于所述第一控制信号的脉冲宽度时,所述第二计数器根据所述第二计数脉冲进行减法计数以得到第二计数值。

12、优选地,当所述第一计数脉冲和所述第二计数脉冲的脉冲个数小于预设值时,所述第一计数器和所述第二计数器停止计数,所述数值寄存器将第一计数值和第二计数值中的一个存储作为校准值。

13、本发明实施例提供的时钟校准电路,通过外部的参考时钟信号与输出时钟信号的频率进行比较以产生校准值,根据校准值对振荡模块的基准电流进行调节校准,以得到所需频率的输出时钟信号,能够实现电路本身的自动校准,不需要太多人工干预,降低了芯片测试环节的技术难度,同时能够降低测试成本。

14、进一步地,通过分频器对参考时钟信号进行分频得到分频时钟信号,对分频时钟信号和输出时钟信号进行频率比较以产生计数控制信号,根据计数控制信号进行加法或者减法计数以得到校准值。

15、进一步地,采用熔丝开关阵列单元对校准值进行存储,形成能够掉电保持的数据,提高校准精度。

技术特征:

1.一种时钟校准电路,其特征在于,包括:

2.根据权利要求1所述的时钟校准电路,其特征在于,所述校准模块包括:

3.根据权利要求2所述的时钟校准电路,其特征在于,计数控制信号包括第一控制信号和第二控制信号,

4.根据权利要求3所述的时钟校准电路,其特征在于,当所述输出时钟信号的频率小于所述分频时钟信号的频率时,第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度;

5.根据权利要求4所述的时钟校准电路,其特征在于,当第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度时,所述双向计数器单元对参考时钟周期内输出时钟信号的脉冲个数进行加法计数直至第一控制信号变为无效电平停止计数。

6.根据权利要求4所述的时钟校准电路,其特征在于,当第二控制信号的脉冲宽度大于所述第一控制信号的脉冲宽度时,所述双向计数器单元对参考时钟周期内输出时钟信号的脉冲个数进行减法计数直至第二控制信号变为无效电平停止计数。

7.根据权利要求5或6所述的时钟校准电路,其特征在于,当所述双向计数器单元停止计数时,校准使能信号从无效电平变为有效电平。

8.根据权利要求1所述的时钟校准电路,其特征在于,所述基准模块包括:

9.根据权利要求3所述的时钟校准电路,其特征在于,双向计数器单元包括:

10.根据权利要求9所述的时钟校准电路,其特征在于,当第一控制信号的脉冲宽度大于所述第二控制信号的脉冲宽度时,所述第一计数器根据所述第一计数脉冲进行加法计数以得到第一计数值;当第二控制信号的脉冲宽度大于所述第一控制信号的脉冲宽度时,所述第二计数器根据所述第二计数脉冲进行减法计数以得到第二计数值。

11.根据权利要求10所述的时钟校准电路,其特征在于,当所述第一计数脉冲和所述第二计数脉冲的脉冲个数小于预设值时,所述第一计数器和所述第二计数器停止计数,所述数值寄存器将第一计数值和第二计数值中的一个存储作为校准值。

技术总结

本申请公开了一种时钟校准电路,包括:振荡模块,用于根据基准电流产生输出时钟信号;基准模块,用于根据校准使能信号以及校准值产生基准电流;校准模块,用于对参考时钟信号进行分频得到分频时钟信号,并对分频时钟信号的频率与输出时钟信号的频率进行比较以产生计数控制信号,根据所述计数控制信号对参考时钟周期内输出时钟信号的脉冲个数进行计数以得到校准值;其中,所述校准值为分频时钟信号的频率与输出时钟信号的频率相同时参考时钟周期内输出时钟信号的脉冲个数。本申请能够实现电路本身的自动校准,不需要太多人工干预,降低了芯片测试环节的技术难度,同时能够降低测试成本。

技术研发人员:蔡俊

受保护的技术使用者:上海赛鹰微电子有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!