一种板内集成3D打印叠层电容的方法与流程

本发明属于电路板电容集成制造,具体涉及一种板内集成3d打印叠层电容。

背景技术:

1、电容作为电子线路中常用的电器元件,一般具有旁路、去耦、滤波、储能等方面的应用。随着电路集成化进一步发展,埋阻埋容也成为一大发展趋势。除了半导体集成电路外,现有的高频电容都是通过独立封装后以焊接的方式集成于电路板上,大体积的电容往往在板面上占据较大的安装空间,且在焊接管脚易引起寄生电容、电阻及电感现象。在半导体集成电路中由于尺寸关系电容容量都很小,这也限制其在射频电路中电磁兼容的能力。通常需要通过增加射频信号吸收单元进行改善,这将会增加制造过程的复杂程度。

2、目前,印制板行业所采用的板内埋容仍是以芯材刻蚀或者丝网印刷浆料的方式,而电容芯板材料由于较薄蚀刻及铺层褶皱、气孔等导致质量控制极为困难,而采用丝网印刷形成电容的容量精度难以控制且易出现分层现象。此外还有采用空腔嵌置焊接电容器件的方式,导致板厚增大且并不能消除焊接引起的寄生电容电感等现象。

3、近些年随着3d打印技术的普及,也出现了相关3d打印电容相关的报道。如:中国专利cn104461188b采用3d打印搭桥结构方式解决了电容屏的制造,简化了现有曝光显影及蚀刻的工序,但其适用于面积较大的单层电容制造。中国专利cn106738855b主要通过制备了水凝胶材料,通过打印方式制备多孔凝胶离子传导层实现了电容式智能皮肤,仅适用于触摸、皮肤感知方面的应用,但其不适用于商业化制造及集成。中国专利申请cn109637819a主要通过印刷或者打印石墨烯、碳纳米管及导电聚合物等方式形成平面电容的制备,仅适用于触摸屏等较大面积时的应用场合,而并不具有代替现有集成电路上电容的潜能。中国专利申请cn113555230a主要通过熔融沉积的方式打印出高分子模具,采用滴涂银浆而形成平面叉指形电容,其仅仅实现了电容功能,但精度控制和集成方面不具有商业化应用价值。中国专利申请cn113725002a主要通过dlp(digital light processing,数字光处理)工艺及电镀工艺形成陶瓷电容,在不变体积的情况下增加了电容容量,但后续仍需要通过焊接的方式集成至电路板上。中国专利申请cn114121502a主要通过制备含石墨烯的光固化树脂,通过dlp及sla(stereo lithography appearance,立体光固化成型法)等工艺形成叉指电极,通过与电解质组合形成超级电容,其电极需要气氛保护脱脂以提升电极导电率,成本较高且后续需要二次组装及如何集成至商业化电路板中成为难题。中国专利申请cn102543426a采用喷墨工艺成型了介质材料和导电种子层,后续仍需要采用电镀工序进行电极的增厚,且均匀喷涂的大面积介电层可能在后续会造成分离现象,同时该工艺方案并没有介绍上下层电极互联及板内封装工艺、电容精度等。

4、通过以上专利文献可以看出,现有3d打印电容通常为单层叉指形平板电容或者只是打印电容电极以及通过沟槽填充封装后形成单个电容结构,但是其形成的单体电容精度难以控制,且后续仍需要通过焊接方式集成于电路板上。此外3d打印制造的平板电容的尺寸均较大且所采用的材料在没有刚性材料封装的情况下,很难灵活集成于现有的电子线路板中,因此并不适用于商业化的制造。

5、因此,鉴于商业应用需求,有必要提出一种板内集成电容的方式。

技术实现思路

1、本发明目的在于解决现有3d打印电容通常为单层叉指形平板电容或者只是打印电容电极以及通过沟槽填充封装后形成单个电容结构,其形成的单体电容精度难以控制,很难灵活集成于现有的电子线路板中的不足之处,而提供一种板内集成3d打印叠层电容的方法。

2、为实现上述目的,本发明所提供的技术解决方案是:

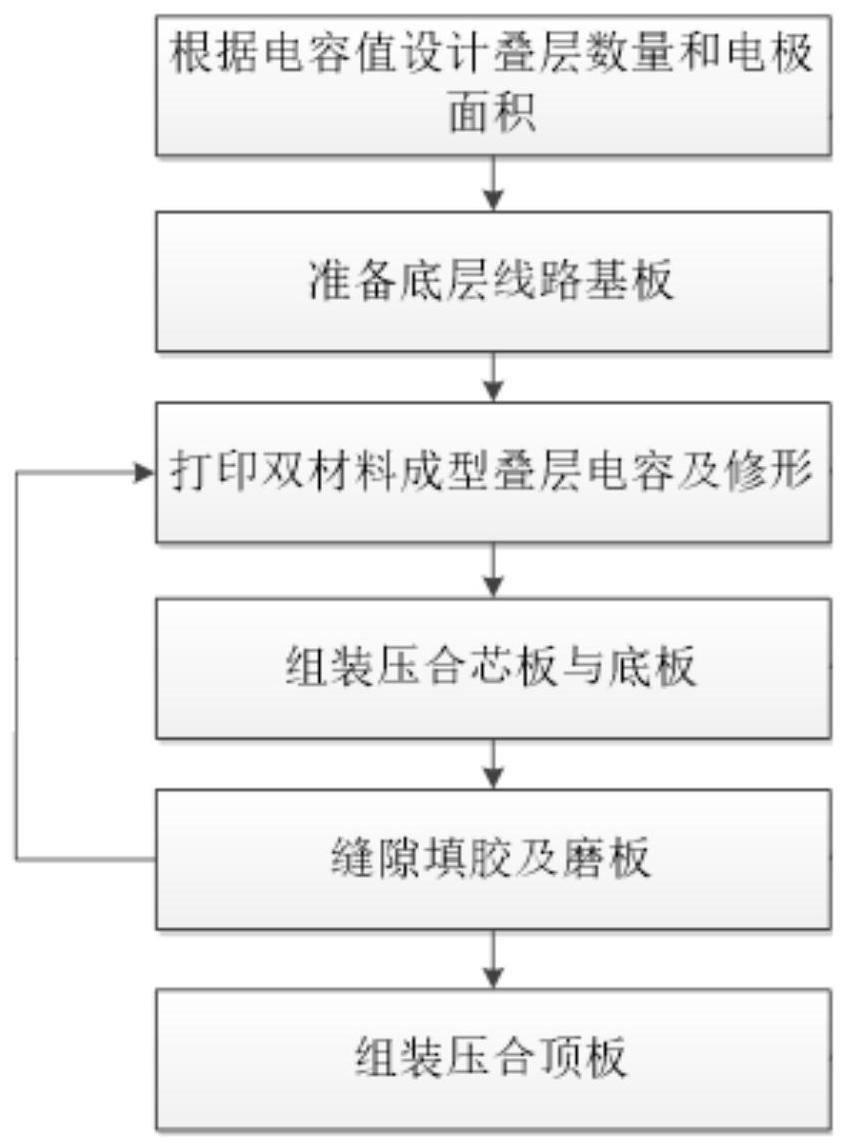

3、一种板内集成3d打印叠层电容的方法,其特殊之处在于,包括以下步骤:

4、1)根据电子线路板中对于电容容值、体积大小的要求以及所选取打印介质材料的介电常数,按照如下板式电容公式设计叠层片式电容电极大小以及层数和层间距:

5、c=ε0×ε×a/d×(n-1)

6、其中,ε0-真空介电常数,8.854×10-12f/m,ε-所选取打印介质材料的介电常数,a-电极面积,d-上下电极之间介质层厚度,n-电极层数;

7、2)根据步骤1)的设计结果在底层电子线路基板上预留电容的位置区域上打印叠层片式电容;打印的电容高度小于中间芯板预留槽深度0.3mm以上,留出封装层厚度;

8、其中,多层电极之间的互联通过打印垂直壁体实现,所述垂直壁体下端通过打印导电线路与底层电子线路基板上预留的导电线路形成连接;

9、底层电子线路基板也是预先准备好的,其上预留打印电容位置,该位置区域处设置有位置标识符以及连接电容的导电线路;

10、在电容打印过程中及打印完成后,需在电容周围打印封装层;

11、3)完成对打印电容的封装后,对电容外侧的封装层进行加工,确保电容四周与中间层线路芯板上预留槽四周安装间隙在0.05~0.2mm,电容顶部(此时包含顶部封装层)低于中心嵌入预留槽深度0.1mm以上;

12、4)组装带有电容的底层电子线路基板和中间层线路芯板,真空热压工艺成型后采用填胶方式填充缝隙,并去除残留胶体确保配合面平整,以保证后续与顶层电路板的组装精度;

13、5)将顶层电路板与步骤4)所得产品进行组装,完成板内集成3d打印叠层电容。

14、进一步地,步骤2)具体为:

15、2.1)在电容底部预先打印导电墨水沉积于底层电子线路基板形成导电线路,其一端连接底层电子线路基板上预留的导电线路,另一端连接电容垂直互联结构底部引脚,在固化后达到电性能连通效果;

16、2.2)在打印导电线路及垂直壁体底部引脚周围填充打印介质墨水,与已沉积的导电线路形成齐平结构,即导电线路嵌入在介质层中,导电线路表面与介质表面齐平;

17、2.3)按照步骤1)设计厚度分别打印导电层(即电极层)和介质层形成叠层电容结构(分别使用的导电墨水和介质墨水),所形成的电容高度小于中间芯板预留槽深度0.3mm以上,留出封装层厚度;

18、在打印过程中及打印完成后,需在电容周围打印封装层。

19、进一步地,步骤2.1)中,打印的导电线路厚度大于底层电子线路基板上预留的导电线路厚度,并在对接位置形成搭接结构,以达到良好的连接效果。

20、进一步地,步骤2)中,导电墨水采用纳米银/铜/金/钯或石墨烯/碳纳米管;介质墨水采用聚亚酰胺、聚砜醚酮、丙烯酸、二氧化钛或钛酸钡;打印材料选用此类可光固成型的材料,选用紫外、激光或者氙灯等方式便可达到快速固化的效果;打印方式为压电喷墨、气溶胶喷射、电流体喷印等可打印低粘度墨水技术,便于沉积层厚度的精确控制。

21、封装层的材料为介质墨水或封装用树脂材料;

22、封装层的打印方式为压电喷射阀或点胶等喷印高粘度材料的方式,以提升封装效率;

23、进一步地,步骤3)中,封装层的后续加工采用精密铣削工艺。

24、进一步地,步骤4)中,组装带有电容的底层电子线路基板和中间层线路芯板时,粘接面使用半固化片式胶膜,采用真空热压工艺成型;在电容与中间层线路芯板槽四周间隙内,填充可压缩弹性胶体材料以缓冲中间层线路芯板与打印电容体在热环境下由于膨胀系数差异带来的应力冲击,稳定电容性能;

25、填充时,采用可压缩弹性胶体材料。

26、进一步地,步骤5)中,采用真空热压工艺顶层电路板与步骤4)所得产品组装成型。

27、本发明还提供了一种电子元件,其特殊之处在于:该电子元件中电容采用上述方法集成在板内。

28、本发明的原理:

29、本发明首先根据实际电子线路中对于电容容值的需要以及集成区域所允许的面积大小,按照叠层片式电容公式计算出所需要打印电容的层数。通过在底层电子线路基板上预留电容区域打印叠层片式电容,其中,电容电极通过打印垂直壁体实现多层电极之间的互联,此外垂直壁体下端引脚通过打印导线与底层电子线路基板上的预留导线形成连接,避免了电容的焊接过程。在电容打印完成后,中间层线路芯板采用胶膜与带电容的底层电子线路基板进行真空热压成型。随后采用填胶方式对电容和中间层线路芯板槽之间的缝隙进行填充,通过磨板的方式保证填胶面的平整度,最终通过与顶层电路板装配热压成型形成板内3d打印电容的集成。

30、本发明的优点是:

31、1.本发明实现了电容在电路板内的集成,为板面上留出更多的安装空间,提高印制电路集成度。

32、2.本发明可根据需求通过控制打印层数和面积,可以准确实现电容大小的调控。

33、3.本发明打印电容可一次成型,工序简单,避免了传统刻蚀、叠层压合等多道工序,且可靠性更高。

34、4.本发明方法内置电容时避免了焊接工序,消除了管脚焊接引起的寄生电容、电感及电阻等,最小化等效电阻和电感,有助提升电路的电磁兼容性。

35、5.本发明板内电容集成方法,易于实现,有利于商业化推广,且采用本方法形成的电容容值误差精度小于10%。

- 还没有人留言评论。精彩留言会获得点赞!