SRAM及其制作方法与流程

本申请涉及半导体,具体而言,涉及一种sram(static random-accessmemory,静态随机存取存储器)及其制作方法。

背景技术:

1、sram读操作和写操作时,需要pg(pass gate,控制开关)的饱和电流(idsat)大小不同,来保证sram在读和写操作过程的噪声容限。现有的sram结构无法满足读写时不同的idsat要求,从而造成了sram的抗干扰性较差。

2、在背景技术部分中公开的以上信息只是用来加强对本文所描述技术的背景技术的理解,因此,背景技术中可能包含某些信息,这些信息对于本领域技术人员来说并未形成在本国已知的现有技术。

技术实现思路

1、本申请的主要目的在于提供一种sram及其制作方法,以解决现有sram结构读写过程的噪声容限较低,导致抗干扰能力较差的问题。

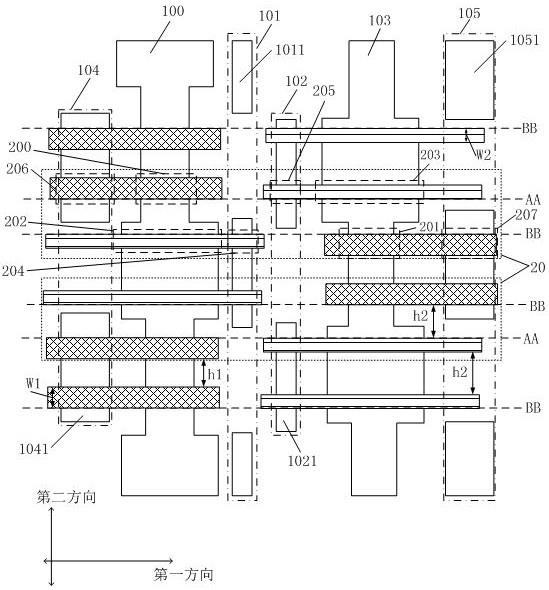

2、为了实现所述目的,根据本申请的一个方面,提供了一种sram,包括有源区以及多个sram单元,所述sram单元包括第一下拉管、第一上拉管、第一控制开关、第二下拉管、第二上拉管以及第二控制开关,其中,所述第一下拉管的源区或者漏区与所述第一控制开关的源区或者漏区接触,所述第一下拉管与所述第一上拉管共用栅极,所述第二下拉管的源区或者漏区与所述第二控制开关的源区或者漏区接触,所述第二下拉管与所述第二上拉管共用栅极,所述有源区包括沿第一方向间隔排列的第一区域、第二区域、第三区域以及第四区域;多个所述sram单元沿第二方向在所述有源区上排列,且相邻的两个所述sram单元沿所述第一方向镜像对称,所述第一方向垂直于所述第二方向;其中,所述第一下拉管和所述第一控制开关沿所述第二方向在所述第一区域中排列,所述第一上拉管位于所述第二区域中,所述第二上拉管位于所述第三区域中,所述第二下拉管和所述第二控制开关沿所述第二方向在所述第四区域中排列;相邻两个所述第一控制开关的栅极之间的距离以及相邻两个所述第二控制开关的栅极之间的距离均为第一距离,所述sram单元中,所述第一控制开关与所述第一下拉管的栅极之间的距离以及所述第二控制开关与所述第二下拉管的栅极之间的距离均为第二距离,所述第二距离大于所述第一距离。

3、可选地,相邻两个所述第一下拉管的栅极之间的距离以及相邻两个所述第二下拉管的栅极之间的距离分别为所述第二距离。

4、可选地,所述第一控制开关的栅极为第一栅极,所述第二控制开关的栅极为第二栅极,所述第一栅极以及所述第二栅极的宽度为第一宽度,所述第一下拉管的栅极为第三栅极,所述第二下拉管的栅极为第四栅极,所述第三栅极以及所述第四栅极的宽度为第二宽度,所述第一宽度大于所述第二宽度,宽度方向平行于所述第二方向,所述第一栅极的靠近所述第三栅极的表面为第一表面,所述第四栅极的靠近所述第二栅极的表面为第二表面,所述第一表面与所述第二表面位于同一平面,所述第三栅极靠近所述第一栅极的表面为第三表面,所述第二栅极靠近所述第四栅极的表面为第四表面,所述第三表面与所述第四表面位于同一平面。

5、可选地,所述有源区还包括第五区域以及第六区域,所述第五区域位于所述第一区域的远离所述第二区域的一侧,所述第六区域位于所述第四区域的远离所述第三区域的一侧,所述sram单元还包括第三控制开关以及第四控制开关,所述第三控制开关位于所述第五区域中,所述第四控制开关位于所述第六区域中,所述第三控制开关与所述第一控制开关共用栅极,所述第四控制开关与所述第二控制开关共用栅极。

6、可选地,所述第二区域包括沿所述第二方向间隔排列的多个第一子区域,相邻的两个所述sram单元中的所述第一上拉管位于同一个所述第一子区域中,所述第三区域包括沿所述第二方向间隔排列的多个第二子区域,相邻的两个所述sram单元中的所述第二上拉管位于同一个所述第二子区域中。

7、可选地,相邻的两个所述第一下拉管的栅极之间的距离以及相邻的两个所述第二下拉管的栅极之间的距离均为第三距离,所述第三距离大于所述第一距离且小于所述第二距离。

8、可选地,所述第一控制开关、所述第二控制开关、所述第一上拉管、所述第二上拉管、所述第一下拉管以及所述第二下拉管的栅极的宽度均相同,宽度方向平行于所述第二方向。

9、根据本申请的另一方面,提供了一种sram的制作方法,包括:对任一种所述的sram的第一下拉管、第一上拉管、第一控制开关、第二下拉管、第二上拉管以及第二控制开关对应的源区和漏区进行离子注入,其中,所述源区以及所述漏区的面积与注入浓度成正比,得到最终sram结构。

10、可选地,对第一上拉管、第一控制开关、第二下拉管、第二上拉管以及第二控制开关对应的源区和漏区进行离子注入,包括:在所述第一上拉管以及所述第二上拉管的表面上形成第一掩膜结构;对覆盖有所述第一掩膜结构的所述sram进行离子注入,以对所述第一控制开关、所述第二控制开关、所述第一下拉管以及所述第二下拉管的所述源区和所述漏区进行掺杂;在所述第一控制开关、所述第一下拉管、所述第二控制开关以及所述第二下拉管的表面上形成第二掩膜结构;对覆盖有所述第二掩膜结构的所述sram进行离子注入,以对所述第一上拉管以及所述第二上拉管的源区和所述漏区进行掺杂。

11、可选地,所述离子注入为晕环(halo)离子注入。

12、应用本申请的技术方案,本申请可以达到的意料不到的技术效果包括:

13、1、所述的sram中,相邻的两个第一控制开关(或第二控制开关)共用的源区或者漏区为第一掺杂区域,第一控制开关(或第二控制开关)与相邻的第一下拉管(或第二下拉管)共用的源区或者漏区为第二掺杂区域,第二掺杂区域的表面积大于第一掺杂区域的表面积,这样后续通过现有制造工艺对本申请的所述sram进行离子注入时,相同的离子注入条件下可以使得第二掺杂区域的掺杂浓度大于第一掺杂区域的掺杂浓度,实现了第一控制开关(或第二控制开关)源端和漏端的非对称性。

14、2、由于第二掺杂区域的掺杂浓度大于第一掺杂区域的掺杂浓度,这样在不改变sram的制作工艺的情况下,制作得到的sram在执行读操作时,第一掺杂区域流向第二掺杂区域的电流小,可以保证读操作时sram的噪声容限较高,这样在进行读操作时,sram的噪声容限较高,保证了sram的整体抗干扰能力较强。

15、3、在执行写操作时,第二掺杂区域流向第一掺杂区域的电流大,可以保证写操作时sram的噪声容限较高,保证了sram的整体抗干扰能力较强。

技术特征:

1.一种sram,包括有源区以及多个sram单元,所述sram单元包括第一下拉管、第一上拉管、第一控制开关、第二下拉管、第二上拉管以及第二控制开关,其中,所述第一下拉管的源区或者漏区与所述第一控制开关的源区或者漏区接触,所述第一下拉管与所述第一上拉管共用栅极,所述第二下拉管的源区或者漏区与所述第二控制开关的源区或者漏区接触,所述第二下拉管与所述第二上拉管共用栅极,其特征在于,

2.根据权利要求1所述的sram,其特征在于,相邻两个所述第一下拉管的栅极之间的距离以及相邻两个所述第二下拉管的栅极之间的距离分别为所述第二距离。

3.根据权利要求2所述的sram,其特征在于,所述第一控制开关的栅极为第一栅极,所述第二控制开关的栅极为第二栅极,所述第一栅极以及所述第二栅极的宽度为第一宽度,所述第一下拉管的栅极为第三栅极,所述第二下拉管的栅极为第四栅极,所述第三栅极以及所述第四栅极的宽度为第二宽度,所述第一宽度大于所述第二宽度,宽度方向平行于所述第二方向,

4.根据权利要求1至3中任一项所述的sram,其特征在于,所述有源区还包括第五区域以及第六区域,所述第五区域位于所述第一区域的远离所述第二区域的一侧,所述第六区域位于所述第四区域的远离所述第三区域的一侧,所述sram单元还包括第三控制开关以及第四控制开关,所述第三控制开关位于所述第五区域中,所述第四控制开关位于所述第六区域中,所述第三控制开关与所述第一控制开关共用栅极,所述第四控制开关与所述第二控制开关共用栅极。

5.根据权利要求1至3中任一项所述的sram,其特征在于,所述第二区域包括沿所述第二方向间隔排列的多个第一子区域,相邻的两个所述sram单元中的所述第一上拉管位于同一个所述第一子区域中,所述第三区域包括沿所述第二方向间隔排列的多个第二子区域,相邻的两个所述sram单元中的所述第二上拉管位于同一个所述第二子区域中。

6.根据权利要求1所述的sram,其特征在于,相邻的两个所述第一下拉管的栅极之间的距离以及相邻的两个所述第二下拉管的栅极之间的距离均为第三距离,所述第三距离大于所述第一距离且小于所述第二距离。

7.根据权利要求6所述的sram,其特征在于,所述第一控制开关、所述第二控制开关、所述第一上拉管、所述第二上拉管、所述第一下拉管以及所述第二下拉管的栅极的宽度均相同,宽度方向平行于所述第二方向。

8.一种sram的制作方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,对第一上拉管、第一控制开关、第二下拉管、第二上拉管以及第二控制开关对应的源区和漏区进行离子注入,包括:

10.根据权利要求9所述的方法,其特征在于,所述离子注入为晕环离子注入。

技术总结

本申请提供了一种SRAM及其制作方法,该SRAM中,有源区包括沿第一方向间隔排列的第一区域、第二区域、第三区域以及第四区域;SRAM单元沿第二方向在有源区上排列,相邻两个SRAM单元沿第一方向镜像对称,第一方向垂直于第二方向;第一下拉管和第一控制开关沿第二方向在第一区域中排列,第二下拉管和第二控制开关沿第二方向在第四区域中排列;相邻两个第一控制开关(或第二控制开关)的栅极之间的距离为第一距离,SRAM单元中,第一控制开关(或第二控制开关)与第一下拉管(或第二下拉管)的栅极之间的距离为第二距离,第二距离大于第一距离。本申请在不改变现有工艺的情况下,提升了SRAM读写噪声容限。

技术研发人员:陈兴,黄普嵩

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!