包括焊盘图案的半导体装置及其制造方法与流程

本公开涉及一种半导体装置,并且更具体地,涉及一种包括焊盘图案的半导体装置及其制造方法。

背景技术:

1、现代计算装置使用集成电路来实施其组件(诸如通用处理器、专用集成电路(asic)和存储器)中的许多。存储器和存储器系统是这些装置的核心组件,并且允许装置的状态信息随时间流逝而持续以供稍后使用或处理。诸如dram的随机存取存储器允许在几乎相同的时间量中读取或写入数据项,而不管存储器内的数据的物理位置如何。这些存储器系统允许其它组件对信息的快速访问。

2、较新的装置正在使用较大量的存储器。已经进行了减小诸如dram的半导体电路的元件的尺寸的研究,以便以较小的物理形状因子提供较大的存储器尺寸。研究包括开发电路的新的制造工艺,以及开发构成组件的新的布置和形状。

技术实现思路

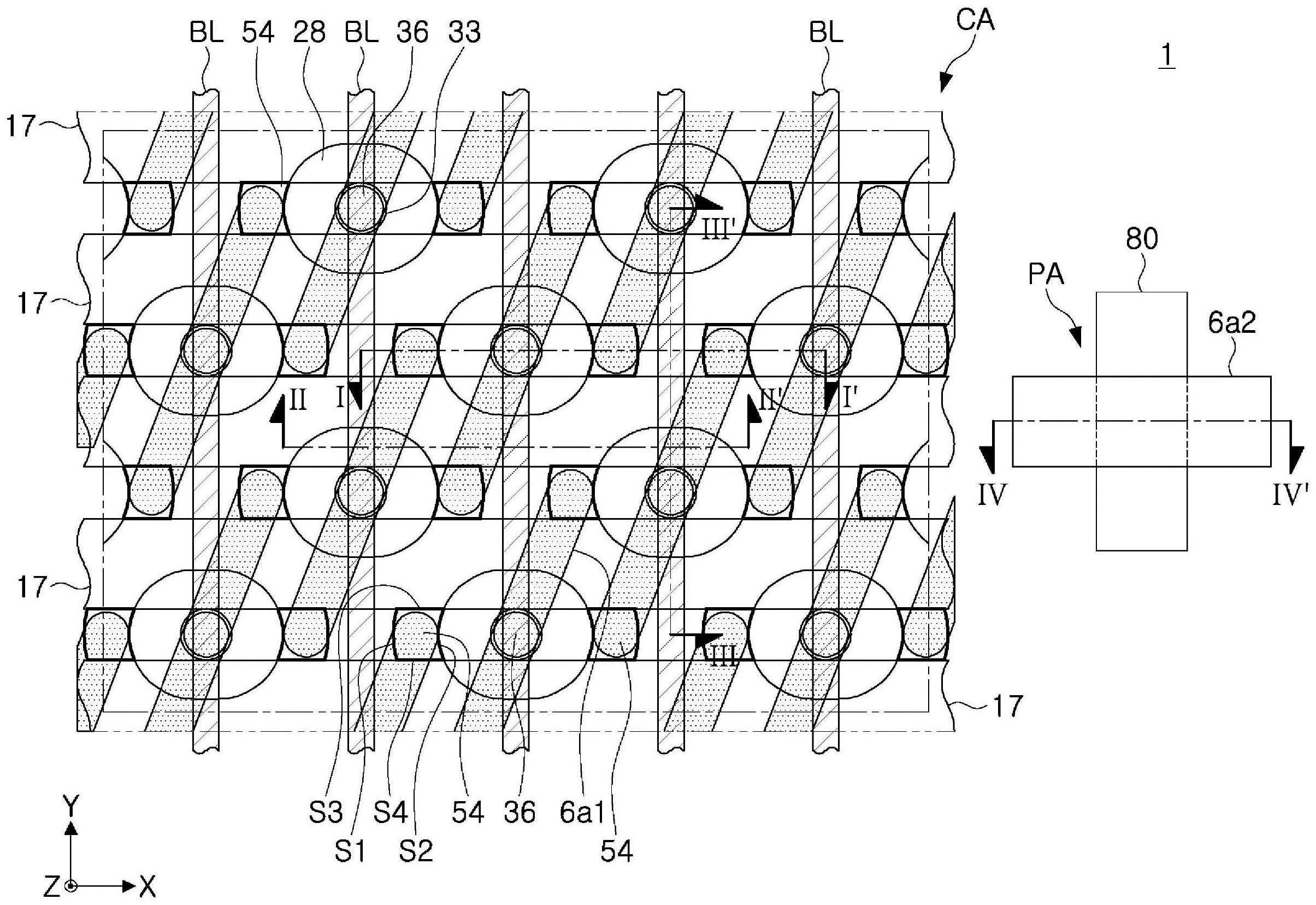

1、一种半导体装置包括:衬底;有源区,其包括第一杂质区和与第一杂质区间隔开的第二杂质区;限定有源区的隔离区;栅极结构,其与有源区相交并在平行于衬底的第一方向上延伸;第一焊盘图案,其设置在第一杂质区上;第二焊盘图案,其设置在第二杂质区上;位线,其设置在第一焊盘图案上并在第二方向上延伸,其中,第二方向垂直于第一方向并平行于衬底;以及在第二焊盘图案上的接触结构,其中,第二焊盘图案具有在第一方向上彼此相对的第一侧表面和第二侧表面,以及在第二方向上彼此相对的第三侧表面和第四侧表面,并且其中,第一侧表面和第二侧表面中的每一个在由第一方向和第二方向形成的水平面中弯曲,并且第三侧表面和第四侧表面中的每一个在水平面中具有基本上线性的形状。一种半导体装置包括:有源区,其包括第一杂质区和与第一杂质区间隔开的第二杂质区;限定有源区的隔离区;栅极结构,其设置在栅极沟槽中,在第一方向上延伸,与有源区相交,并且延伸到隔离区中;第一焊盘图案,其接触第一杂质区并设置在第一杂质区上;第二焊盘图案,其接触第二杂质区,与第一焊盘图案间隔开,并设置在第二杂质区上;位线,其接触第一焊盘图案,在垂直于第一方向的第二方向上延伸,并且其中,位线设置在第一焊盘图案上;接触结构,其接触第二焊盘图案并设置在第二焊盘图案上;以及间隔件结构,其接触位线的侧表面,其中,第一焊盘图案的上表面接触位线的下表面,并且其中,第一焊盘图案的上表面在第一方向上的宽度与位线的下表面在第一方向上的宽度不同。

2、一种半导体装置包括:隔离区,其限定存储器单元区中的单元有源区和外围区中的外围有源区;单元栅极结构,其设置在栅极沟槽中,其中,单元栅极结构在存储器单元区中在第一方向上延伸,与单元有源区相交,并且延伸到隔离区中;第一焊盘图案,其接触单元有源区中的第一杂质区并设置在单元有源区上;第二焊盘图案,其接触单元有源区中的第二杂质区并设置在单元有源区上;位线,其接触第一焊盘图案并在垂直于第一方向的第二方向上延伸,其中,位线设置在第一焊盘图案上;单元接触结构,其接触第二焊盘图案并位于第二焊盘图案上;以及阻挡间隔件,其包括插入在第一焊盘图案和第二焊盘图案之间的部分,其中,第一焊盘图案的上表面的水平与第二焊盘图案的上表面的水平之间的水平差大于第一焊盘图案的下表面的水平与第二焊盘图案的下表面的水平之间的水平差。

3、一种用于制造半导体装置的方法包括:形成限定有源区的隔离区;形成与有源区相交并延伸到隔离区中的栅极沟槽;在栅极沟槽中形成栅极结构;形成第一焊盘图案以接触有源区的第一区;在形成第一焊盘图案之后,形成具有设置在比第一焊盘图案的上表面的水平低的水平上的上表面的第二焊盘图案,其中,第二焊盘图案的上表面接触有源区的第二区;形成下导线以接触第一焊盘图案的上表面并且在与栅极结构相交的方向上延伸;在形成下导线之后,形成上导线和竖直地堆叠在上导线上的位线封盖图案;形成覆盖下导线的侧表面、上导线的侧表面和位线封盖图案的侧表面的位线间隔件;在包括下导线、上导线和位线封盖图案的结构的至少一侧上形成绝缘栅栏;以及形成接触结构以接触绝缘栅栏之间的第二焊盘图案。

技术特征:

1.一种半导体装置,包括:

2.如权利要求1所述的半导体装置,

3.如权利要求1所述的半导体装置,其中,所述第一焊盘图案在所述水平面中具有圆形。

4.如权利要求1所述的半导体装置,还包括:

5.如权利要求4所述的半导体装置,

6.如权利要求4所述的半导体装置,其中,所述阻挡间隔件的厚度大于所述缓冲间隔件的厚度。

7.如权利要求1所述的半导体装置,其中,所述第一焊盘图案的下表面与所述第一焊盘图案的上表面之间的距离大于所述第二焊盘图案的下表面与所述第二焊盘图案的上表面之间的距离。

8.如权利要求1所述的半导体装置,其中,所述第一焊盘图案的上表面的水平与所述第二焊盘图案的上表面的水平之间的水平差大于所述第一焊盘图案的下表面的水平与所述第二焊盘图案的下表面的水平之间的水平差。

9.一种半导体装置,包括:

10.如权利要求9所述的半导体装置,其中,在所述第一方向上,所述第一焊盘图案的上表面的宽度大于所述位线的下表面的宽度。

11.如权利要求9所述的半导体装置,

12.如权利要求11所述的半导体装置,其中,所述第一焊盘图案的上表面包括与所述下导线竖直地重叠的部分和与所述第一位线间隔件竖直地重叠的部分。

13.如权利要求11所述的半导体装置,其中,所述第二位线间隔件的厚度大于所述第一位线间隔件的厚度。

14.如权利要求11所述的半导体装置,其中,所述下导线的侧表面不与所述上导线的侧表面对齐。

15.如权利要求9所述的半导体装置,其中,所述位线的两个侧表面之间的中心轴和所述第一焊盘图案的两个侧表面之间的中心轴在所述第一方向上不对齐。

16.如权利要求9所述的半导体装置,其中,所述第一焊盘图案接触所述第一杂质区的上表面的一部分和与所述第一杂质区相邻的所述隔离区的一部分。

17.如权利要求9所述的半导体装置,还包括:

18.如权利要求17所述的半导体装置,

19.一种半导体装置,包括:

20.如权利要求19所述的半导体装置,还包括:

技术总结

提供了一种半导体装置和一种制造半导体装置的方法。该半导体装置包括:衬底;有源区,其包括第一杂质区和与第一杂质区间隔开的第二杂质区;隔离区,其限定有源区;栅极结构,其与有源区相交并在平行于衬底的第一方向上延伸;第一焊盘图案,其设置在第一杂质区上;第二焊盘图案,其设置在第二杂质区上;位线,其设置在第一焊盘图案上并在第二方向上延伸,其中,第二方向垂直于第一方向并平行于衬底;以及接触结构,其位于第二焊盘图案上,其中,第二焊盘图案具有在第一方向上彼此相对的第一侧表面和第二侧表面,第一侧表面和第二侧表面都沿着平行于衬底的平面弯曲。

技术研发人员:崔民洙,金昭煐

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!