微电子装置、相关电子系统及形成微电子装置的方法与流程

在各种实施例中,本公开大体上涉及微电子装置设计及制造领域。更特定来说,本公开涉及由独立形成的微电子装置结构形成微电子装置的方法及相关微电子装置及电子系统。

背景技术:

1、微电子装置设计者通常期望通过减小个别特征的尺寸及通过减小相邻特征之间的间隔距离来提高微电子装置内特征的集成度或密度。另外,微电子装置设计者通常期望设计不仅小型而且提供性能优势以及简化设计的架构。

2、微电子装置的一个实例是存储器装置。存储器装置通常提供为计算机或其它电子装置中的内部集成电路。存在许多类型的存储器装置,包含(但不限于):易失性存储器装置,例如动态随机存取存储器(dram)装置;及非易失性存储器装置,例如nand快闪存储器装置。dram装置的典型存储器单元包含一个存取装置(例如晶体管)及一个存储器存储结构(例如电容器)。半导体装置的现代应用可采用大量存储器单元,其布置成展现存储器单元行及列的存储器阵列。存储器单元可通过沿存储器阵列的存储器单元行及列布置的数字线(例如位线、数据线)及字线(例如存取线)来电存取。存储器阵列可呈二维(2d)以便展现存储器单元的单个层面(例如单个层级、单个层阶),或可呈三维(3d)以便展现存储器单元的多个层面(例如多个层阶、多个层级)。

3、下伏于存储器装置的存储器阵列的基底控制逻辑结构内的控制逻辑装置已用于控制存储器装置的存储器单元的操作(例如存取操作、读取操作、写入操作)。可提供通过布线及互连结构来与存储器阵列的存储器单元电连通的控制逻辑装置的组合件。然而,用于在基底控制逻辑结构之上形成存储器阵列的处理条件(例如温度、压力、材料)会限制基底控制逻辑结构内控制逻辑装置的配置及性能。另外,在基底控制逻辑结构内采用的不同控制逻辑装置的数量、尺寸及布置也会非期望地阻碍存储器装置的大小(例如水平占用面积)减小及/或存储器装置的性能改进(例如更快存储器单元开/关速度、更低阈值切换电压要求、更快数据传送速率、更低功耗)。此外,随着存储器阵列的密度及复杂性提高,控制逻辑装置的复杂性也提高。在一些例子中,控制逻辑装置比存储器装置占用更多面积以降低存储器装置的存储器密度。

技术实现思路

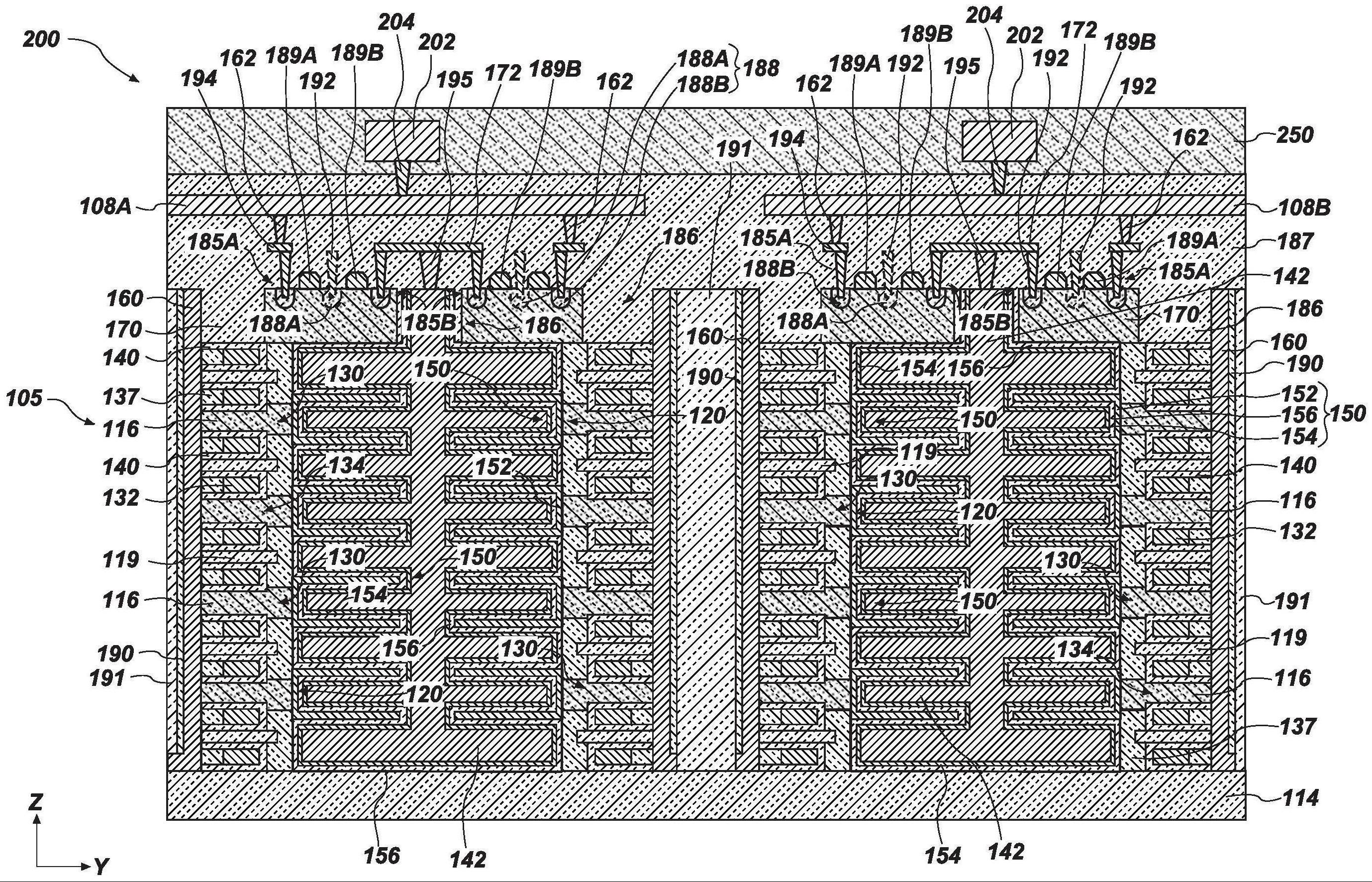

1、在一些实施例中,一种微电子装置包括存储器单元竖直堆叠,存储器单元的每一竖直堆叠包括:存取装置竖直堆叠;电容器竖直堆叠,其与所述存取装置竖直堆叠水平相邻;及导电支柱结构,其竖直延伸穿过所述存取装置竖直堆叠。所述微电子装置进一步包括:多路复用器及额外晶体管,其竖直上覆于所述存储器单元竖直堆叠;及全局数字线,其竖直上覆于所述多路复用器及所述额外晶体管。

2、在其它实施中,一种微电子装置包括:动态随机存取存储器(dram)单元竖直堆叠,每一dram单元包括与存取装置水平相邻的存储装置;至少一个多路复用器,其竖直上覆于所述dram单元竖直堆叠中的至少一者;及至少一个额外晶体管结构,其竖直上覆于所述dram单元竖直堆叠中的所述至少一者且与所述至少一个多路复用器水平相邻,所述至少一个多路复用器及所述至少一个额外晶体管结构共享源极区。

3、在其它实施例中,一种形成微电子装置的方法包括:在竖直延伸穿过彼此水平相邻的存取装置竖直堆叠的开口中形成导电材料以形成与所述存取装置竖直堆叠中的每一者的所述存取装置电连通的导电支柱结构;在所述开口中的所述导电材料之上形成绝缘衬层材料;移除所述开口的所述绝缘衬层材料的下部及所述下部处的所述导电材料以形成个别地与所述存取装置竖直堆叠中的一者电连通的隔离导电支柱结构;在所述存取装置竖直堆叠中的每一者的与所述导电支柱结构相对的一侧上穿过竖直交替第一材料及第二材料的堆叠结构形成沟槽;在所述沟槽中形成电容器结构竖直堆叠以形成存储器单元竖直堆叠,存储器单元的每一竖直堆叠包括与存取装置竖直堆叠电连通的电容器结构竖直堆叠;及在所述存储器单元竖直堆叠中的每一者之上竖直形成多路复用器及至少一个额外晶体管。

4、在额外实施例中,一种电子系统包括:输入装置;输出装置;处理器装置,其可操作地耦合到所述输入装置及所述输出装置;及存储器装置,其可操作地耦合到所述处理器装置。所述存储器装置包括:电容器结构竖直堆叠,其与存取装置竖直堆叠水平相邻;导电板结构,其与所述电容器结构中的每一者的电极电连通;导电支柱结构,其与所述存取装置竖直堆叠电连通;电容器结构额外竖直堆叠,其包括与所述导电支柱结构电连通的额外电极,所述导电板结构水平介入于所述电容器结构额外竖直堆叠与所述电容器结构竖直堆叠之间;及多路复用器及泄放晶体管,其竖直上覆于所述电容器结构竖直堆叠及所述存取装置竖直堆叠。

技术特征:

1.一种微电子装置,其包括:

2.根据权利要求1所述的微电子装置,其中每一多路复用器个别地与所述额外晶体管中的一者共享源极区。

3.根据权利要求1所述的微电子装置,其进一步包括竖直延伸穿过所述存储器单元竖直堆叠且与所述存储器单元竖直堆叠的所述电容器竖直堆叠相邻的导电板结构。

4.根据权利要求3所述的微电子装置,其中成对的所述额外晶体管与所述导电板结构电连通。

5.根据权利要求1所述的微电子装置,其中:

6.根据权利要求1所述的微电子装置,其中水平相邻多路复用器个别地与竖直延伸穿过存储器单元的不同竖直堆叠的导电支柱结构电连通。

7.根据权利要求1所述的微电子装置,其进一步包括与所述存储器单元竖直堆叠中的多者相交的导电结构竖直堆叠。

8.根据权利要求7所述的微电子装置,其中所述导电结构竖直堆叠的每一导电结构经配置以与所述导电结构竖直堆叠相交的所述存储器单元竖直堆叠的存取装置电连通。

9.根据权利要求1至8中任一权利要求所述的微电子装置,其进一步包括个别地与所述多路复用器中的一者的漏极区及所述全局数字线中的一者电连通的全局数字线接触结构。

10.根据权利要求1至8中任一权利要求所述的微电子装置,其中彼此水平相邻的成对的所述额外晶体管的漏极区彼此电连通。

11.根据权利要求1至8中任一权利要求所述的微电子装置,其中所述多路复用器中的每一者的源极区与所述导电支柱结构中的一者电连通。

12.一种微电子装置,其包括:

13.根据权利要求12所述的微电子装置,其进一步包括竖直上覆于所述至少一个多路复用器的全局数字线。

14.根据权利要求12所述的微电子装置,其中所述源极区与竖直延伸穿过所述dram单元竖直堆叠中的所述至少一者的导电支柱结构电连通。

15.根据权利要求12所述的微电子装置,其中所述至少一个多路复用器的漏极区与全局数字线电连通。

16.根据权利要求12所述的微电子装置,其中所述至少一个额外晶体管结构的漏极区与导电板结构电连通。

17.根据权利要求12所述的微电子装置,其中所述至少一个多路复用器的漏极区与所述至少一个额外晶体管的漏极区水平对准。

18.根据权利要求17所述的微电子装置,其中所述至少一个多路复用器的所述漏极区及所述至少一个额外晶体管的所述漏极区与所述至少一个多路复用器电连通的全局数字线水平对准。

19.根据权利要求17所述的微电子装置,其中所述源极区从所述至少一个多路复用器的所述漏极区及所述至少一个额外晶体管的所述漏极区水平偏移。

20.根据权利要求12至19中任一权利要求所述的微电子装置,其中所述至少一个多路复用器的栅极结构在大体上垂直于字线的水平方向上延伸,所述字线经配置以与所述dram单元的所述存取装置电连通。

21.一种形成微电子装置的方法,所述方法包括:

22.根据权利要求21所述的方法,其中在所述沟槽中形成电容器结构竖直堆叠以形成存储器单元竖直堆叠包括:

23.根据权利要求22所述的方法,其进一步包括在所述沟槽中的所述第二电极材料之上形成导电板结构。

24.根据权利要求23所述的方法,其中形成至少一个额外晶体管包括形成与所述导电板结构电连通的所述至少一个额外晶体管的漏极区。

25.根据权利要求21至24中任一权利要求所述的方法,其中形成多路复用器包括形成与竖直上覆于所述多路复用器的全局数字线电连通的所述多路复用器的漏极区。

26.根据权利要求21至24中任一权利要求所述的方法,其中形成多路复用器及至少一个额外晶体管包括形成与所述至少一个额外晶体管共享的所述多路复用器的源极区。

27.一种电子系统,其包括:

28.根据权利要求27所述的电子系统,其进一步包括竖直上覆于所述多路复用器及所述泄放晶体管的全局数字线。

29.根据权利要求28所述的电子系统,其中:

30.根据权利要求27至29中任一权利要求所述的电子系统,其中所述多路复用器包括与所述泄放晶体管共享的源极区。

技术总结

本申请大体上涉及微电子装置、相关电子系统及形成微电子装置的方法。一种微电子装置包括存储器单元竖直堆叠,存储器单元的每一竖直堆叠包括:存取装置竖直堆叠;电容器竖直堆叠,其与所述存取装置竖直堆叠水平相邻;及导电支柱结构,其竖直延伸穿过所述存取装置竖直堆叠。所述微电子装置进一步包括:多路复用器及额外晶体管,其竖直上覆于所述存储器单元竖直堆叠;及全局数字线,其竖直上覆于所述多路复用器及所述额外晶体管。

技术研发人员:F·A·席赛克-艾吉,R·E·法肯索尔

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!