一种基于多重混联校验码的信道编译码装置及方法

本发明属于无线通信,具体涉及一种基于多重混联校验码的信道编译码装置及方法。

背景技术:

1、在语音、数据、图像、视频等综合业务和不同种类多媒体业务等通信业务中,随着信息技术的发展,人们对通信有着更高的要求。无线通信技术由于不必建立物理线路,成本较低、对抗环境的变化能力较强等优点而蓬勃发展。无线数据的编译码技术也因此成为当前通信领域的研究热点。

2、信道编码是无线通信技术领域的重要一环,通信系统通常采用信道编码提高数据传输的可靠性,保证通信的质量。目前信道编码的分类主要包括线性分组码、卷积码、级联码、turbo码和ldpc码。其中分组码又分为汉明码、格雷码、循环码。在这几种编码类型中,级联编码应用的场景更加广泛、性能更佳。

技术实现思路

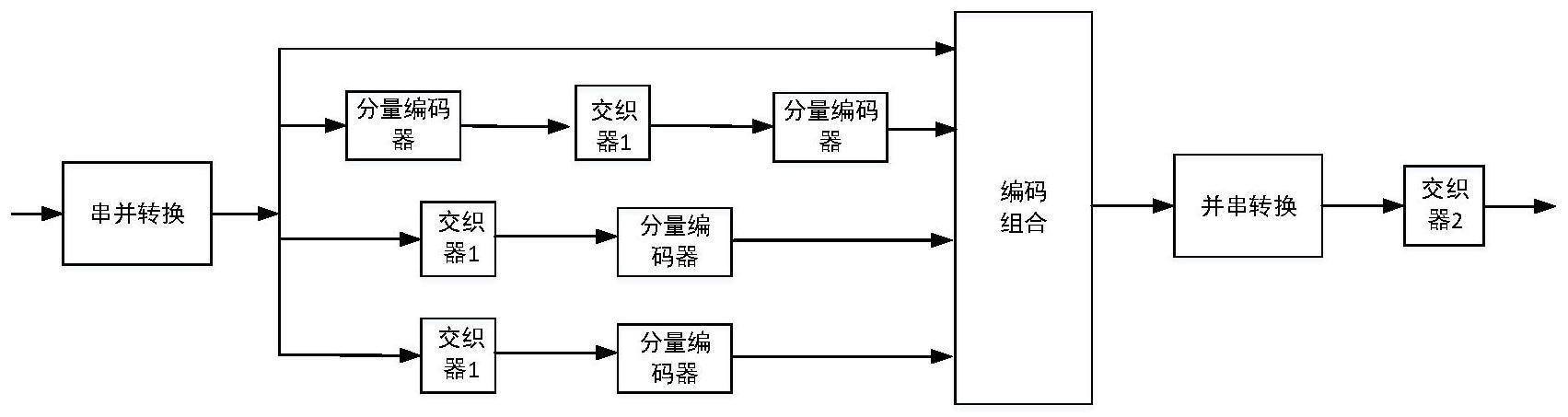

1、本发明提供了一种基于多重混联校验码的信道编译码装置及方法,主要是将分量编码模块通过串联、并联方式级联起来,生成校验码,通过组合输出编码数据,最后通过并串转换和交织器生成串行编码序列。

2、译码方面主要通过迭代译码,将接收数据首先通过解交织器及串并转换,之后通过分量译码器与交织解交织器组成的迭代译码系统,最后通过硬判决输出译码后的数据。

3、本发明通过以下技术方案予以实现:

4、本发明提供一种基于多重混联校验码的信道编码装置,包括串并转换模块、分量编码器模块、交织器1模块、编码组合模块、并串转换模块以及交织器2模块;

5、所述串并转换模块输入为串行数据序列,所述串并转换模块输出与编码器各个并行支路模块连接,用于将串行数据转换成并行数据,便于后续编码;

6、所述分量编码器模块输入为经串并转换模块后的原始数据,或者输入为通过交织器1模块的输出数据,与后续交织器1模块相连,或者与编码组合模块相连,用于将输入数据进行奇偶校验,输出校验码;

7、所述交织器1模块输入为经串并转换模块后的原始数据,或者输入为经过分量编码器模块后的数据,与后续分量编码器模块相连,利用规则行列循环交织规则用于将输入数据顺序进行打乱,减少衰落及突发干扰;

8、所述编码组合模块输入为经串并转换模块后的原始数据以及经过编码后的校验码,与并串转换模块相连,用来生成完整的编码数据;

9、所述并串转换模块输入为组合后的完整编码数据,与交织器2模块相连,用于将并行数据转换为串行数据;

10、所述交织器2模块输入为并串转换后的串行数据,利用与交织器1不同的分组交织方式实现编码后数据的交织出来,进一步减少突发干扰。

11、本发明还提供一种基于多重混联校验码的信道译码装置,包括解交织器2模块、串并转换模块、数据拆分模块、分量译码器模块、交织器1模块、解交织器1模块和硬判决模块;

12、所述解交织器2模块输入为接收端接收到的串行数据,与后续串并转换模块相连,作用是将发送端通过交织器2模块输出的数据恢复成交织前的序列顺序;

13、所述串并转换模块输入为通过解交织器2模块后输出的串行数据,与数据拆分模块相连,用于将串行数据转换成并行数据,便于后续解码模块的使用;

14、所述数据拆分模块输入为接收到的并行数据,与后续多重迭代译码系统相连,用于将数据拆分成原始数据与4个校验码,作用于迭代译码的输入;

15、所述分量译码器模块输入为利用对数似然比作为软信息输入的先验信息,与解交织模块相连,输出为经过解交织的外信息,作为先验信息输入给其他的分量译码器,进行下一次迭代译码的输入;

16、所述交织器1模块输入为经过解交织后的外信息,与分量译码器相连,用于将外信息进行交织处理,输入到下一次迭代译码的分量译码器中;

17、所述解交织器1模块输入为经过分量译码的外信息,与下一次迭代的交织器1模块相连,用于将外信息数据恢复成原始顺序序列;

18、所述硬判决模块输入为接收数据的似然比以及各个分支经过迭代译码输出的信息数据似然比值,作用为根据输入的似然比值对每一比特的值进行判决,输出译码后的结果。

19、本发明还提供一种基于多重混联校验码的信道编码方法,包括以下步骤:

20、步骤1,将发送端的串行数据输入至串并转换模块,将序列转换成m×n的矩阵形式;

21、步骤2,将转换成并行数据的m×n矩阵d分成三路分别进行校验码的生成;

22、步骤3,将并行数据矩阵经过编码器的第一支路,并行数据矩阵进入分量编码器,分量编码器采用奇偶校验规则,按行校验其中是否有奇数个或者偶数个“1”,生成校验码,将原始数据及校验码组成的数据(d、p11)通过交织器1,将数据顺序按照规则打乱,最后再通过一个分量编码器产生奇偶校验码p1,得到第一支路的校验码;

23、步骤4,将并行数据矩阵经过编码器的第二支路,并行数据矩阵d首先进入交织器1,将数据矩阵按照规则打乱,最后通过一个分量编码器,按行校验其中是否有奇数个或者偶数个“1”,最后生成第二支路校验码p2;

24、步骤5,同步骤4一致,数据矩阵d首先进入循环交织器1,然后通过分量编码器,最后生成第三支路奇偶校验码p3;

25、步骤6,将原始m×n的信息数据矩阵d、三条支路的校验码p11、p1、p2、p3输入至编码组合模块,将数据进行组合得到最终编码后的数据c=(d、p11、p1、p2、p3);

26、步骤7,将得到的编码后的数据c进行并串转换,输出串行数据序列;

27、步骤8,将步骤7所得序列输入到另一交织器2中,交织器2采用分组交织规则,将序列按行写入一个i×j的矩阵中,然后按照列读出数据,最终产生编码后输出的数据比特。

28、本发明还提供一种基于多重混联校验码的信道译码方法,包括以下步骤:

29、步骤1,接收端接收到信息序列后,首先通过解交织器2,解交织器2是根据分组交织规则,将序列按列写入一个j×i的矩阵中,然后按照行读出数据,来使得数据恢复到原始顺序;

30、步骤2,将步骤1输出的数据序列,通过串并转换模块,输出m×n的矩阵数据;

31、步骤3,将步骤2中的矩阵数据,通过数据拆分,将数据拆分成信息数据d以及四个校验码序列p1、p2、p3以及第一支路上通过第一个分量编码器后产生的校验码p11;

32、步骤4,通过步骤3得到的信息数据d,输入到第一支路的分量译码器中,同时将另外三个支路输出的外信息值,通过交织器1后输入至该分量译码器中,分量译码器采用max-log-map算法,得到先验信息值,之后通过解交织器1输出该支路的外信息w1,重复此步骤,直到达到规定的迭代停止准则或迭代次数为止;

33、步骤5,其他三条支路同步骤4一致,输入除本支路外其他支路输出的先验信息值,通过交织器1得到其他三条支路的外信息w2,w3、w4重复此步骤,直至迭代停止;

34、步骤6,将迭代停止后的信息数据d以及四条支路得到的外信息值w1、w2、n3、w4输入至硬判决模块,根据判决规则输出译码后的数据。

35、与现有技术相比,本发明有益效果是:

36、1、相比于其他级联编码,本发明编码具有较高的编码效率,误码率更低,具有更好的性能。

37、2、相较于其他迭代译码,本发明译码复杂度较小,便于在硬件上实现,消耗的资源也较小。

- 还没有人留言评论。精彩留言会获得点赞!