用于高压操作的半导体开关的制作方法

本披露总体上涉及半导体器件领域,更具体地,涉及用于高压操作的半导体开关。

背景技术:

1、半导体器件可以包括电压电平移位电路,这些电压电平移位电路生成高压信号以支持需要比供应到半导体器件的电压更高的电压的操作。当高压信号从电压电平移位电路传送到半导体器件的各个部件时,希望具有可以处理高电压而不会引起可靠性或功能性问题的开关。

技术实现思路

1、本披露描述了用于高压操作的半导体开关。这些开关包括n沟道和/或p沟道扩散增强型金属氧化物半导体场效应晶体管(de-mos fet)。除其他特征之外,de-mos fet包括用于支持相对较高的电压信号的缓变结。本披露描述了为包括在用于高压操作的半导体开关中的这种de-mos fet提供安全操作条件的电路。此

技术实现要素:

并不是本披露的全面概览,并且不旨在标识本披露的关键或重要元件,也不旨在界定其范围。相反,本发明内容的主要目的是以简化形式呈现本披露的一些概念,作为稍后呈现的更详细描述的序言。

2、在一些实施例中,一种电路包括:de-nmos fet,其包括耦合到该电路的节点的栅极,其中,该de-nmos fet的源极和漏极分别耦合到电路的输入节点和输出节点;耦合到该节点的电压源,其中,该电压源被配置为在该节点处提供第一电压,该第一电压比该输入节点处的第二电压大预定量;以及耦合到该节点的电流源,该电流源被配置为向该电压源供应电流。

3、在一些实施例中,一种电路包括:第一部件,其包括输出节点,该第一部件被配置为在该输出节点处生成第一电压;第二部件,其耦合到电源节点,该第二部件被配置为以该第一电压操作;以及第一开关,其连接在该输出节点与该电源节点之间,其中,该第一开关包括:第一de-nmos fet,其包括耦合到第一开关的第一节点的栅极,其中,该第一de-nmosfet的源极和漏极分别耦合到输出节点和该电源节点;耦合到该第一节点的第一电压源,其中,该第一电压源被配置为生成比该第一电压大第一预定量的第二电压;以及耦合到该第一节点的第一电流源,该第一电流源被配置为向该第一电压源供应第一电流。

4、在一些实施例中,一种方法包括:确定向部件的电源节点供应第一电压或第二电压;以及至少部分基于该确定,启用被配置为将该第一电压耦合到该电源节点的第一开关或者被配置为将该第二电压耦合到该电源节点的第二开关,其中,该第一开关和该第二开关中的每一个包括:de-nmos fet,其具有耦合到该开关的节点的栅极,其中,该de-nmosfet的源极和漏极分别耦合到该开关的输入节点和输出节点;耦合到该节点的电压源,其中,该电压源被配置为生成比该输入节点的输入电压大预定量的电压;以及耦合到该节点的电流源,该电流源被配置为向该电压源供应电流。

技术特征:

1.一种电路,包括:

2.根据权利要求1所述的电路,其中,所述预定量小于所述de-nmos fet的栅源击穿电压bvgs。

3.根据权利要求2所述的电路,其中,所述de-nmos fet的bvgs小于所述de-nmos fet的漏栅击穿电压bvdg或者所述de-nmos fet的漏源击穿电压bvds。

4.根据权利要求1所述的电路,其中,所述预定量对应于跨所述de-nmosfet的栅极和源极施加的电压vgs,所述电压激活所述de-nmos fet以将所述第二电压传送到所述输出节点。

5.根据权利要求1所述的电路,其中,所述电压源包括:

6.根据权利要求5所述的电路,其中,所述一个或多个二极管中的第二二极管的阳极耦合到所述节点。

7.根据权利要求6所述的电路,其中,所述第一二极管对应于所述第二二极管。

8.根据权利要求5所述的电路,其中,所述预定量与以下各项的总和成比例:所述de-pmos fet的阈值电压以及所述一个或多个二极管的阈值电压之和。

9.根据权利要求5所述的电路,其中,所述de-nmos fet是第一de-nmosfet,并且所述一个或多个二极管中的每个二极管对应于漏极和栅极连接在一起的第二de-nmos fet。

10.根据权利要求9所述的电路,其中,所述第一de-nmos fet具有第一阈值电压,并且所述第二de-nmos fet中的每一个具有与所述第一阈值电压相同的第二阈值电压。

11.根据权利要求1所述的电路,其中,所述电流源对应于电流镜电路中的de-pmosfet,并且其中,所述de-pmos fet的源极和漏极分别耦合到电压供应装置和所述节点。

12.根据权利要求1所述的电路,其中,所述de-nmos fet是第一de-nmos fet,并且所述电路进一步包括:

13.根据权利要求12所述的电路,其中,所述电流源被配置为响应于在所述第二de-nmos fet的栅极处施加的启用所述电路的信号,向所述电压源供应所述电流。

14.根据权利要求12所述的电路,其中,所述第一de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的启用所述电路的信号,将所述输入节点处的第二电压传送到所述输出节点。

15.根据权利要求12所述的电路,其中,所述第一de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的禁用所述电路的信号,将所述输出节点与所述输入节点隔离开。

16.根据权利要求12所述的电路,其中,所述第二de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的禁用所述电路的信号,从所述电流源汲取所述电流。

17.根据权利要求12所述的电路,其中,所述第二de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的禁用所述电路的信号,将所述第一de-nmos fet的栅极耦合到接地节点。

18.一种电路,包括:

19.根据权利要求18所述的电路,其中,所述第一预定量对应于跨所述第一de-nmosfet的栅极和源极施加的电压vgs,所述电压激活所述第一de-nmos fet以将所述第一电压传送到所述电源节点。

20.根据权利要求18所述的电路,其中,所述第一电压源包括:

21.根据权利要求20所述的电路,其中,所述一个或多个二极管中的每个二极管对应于一个de-nmos fet,所述de-nmos fet包括连接到其栅极的漏极。

22.根据权利要求21所述的电路,其中,所述第一de-nmos fet具有第一阈值电压,并且所述de-nmos fet中的每一个具有与所述第一阈值电压相同的第二阈值电压。

23.根据权利要求18所述的电路,其中,所述第一开关进一步包括:

24.根据权利要求23所述的电路,其中,所述第一de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的启用所述第一开关的所述第一信号,将所述输出节点处的所述第一电压传送到所述电源节点。

25.根据权利要求23所述的电路,其中,所述第一de-nmos fet被配置为响应于在所述第二de-nmos fet的栅极处施加的禁用所述第一开关的所述第一信号,将所述输出节点与所述电源节点隔离开。

26.根据权利要求23所述的电路,进一步包括第二开关,其连接在所述电源节点与连接到外部电源的焊盘之间,所述外部电源被配置为在所述焊盘处供应第三电压,其中,所述第二开关包括:

27.根据权利要求26所述的电路,其中:

28.根据权利要求26所述的电路,其中,所述第三de-nmos fet被配置为响应于在所述第四de-nmos fet的栅极处施加的启用所述第二开关的所述第二信号,将所述第三电压传送到所述电源节点。

29.根据权利要求26所述的电路,其中,所述第三de-nmos fet被配置为响应于在所述第四de-nmos fet的栅极处施加的禁用所述第二开关的所述第二信号,将所述焊盘与所述电源节点隔离开。

30.根据权利要求18所述的电路,其中,所述第一部件包括电压电平移位器,所述电平移位器被配置为基于小于所述第一电压的第三电压生成所述第一电压。

31.根据权利要求18所述的电路,其中,所述第二部件包括电可擦除可编程只读存储器eeprom单元阵列。

32.一种方法,包括:

33.根据权利要求32所述的方法,其中:

34.根据权利要求32所述的方法,其中,所述de-nmos fet是第一de-nmos fet,并且所述第一开关和所述第二开关中的每一个进一步包括:

35.根据权利要求34所述的方法,其中,启用所述第一开关包括:

36.根据权利要求34所述的方法,其中,启用所述第二开关包括:

37.根据权利要求32所述的方法,其中,向所述电源节点供应所述第一电压包括:

38.根据权利要求32所述的方法,其中,向所述电源节点供应所述第二电压包括:

39.根据权利要求32所述的方法,其中,所述电压源包括:

40.根据权利要求39所述的方法,其中,所述de-nmos fet是第一de-nmos fet,并且其中,所述一个或多个二极管中的每个二极管对应于一个第二de-nmos fet,所述第二de-nmos fet包括连接到其栅极的漏极。

41.根据权利要求40所述的方法,其中,所述第一de-nmos fet具有第一阈值电压,并且所述第二de-nmos fet中的每一个具有与所述第一阈值电压相同的第二阈值电压。

42.根据权利要求32所述的方法,其中,所述部件包括被配置为以所述第一电压或所述第二电压操作的电可擦除可编程只读存储器eeprom单元阵列。

技术总结

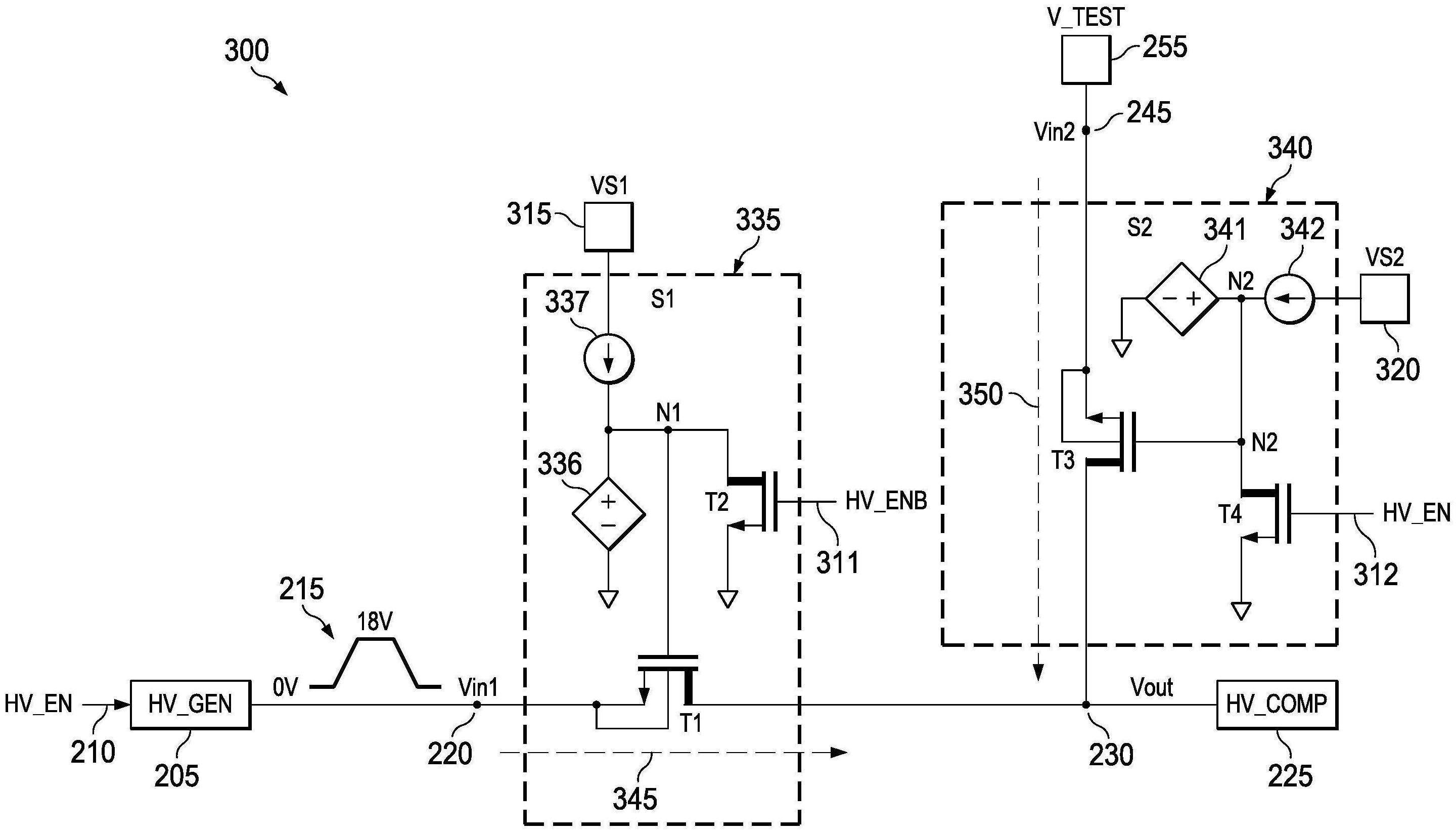

描述了用于高压操作的半导体开关(335,340)。该半导体开关包括第一DE‑NMOS FET(T1,T3),其包括耦合到该开关的节点(N1,N2)的栅极,其源极和漏极分别耦合到输入节点和输出节点(220,245,230)。该开关还包括第二DE‑NMOS FET(T2,T4),其漏极耦合到该节点(N1,N2)。该第二DE‑NMOS FET(T2,T4)的栅极被配置为接收启用或禁用该开关(335,340)的信号(HV_ENB,HV_EN)。该开关包括耦合到该节点(N1,N2)的电压源(例如,压控电压源)(336,341),该电压源在该节点(N1,N2)处供应第一电压。该第一电压比在该输入节点(220,245)处的第二电压大预定量,使得该第一DE‑NMOS FET(T1,T3)可以在支持高压操作的同时在安全操作区内操作。该开关还包括被配置为向该电压源(336,341)供应电流的电流源(337,342)。

技术研发人员:R•辛哈,R•库尔斯乐斯塔

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!