一种迟滞比较器的制作方法

本技术涉及电子,具体涉及一种迟滞比较器。

背景技术:

1、迟滞比较器是一种具有迟滞特性的比较器电路,它可以将输入信号与阈值进行比较,并输出相应的信号。迟滞比较器具有一定的迟滞量,可以有效地降低由于输入信号微小波动而导致的误判,以及滤除输入信号中的噪声和干扰,从而提高系统的稳定性和抗噪声能力。

2、当迟滞比较器处于复杂环境中时,需要根据不同信号的干扰调节合适的迟滞量,从而抵抗噪声。而现有技术中,迟滞比较器的迟滞量通常是由电路元件参数决定的,不能根据实际情况进行调节。

3、因此,亟需一种可调节迟滞量的迟滞比较器。

技术实现思路

1、本技术提供了一种迟滞比较器,可以根据实际情况对迟滞量进行调节。

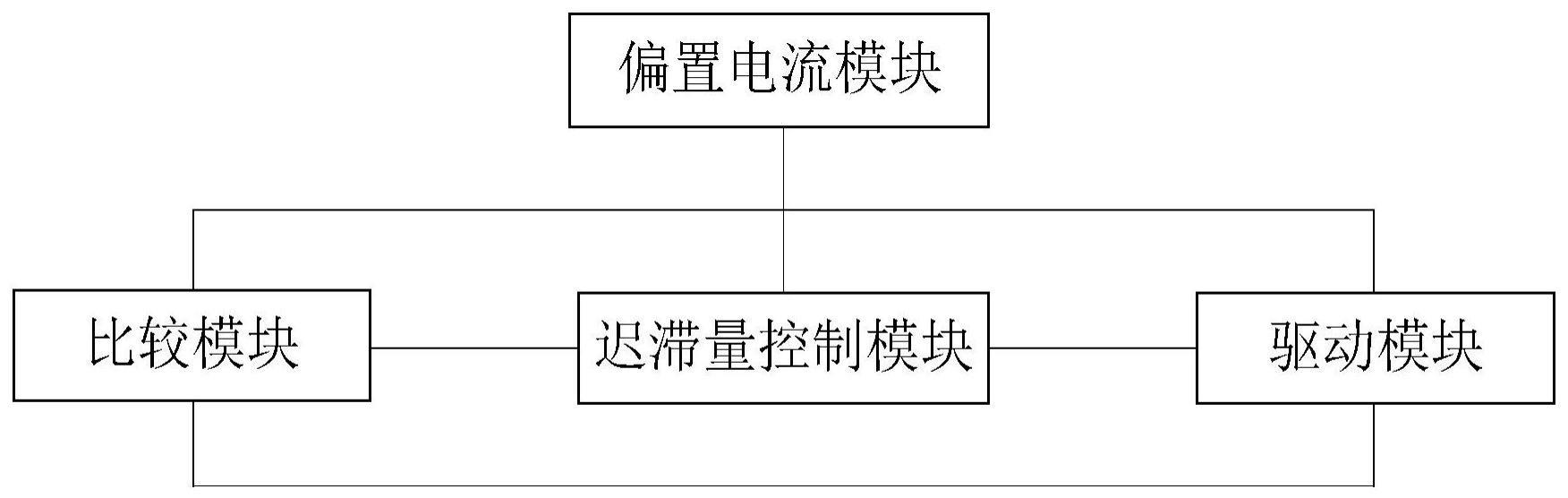

2、第一方面,本技术提供了一种迟滞比较器,其特征在于,包括:偏置电流模块、迟滞量控制模块、比较模块以及驱动模块,其中:

3、所述偏置电流模块的输出端分别与所述迟滞量控制模块的电源端、所述比较模块的电源端以及所述驱动模块的电源端相连接,所述偏置电流用于为所述迟滞量控制模块、所述比较模块以及所述驱动模块提供偏置电流;

4、所述比较模块的第一端与所述迟滞量控制模块的第一端相连接,所述比较模块的第二端与所述驱动模块的第一端相连接;

5、所述迟滞量控制模块的第二端与所述驱动模块的第一端相连接;

6、所述比较模块,用于接收从第一外部接口输入的电压信号,根据所述电压信号,生成比较信号,并将所述比较信号输出至所述驱动模块;

7、所述迟滞量控制模块,用于接收从第二外部接口输入的迟滞量控制信号,根据所述迟滞量控制信号产生迟滞时长,并将所述迟滞时长输出至所述比较模块;

8、所述比较模块,还用于确定接收到所述迟滞时长的第一时刻,在所述迟滞时长内,持续输出所述第一时刻的比较信号至所述驱动模块;

9、所述驱动模块,用于输出所述比较模块输出的比较信号至第三外部接口。

10、通过采用该技术方案,当迟滞比较器在实际应用中存在各种干扰源时,可根据第二外部接口输入的迟滞量控制信号产生迟滞时长,相比于现有技术中,需要根据电路元件参数设置的固定迟滞量可能无法满足实际需求,而本技术实施例提供的迟滞比较器中的迟滞时长可根据输入的控制信号灵活调节。

11、可选的,所述驱动模块为前级驱动模块,所述偏置电流模块包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第一nmos管以及第二nmos管,其中:

12、所述第一pmos管的漏极分别与所述第一nmos管的漏极、所述第一nmos管的栅极、所述第二nmos管的栅极以及所述第五nmos管的栅极相连接,所述第一pmos管的源极与直流电源相连接,所述第一pmos管的栅极接偏置电压;

13、所述第二nmos管的漏极分别与所述第二pmos管的漏极、所述第二pmos管的栅极、所述第三pmos管的栅极、所述第四pmos管的栅极相连接;

14、所述第三pmos管的漏极与所述迟滞量控制模块相连接;

15、所述第四pmos管的漏极与所述前级驱动模块相连接;

16、所述第一nmos管的源极以及所述第二nmos管的源极接地。

17、通过采用该技术方案,偏置电流模块可为迟滞比较器提供稳定的静态工作电流,通过对各个管子宽长比不同,对迟滞比较器的偏置电流进行配置,以维护迟滞比较器的精度和稳定性。

18、可选的,所述驱动模块为前级驱动模块,所述第一外部接口包括第一电压输入接口和第二电压输入接口,比较模块包括第五pmos管、第六pmos管、第三nmos管、第四nmos管以及第六nmos管,其中:

19、所述第五pmos管的栅极与所述第一电压输入接口相连接,所述第五pmos管的源极与所述迟滞量控制模块的第一端相连接,所述第五pmos管的漏极分别与所述第三nmos管的栅极、所述第三nmos管的漏极以及所述第四nmos管的栅极相连接;

20、所述第六pmos管的源极与所述迟滞量控制模块的第一端相连接,所述第六pmos管的栅极与所述第二电压输入接口相连接,所述第六pmos管的漏极分别与所述第四nmos管的漏极以及所述第六nmos管的栅极相连接;

21、所述第六nmos管的漏极分别与所述偏置电流模块的输出端以及前级驱动模块的第一端相连接,所述第六nmos管的源极接地;

22、所述第三nmos管的源极以及所述第四nmos管的源极接地。

23、通过采用该技术方案,比较模块的电流由偏置电流模块提供,当输入信号inp或者inn的输入电压不同,使得流过第五pmos管和第六pmos管的电流大小不同。如果流过第五pmos管比流过第六pmos管的电流大时,使得第六nmos管的栅极高电平,如果流过第五pmos管比流过第六pmos管的电流小时,使得第六nmos管的栅极低电平,从而实现对输入信号的快速响应。

24、可选的,所述驱动模块为前级驱动模块,所述迟滞量控制模块包括至少两个迟滞量控制单元、迟滞量输出单元、恒流源单元以及反馈单元,其中:

25、各个所述迟滞量控制单元逐级连接,第一个迟滞量控制单元与所述偏置电流模块相连接,最后一个迟滞量控制单元与所述迟滞量输出单元的第一端相连接;

26、所述迟滞量输出单元的第二端与所述反馈单元的一端相连接,所述迟滞量输出单元的第三端与所述恒流源单元的第一端相连接;

27、所述恒流源单元的第二端与所述偏置电流模块相连接,所述恒流源的第三端接地;

28、所述反馈单元的另一端与所述前级驱动模块的第一端相连接。

29、通过采用该技术方案,迟滞量控制单元可根据控制输入信号,产生延迟输出信号的响应,从而实现迟滞比较器的迟滞特性,使得输出信号更加稳定可靠。

30、可选的,迟滞量控制模块包括第一迟滞量控制单元、第二迟滞量控制单元、第三迟滞量控制单元、第四迟滞量控制单元、所述迟滞量输出单元、所述恒流源单元以及所述反馈单元,所述第二外部接口包括第一信号输入接口、第二信号输入接口、第三信号输入接口、第四信号输入接口,所述第一迟滞量控制单元包括第十三nmos管、十四nmos管、第一电阻以及第二电阻,所述第二迟滞量控制单元包括第十二nmos管、十五nmos管、第三电阻以及第四电阻,所述第三迟滞量控制单元包括第十一nmos管、十六nmos管、第五电阻以及第六电阻,所述第四迟滞量控制单元包括第十nmos管、十七nmos管、第七电阻以及第八电阻,所述迟滞量输出单元为第七pmos管,所述恒流源单元为第五nmos管,所述反馈单元包括第八pmos管、第九pmos管、第八nmos管、第九nmos管,其中:

31、所述第十三nmos管的栅极分别与所述第一信号输入接口以及所述第十四nmos管的栅极相连接,所述第十三nmos管的漏极分别与所述第一电阻的一端、所述第二电阻的一端、所述第十四nmos管的漏极以及所述偏置电流模块相连接,所述第十三nmos管的源极分别与所述第一电阻的另一端、所述第十二nmos管的漏极以及所述第三电阻的一端相连接;

32、所述第十四nmos管的源极分别与所述第二电阻的另一端、所述第四电阻的一端以及所述第十五nmos管的漏极相连接;

33、所述第十二nmos管的栅极分别与所述第二信号输入接口、所述第十五nmos管的栅极相连接,所述第二nmos管的源极分别与所述第三电阻的另一端、所述第五电阻的一端、所述第十一nmos管的漏极相连接;

34、所述第十五nmos管的源极分别与所述第四电阻的另一端、所述第六电阻的一端以及所述第十六nmos管的漏极相连接;

35、所述第十一nmos管的栅极分别与所述第三信号输入接口、所述第十六nmos管的栅极相连接;所述第十一nmos管的源极分别与所述第五电阻的另一端、所述第十nmos关的漏极以及所述第七电阻的一端相连接;

36、所述第十六nmos管的源极分别与所述第六电阻的另一端、所述第十七nmos管的漏极以及所述第八电阻的一端相连接;

37、所述第十nmos管的栅极分别与所述第四信号输入接口以及所述第十七nmos管的栅极相连接,所述第十nmos管的源极分别与所述第七电阻的另一端、所述比较模块的一端、所述第七pmos管的源极相连接;

38、所述第十七nmos管的源极分别与所述第八电阻的另一端以及所述比较模块的一端相连接;

39、所述第七pmos管的漏极与所述第五nmos管的漏极相连接,所述第七pmos管的栅极分别与所述第九pmos管的漏极以及所述第七nmos管的漏极相连接;

40、所述第五nmos管的栅极与所述偏置电流模块相连接,所述第五nmos管的源极接地;

41、所述第九pmos管的源极接直流电源,所述第九pmos管的栅极分别与所述第七nmos管的栅极、所述第八pmos管的漏极以及所述第八nmos管的漏极相连接;

42、所述第八pmos管的栅极分别与所述前级驱动模块的一端以及所述第八nmos管的栅极相连接;

43、所述第七nmos管的源极以及所述第八nmos管的源极分别接地。

44、通过采用该技术方案,采用4个迟滞量控制单元组成迟滞量控制模块,输入信号f1、f2、f3、f4=0000到f1、f2、f3、f4=1111,能产生16个控制组合,从而可进一步提高迟滞量控制信号的精度。

45、可选的,所述驱动模块为后级驱动模块,所述后级驱动模块包括第十pmos管和第九nmos管,第十五pmos管和第二十四nmos管,其中:

46、所述第十五pmos管的栅极分别与所述第二十四nmos管栅极相连、所述偏置电流模块的输出端、所述比较模块的第二端以及所述迟滞量控制模块的第二端相连接,所述第十五pmos管的漏极分别与所述第二十四nmos管漏极、所述第十pmos管的栅极以及所述第九nmos管栅极相连,所述第十五pmos管的源极、所述第十pmos管的源极以及直流电源相连接;

47、所述第十pmos管的漏极分别与第九nmos管漏极、所述第三外部接口相连接;

48、所述第二十四nmos管的源极和第九nmos管的源极接地。

49、通过采用该技术方案,后级驱动模块具有将比较模块和迟滞量控制模块的输出转换为对外部器件驱动/关闭的能力,可以用于控制其他电路或外部设备的操作。

50、可选的,所述的迟滞比较器,还包括:基准电流模块,其中:

51、所述基准电流模块的一端与所述偏置电流模块的输入端相连接,所述基准电流模块用于为所述偏置电流模块产生基准电流。

52、通过采用该技术方案,基准电流模块可为偏置电流模块提供稳定的电流。

53、可选的,所述基准电流模块包括:第十八nmos管、第十九nmos管、第二十nmos管、第十一pmos管以及第九电阻,其中:

54、所述第十八nmos管的漏极分别与所述第十一pmos管的漏极、所述第十一pmos管的栅极以及所述偏置电流模块的输入端相连接,所述第十八nmos管的栅极与所述第九电阻的一端相连接,所述第十八nmos管的栅极分别与所述第十九nmos管的栅极、所述第十九nmos管的漏极、所述第二十nmos管的栅极以及所述第二十nmos管的源极相连接;

55、所述第十一pmos管的源极以及所述第二十nmos管的漏极分别与直流电源相连接;

56、所述第十九nmos管的源极以及所述第九电阻的另一端分别接地。

57、通过采用技术方案,基准电流模块可为偏置电流模块提供稳定的电流。

58、可选的,所述迟滞比较器,还包括:所述驱动模块为前级驱动模块,其中:

59、所述前级驱动模块的一端分别与所述比较模块的第二端以及迟滞量控制模块的第二端相连接,所述前级驱动模块的另一端与所述前级驱动模块的第一端相连接,所述前级驱动模块用于滤除所述电压信号中的噪声干扰。

60、通过采用技术方案,前级驱动模块可以有效降低比较器输出的噪声,提高迟滞比较器输出信号的精度。

61、可选的,所述前级驱动模块包括:第十二pmos管、第十三pmos管、第十四pmos管、第二十一nmos管、第二十二nmos管以及第二十三nmos管,其中:

62、所述第二十二nmos管的栅极分别与所述第十二pmos管的栅极、所述第十三pmos管的栅极、所述第二十一nmos管的栅极、所述比较模块的第二端、所述迟滞量控制模块的第二端以及所述偏置电流模块的输出端相连接,所述第二十二nmos管的漏极分别与所述第十三pmos管的漏极、所述第二十三nmos管的栅极、所述第十四pmos管的栅极以及所述前级驱动模块的第一端相连接,所述第二十二nmos管的源极分别与所述第二十三nmos管的源极、所述第二十一nmos管的漏极相连接;

63、所述第十三pmos管的源极分别与所述第十四pmos管的源极、所述第十二pmos管的漏极相连接;

64、所述第十二pmos管的源极以及所述第二十三nmos管的漏极分别接直流电源;

65、所述第二十一nmos管的源极以及所述第十四pmos管的漏极分别接地。

66、通过采用该技术方案,前级驱动模块可以有效降低比较器输出的噪声,提高迟滞比较器输出信号的精度。

67、综上所述,本技术实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

68、当迟滞比较器在实际应用中存在各种干扰源时,可根据第二外部接口输入的迟滞量控制信号产生迟滞时长,相比于现有技术中,需要根据电路元件参数设置的固定迟滞量可能无法满足实际需求,而本技术实施例提供的迟滞比较器中的迟滞时长可根据输入的控制信号灵活调节。

- 还没有人留言评论。精彩留言会获得点赞!