采样复位电路和模拟前端电路的制作方法

本申请涉及采样复位电路,特别是涉及采样复位电路和模拟前端电路。

背景技术:

1、在模拟前端中,链路的线性度非常关键,其线性度会限制后面模数转换器的性能。模拟前端的线性度主要是由积分器,相关双采样电路以及保持电路共同决定的。积分器以及保持电路的线性度主要由自己的放大器性能决定,采样电路并没有放大器,所以它的线性度更需要得到保证。在相关技术中,通常需要增加额外的辅助放大器来提高链路线性度,导致采样复位电路功耗较高。

2、目前针对相关技术中采样复位电路的功耗高的问题,尚未提出有效的解决方案。

技术实现思路

1、本申请实施例提供了一种采样复位电路和模拟前端电路,以至少解决相关技术中解决了采样电路功耗高的问题。

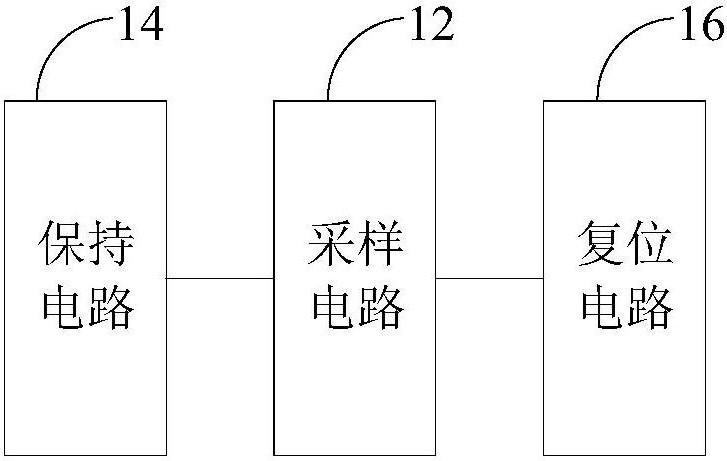

2、第一方面,本申请实施例提供了一种采样复位电路,所述采样复位电路包括:采样电路、保持电路和复位电路;

3、所述采样电路,分别连接所述保持电路和所述复位电路;

4、所述复位电路,用于在所述采样电路采样结束后,对所述采样电路的电位进行复位;其中,所述复位电路的复位电压设置为所述保持电路的最高电位。

5、在其中一些实施例中,所述采样电路包括采样电容;

6、所述采样电容的第一端分别连接所述保持电路的输入端和所述复位电路,且所述采样电容的第二端连接所述保持电路的输出端。

7、在其中一些实施例中,所述保持电路包括第一开关子电路和第二开关子电路;

8、所述第一开关子电路,用于在采样时段期间将所述保持电路的输入端与所述采样电容的第一端断开,并且在保持时段期间将所述保持电路的输入端与所述采样电容的第一端导通;

9、所述第二开关子电路,用于在所述采样时段期间将所述保持电路的输出端与所述采样电容的第二端断开,并且在所述保持时段期间将所述保持电路的输出端与所述采样电容的第二端导通。

10、在其中一些实施例中,所述第一开关子电路包括第一互补金属氧化物半导体(complementary metal oxide semiconductor,简称为cmos)开关,且所述第一cmos开关的栅极用于连接保持相信号;和/或,所述第二开关子电路包括第一n型金属氧化物半导体(nmetal oxide semiconductor,简称为nmos)开关,且所述第一nmos开关的栅极用于连接所述保持相信号。

11、在其中一些实施例中,所述采样电路包括采样电容;所述复位电路还包括第三开关子电路和第四开关子电路;

12、所述第三开关子电路,用于在采样时段期间将所述复位电路的复位电压与所述采样电容的第一端断开,并且在复位时段期间将所述复位电路与所述采样电容的第一端导通;

13、所述第四开关子电路,用于在所述采样时段期间和所述复位时段期间将所述采样电容的第二端与模拟地导通。

14、在其中一些实施例中,所述第三开关子电路包括第二cmos开关,且所述第二cmos开关的栅极用于连接复位信号;和/或,所述第四开关子电路包括第二nmos开关,且所述第二nmos开关的栅极用于连接所述复位信号。需要补充说明的是,当上述采样相信号、保持相信号均为0时,生成复位信号。

15、在其中一些实施例中,所述复位电路还包括第五开关子电路;

16、所述第五开关子电路,用于在所述采样时段期间和所述复位时段期间,将所述采样电容的第二端与所述模拟地导通。

17、在其中一些实施例中,所述采样电路还包括运算放大器;

18、所述运算放大器的输入端连接所述信号输入端,且所述运算放大器的输出端连接所述采样电容的第一端。

19、在其中一些实施例中,所述采样电路还包括采样开关子电路;

20、所述采样开关子电路在采样时段期间将所述运算放大器的输出端与所述采样电容的第一端导通,并且在保持时段期间将所述运算放大器的输出端与所述采样电容的第一端断开。

21、第二方面,本申请实施例提供了一种模拟前端电路,所述模拟前端电路包括模数转换器,以及如上述第一方面所述的采样复位电路;

22、所述模数转换器,连接所述采样复位电路中的保持电路,用于将所述保持电路输出的模拟信号进行模数转换处理,并生成信号处理结果。

23、相比于相关技术,本申请实施例提供了一种采样复位电路和模拟前端电路,该采样复位电路包括:采样电路、保持电路和复位电路;该采样电路分别连接该保持电路和该复位电路;该复位电路,用于在该采样电路采样结束后,对该采样电路的电位进行复位;其中,该复位电路的复位电压设置为该保持电路的最高电位,解决了采样电路功耗高的问题,实现了低功耗、安全的采样复位电路。

24、本申请的一个或多个实施例的细节在以下附图和描述中提出,以使本申请的其他特征、目的和优点更加简明易懂。

技术特征:

1.一种采样复位电路(52),其特征在于,所述采样复位电路(52)包括:采样电路(12)、保持电路(14)和复位电路(16);

2.根据权利要求1所述的采样复位电路(52),其特征在于,所述采样电路(12)包括采样电容(ccds);

3.根据权利要求2所述的采样复位电路(52),其特征在于,所述保持电路(14)包括第一开关子电路(s1)和第二开关子电路(s2);

4.根据权利要求3所述的采样复位电路(52),其特征在于,所述第一开关子电路(s1)包括第一cmos开关(cmos1),且所述第一cmos开关(cmos1)的栅极用于连接保持相信号;和/或,所述第二开关子电路(s2)包括第一nmos开关(nmos1),且所述第一nmos开关(nmos1)的栅极用于连接所述保持相信号。

5.根据权利要求1所述的采样复位电路(52),其特征在于,所述采样电路(12)包括采样电容(ccds);所述复位电路(16)还包括第三开关子电路(s3)和第四开关子电路(s4);

6.根据权利要求5所述的采样复位电路(52),其特征在于,所述第三开关子电路(s3)包括第二cmos开关(cmos2),且所述第二cmos开关(cmos2)的栅极用于连接复位信号;和/或,所述第四开关子电路(s4)包括第二nmos开关(nmos2),且所述第二nmos开关(nmos2)的栅极用于连接所述复位信号。

7.根据权利要求5所述的采样复位电路(52),其特征在于,所述复位电路(16)还包括第五开关子电路;

8.根据权利要求1至7任一项所述的采样复位电路(52),其特征在于,所述采样电路(12)还包括运算放大器和采样电容(ccds);

9.根据权利要求8所述的采样复位电路(52),其特征在于,所述采样电路(12)还包括采样开关子电路(s5);

10.一种模拟前端电路,其特征在于,所述模拟前端电路包括模数转换器(54),以及如权利要求1至9任一项所述的采样复位电路(52);

技术总结

本申请涉及一种采样复位电路和模拟前端电路,其中,该采样复位电路包括:采样电路、保持电路和复位电路;该采样电路分别连接该保持电路和该复位电路;该复位电路,用于在该采样电路采样结束后,对该采样电路的电位进行复位;其中,该复位电路的复位电压设置为该保持电路的最高电位。通过本申请,解决了采样电路功耗高的问题,实现了低功耗、安全的采样复位电路。

技术研发人员:邬蓉,池浩

受保护的技术使用者:上海联影微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!