一种高可靠抗辐射反熔丝开关单元结构的制作方法

本发明涉及微电子集成电路,特别涉及一种高可靠抗辐射反熔丝开关单元结构。

背景技术:

1、随着航空航天、雷达、导弹、船舶、电子对抗、通信领域等各大重点工程要求电子系统向多功能、高速率、小型化及低功耗方向发展,对高可靠、抗辐射的可编程逻辑器件的需求愈发突出。

2、在实现可编程逻辑器件及内核的基本组成单元中,sram开关单元存在着抗辐射性能差、功耗高、易失性等问题,flash开关单元存在着速度慢、编程电压高等问题。相比之下,反熔丝开关单元在高可靠、抗辐射等方面具有先天的优势,这对军事和宇航应用具有特别的吸引力。

技术实现思路

1、本发明的目的在于提供一种高可靠抗辐射反熔丝开关单元结构,以解决传统开关单元可靠性低、抗辐射性能差的问题,提升反熔丝开关单元器件信号驱动能力以及增强其驱动能力可调的灵活性。

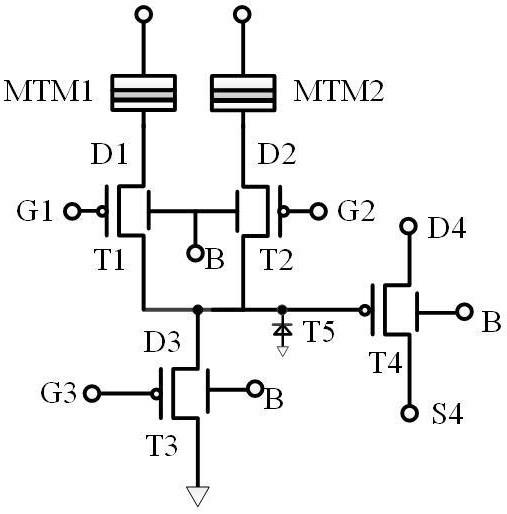

2、为解决上述技术问题,本发明提供了一种高可靠抗辐射反熔丝开关单元结构,包括第一反熔丝器件、第二反熔丝器件、第一高压pmos管、第二高压pmos管、第三高压pmos管及pmos型信号传输管;

3、所述第一反熔丝器件和所述第二反熔丝器件均包括上极板和下极板;所述第一反熔丝器件的上极板和所述第二反熔丝器件的上极板连接电源,所述第一反熔丝器件的下极板与第一高压pmos管的漏端相连,所述第二反熔丝器件的下极板与第二高压pmos管的漏端相连;

4、所述第一高压pmos管的源端、所述第二高压pmos管的源端均同时与第三高压pmos管的漏端以及pmos型信号传输管的栅极相连;所述第三高压pmos管的源端接地;所述第一高压pmos管的栅端、所述第二高压pmos管的栅端和所述第三高压pmos管的栅端均接电平信号;

5、所述第一高压pmos管、所述第二高压pmos管、所述第三高压pmos管和所述pmos型信号传输管共衬底;

6、通过对所述第一反熔丝器件、所述第二反熔丝器件编程形成开态,与所述第一高压pmos管、所述第二高压pmos管形成通路,实现控制信号对pmos型信号传输管的栅极电位控制,最终实现pmos型信号传输管的开/关态;

7、所述高可靠抗辐射反熔丝开关单元结构采用旁路二极管进行栅极保护,以预防瞬间vpp信号编程电压对地形成通路时,高压对pmos型信号传输管的管栅造成损伤;所述旁路二极管的负极同时连接所述第一高压pmos管的源端、所述第二高压pmos管的源端、第三高压pmos管的漏端以及pmos型信号传输管的栅极,所述旁路二极管的正极接地。

8、在一种实施方式中,所述第一反熔丝器件和所述第二反熔丝器件同为ono型,或同为mtm型,或同为xpm型结构。

9、在一种实施方式中,对所述第一反熔丝器件的编程,是通过开启第一高压pmos管和第三高压pmos管,实现编程电压vpp信号加载到第一反熔丝器件的上极板,进而形成开态;

10、对所述第二反熔丝器件的编程,是通过开启第二高压pmos管和第三高压pmos管,实现编程电压vpp信号加载到第二反熔丝器件的上极板,进而形成开态。

11、在一种实施方式中,所述pmos型信号传输管实现开态的操作步骤有两种;

12、第一种:(1)对第一反熔丝器件的编程形成开态,(2)对第二反熔丝器件的未编程形成关态,(3)对第一高压pmos管的漏端和栅端施加电压0v,对第二高压pmos管的漏端和栅端分别施加电压vdd和0v,对第三高压pmos管的栅端施加电压vdd,对共同衬底施加电压vdd,此时传递至pmos型信号传输管的栅端电位为0v,由此实现pmos型信号传输管的开态;

13、第二种:(1)对第一反熔丝器件的未编程形成关态,(2)对第二反熔丝器件的编程形成开态,(3)对第一高压pmos管的漏端和栅端分别施加电压vdd和0v,对第二高压pmos管的漏端和栅端施加电压0v,对第三高压pmos管的栅端施加电压vdd,对共同衬底施加电压vdd,此时传递至pmos型信号传输管的栅端电位为0v,由此实现pmos型信号传输管的开态。

14、在一种实施方式中,所述pmos型信号传输管实现关态的操作步骤有两种;

15、第一种:(1)对第一反熔丝器件的编程形成开态,(2)对第二反熔丝器件的未编程形成关态,(3)对第一高压pmos管的漏端和栅端分别施加电压vdd和0v,对第二高压pmos管的漏端和栅端施加电压0v,对第三高压pmos管的栅端施加电压vdd,对共同衬底施加电压vdd,此时传递至pmos型信号传输管的栅端电位为vdd,由此实现pmos型信号传输管的关态;

16、第二种:(1)对第一反熔丝器件的未编程形成关态,(2)对第二反熔丝器件的编程形成开态,(3)对第一高压pmos管的漏端和栅端施加电压0v,对第二高压pmos管的漏端和栅端分别施加电压vdd和0v,对第三高压pmos管的栅端施加电压vdd,对共同衬底施加电压vdd,此时传递至pmos型信号传输管的栅端电位为vdd,由此实现pmos型信号传输管的关态。

17、本发明提供的一种高可靠抗辐射反熔丝开关单元结构,结构简单、体积小、速度快、功耗低、与cmos工艺兼容,且具有高度可靠性和良好的抗辐射性等优势,可以广泛应用于航空、航天、兵器、船舶领域下空间环境的抗辐射非易失性存储器或可编程阵列逻辑器件。

技术特征:

1.一种高可靠抗辐射反熔丝开关单元结构,其特征在于,包括第一反熔丝器件、第二反熔丝器件、第一高压pmos管、第二高压pmos管、第三高压pmos管及pmos型信号传输管;

2.如权利要求1所述的高可靠抗辐射反熔丝开关单元结构,其特征在于,所述第一反熔丝器件和所述第二反熔丝器件同为ono型,或同为mtm型,或同为xpm型结构。

3.如权利要求1所述的高可靠抗辐射反熔丝开关单元结构,其特征在于,对所述第一反熔丝器件的编程,是通过开启第一高压pmos管和第三高压pmos管,实现编程电压vpp信号加载到第一反熔丝器件的上极板,进而形成开态;

4.如权利要求1所述的高可靠抗辐射反熔丝开关单元结构,其特征在于,所述pmos型信号传输管实现开态的操作步骤有两种;

5.如权利要求1所述的高可靠抗辐射反熔丝开关单元结构,其特征在于,所述pmos型信号传输管实现关态的操作步骤有两种;

技术总结

本发明公开一种高可靠抗辐射反熔丝开关单元结构,属于微电子集成电路领域。第一反熔丝器件的下极板与第一高压PMOS管的漏端相连,第二反熔丝器件的下极板与第二高压PMOS管的漏端相连;第一高压pMOS管的源端、第二高压pMOS管的源端均同时与第三高压PMOS管的漏端以及pMOS型信号传输管的栅极相连;第三高压PMOS管的源端接地;通过对第一反熔丝器件、第二反熔丝器件编程形成开态,与第一高压pMOS管、第二高压pMOS管形成通路,实现控制信号对pMOS型信号传输管的栅极电位控制,最终实现pMOS型信号传输管的开/关态。本发明结构简单,与CMOS工艺兼容,具有高度可靠性和抗辐射性,适用于空间环境的抗辐射非易失性存储器或可编程阵列逻辑器件。

技术研发人员:李幸和,刘国柱,魏轶聃

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!