增量型SDM积分器的制作方法

本发明属于集成电路,具体涉及一种增量型sdm积分器。

背景技术:

1、在低osr(over sampling ratio,过采样率)下的增量型sdm积分器(incrementalsigma-delta modulator)应用中,传统chop技术无法很好的抑制运放失调(offset)带来的影响,前级积分器的运放失调依然会被后级积分器积分,导致增量型sdm积分器的失调过大,影响adc的dc测量精度。

2、因此,针对上述技术问题,有必要提供一种增量型sdm积分器。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种增量型sdm积分器,以降低或消除增量型sdm积分器的输出失调。

2、为了实现上述目的,本发明一实施例提供的技术方案如下:

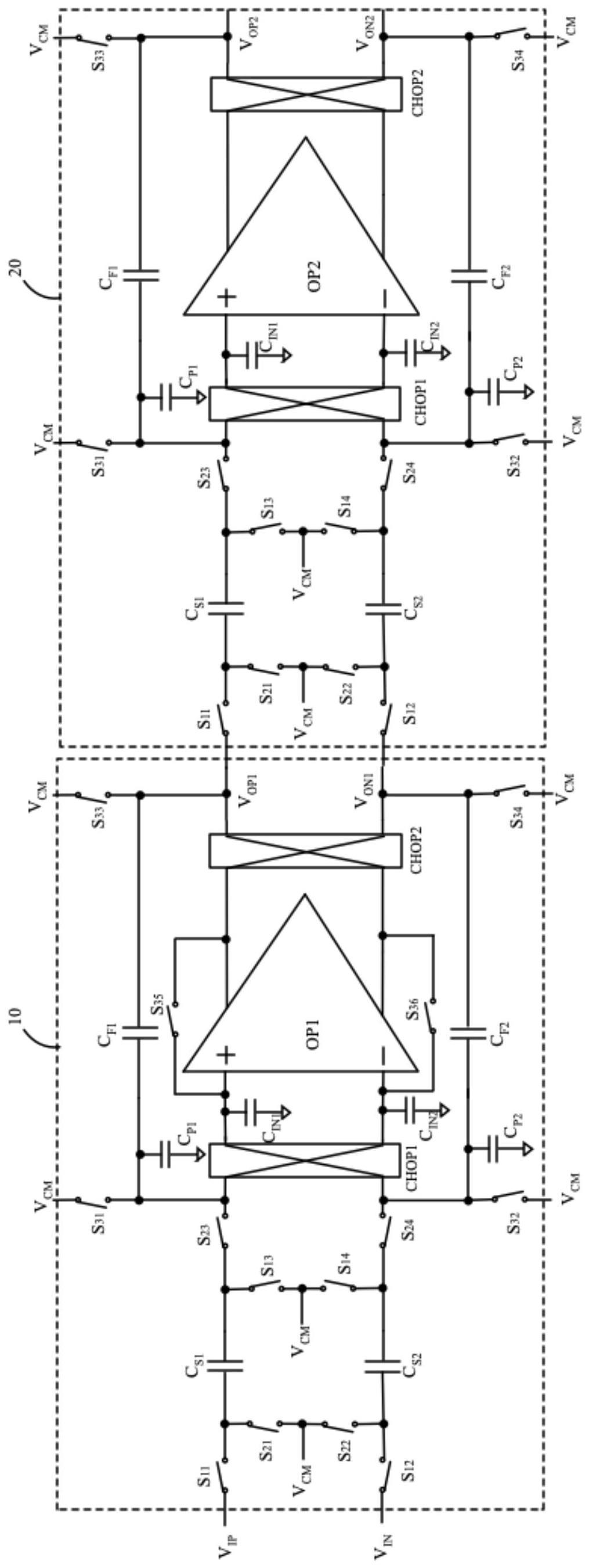

3、一种增量型sdm积分器,所述sdm积分器包括级联设置的若干第一积分器及一个第二积分器,所述第一积分器和第二积分器分别包括运放、斩波器、采样电容、反馈电容、若干时序开关及若干复位开关,其中:

4、所述斩波器包括与运放输入端相连的第一斩波器及与运放输出端相连的第二斩波器;

5、所述采样电容的第一极板与输入信号相连,第二极板与第一斩波器的输入端相连;

6、所述反馈电容的第一极板与第二斩波器的输出端相连,第二极板与第一斩波器的输入端相连;

7、所述时序开关包括第一时序开关及第二时序开关,第一时序开关的第一端和第二端分别与输入信号和采样电容的第一极板相连、或与采样电容的第二极板和基准电压相连,第二时序开关的第一端和第二端分别与基准电压和采样电容的第一极板相连、或与采样电容的第二极板和第一斩波器的输入端相连;

8、所述复位开关包括第一复位开关、第二复位开关及第三复位开关,第一复位开关的第一端和第二端分别与基准电压和第一斩波器的输入端相连,第二复位开关的第一端和第二端分别与基准电压和第二斩波器的输出端相连,第三复位开关的第一端和第二端分别与运放的输出端和运放的输入端相连。

9、一实施例中,所述第一时序开关和第二时序开关分别通过非交叠的第一时钟信号φ1和第二时钟信号φ2控制,所述第一斩波器与第二斩波器通过斩波信号chop进行控制,所述复位开关通过复位信号rst进行控制。

10、一实施例中,所述第一时钟信号φ1和第二时钟信号φ2的周期为t,斩波信号chop的周期为2n*t,n≥2,且每个斩波信号chop周期内,至少有相邻的两个时间段t同为高电平或低电平。

11、一实施例中,所述第一时钟信号φ1和第二时钟信号φ2的周期为t,斩波信号chop的周期为4t,且每个斩波信号chop周期内,有相邻的两个时间段t同为高电平或低电平。

12、一实施例中,所述第一积分器及第二积分器输出端的差模电压分别为:

13、于第一个时段t内,第一积分器输出端的差模电压由va+vos跳变为va+vc+vos,第二积分器输出端的差模电压由0跳变为va+vos;

14、于第二个时段t内,第一积分器输出端的差模电压由vc-vos-va跳变为-vos-va,第二积分器输出端的差模电压由va+vos跳变为vc;

15、于第三个时段t内,第一积分器输出端的差模电压由-vos-va跳变为-vos-va-vc,第二积分器输出端的差模电压由vc跳变为vc-vos-va;

16、于第四个时段t内,第一积分器输出端的差模电压由va+vos-vc跳变为va+vos,第二积分器输出端的差模电压由vc-vos-va跳变为0;

17、其中,vos运放输出端的初始差模电压,cs为采样电容的容值,cf为反馈电容的容值,cp为反馈电容的下极板与地电位之间产生的寄生电容的容值。

18、一实施例中,所述运放的第一输入端与地电位之间产生有第一寄生电容cin1,运放的第二输入端与地电位之间产生有第二寄生电容cin2,第一寄生电容cin1和第一寄生电容cin2的容值均为cin。

19、一实施例中,所述采样电容包括:

20、第一采样电容cs1,第一极板与第一输入信号vip相连,第二极板与第一斩波器的第一输入端相连;

21、第二采样电容cs2,第一极板与第二输入信号vin相连,第二极板与第一斩波器的第二输入端相连;

22、其中,所述第一采样电容cs1和第二采样电容cs2的容值均为cs。

23、一实施例中,所述反馈电容包括:

24、第一反馈电容cf1,第一极板与第二斩波器的第一输出端相连,第二极板与第一斩波器的第一输入端相连,第二极板为下极板,第二极板与地电位之间产生有第三寄生电容cp1;

25、第二反馈电容cf2,第一极板与第二斩波器的第二输出端相连,第二极板与第一斩波器的第二输入端相连,第二极板为下极板,第二极板与地电位之间产生有第四寄生电容cp2;

26、其中,所述第一反馈电容cf1和第二反馈电容cf2的容值均为cf,第三寄生电容cp1和第四寄生电容cp2的容值均为cp。

27、一实施例中,所述第一时序开关包括:

28、第一开关s11,第一端和第二端分别与第一输入信号vip和第一采样电容cs1的第一极板相连;

29、第二开关s12,第一端和第二端分别与第二输入信号vin和第二采样电容cs2的第一极板相连;

30、第三开关s13,第一端和第二端分别与第一采样电容cs1的第二极板和基准电压vcm相连;

31、第四开关s14,第一端和第二端分别与第二采样电容cs2的第二极板和基准电压vcm相连;

32、所述第二时序开关包括:

33、第五开关s21,第一端和第二端分别与基准电压vcm和第一采样电容cs1的第一极板相连;

34、第六开关s22,第一端和第二端分别与基准电压vcm和第二采样电容cs2的第一极板相连;

35、第七开关s23,第一端和第二端分别与第一采样电容cs1的第二极板和第一斩波器的第一输入端相连;

36、第八开关s24,第一端和第二端分别与第二采样电容cs2的第二极板和第一斩波器的第二输入端相连。

37、一实施例中,所述第一复位开关包括:

38、第九开关s31,第一端和第二端分别与基准电压vcm和第一反馈电容cf1的第二极板相连;

39、第十开关s32,第一端和第二端分别与基准电压vcm和第二反馈电容cf2的第二极板相连;

40、所述第二复位开关包括:

41、第十一开关s33,第一端和第二端分别与基准电压vcm和第一反馈电容cf1的第一极板相连;

42、第十二开关s34,第一端和第二端分别与基准电压vcm和第二反馈电容cf2的第一极板相连;

43、所述第三复位开关包括:

44、第十三开关s35,第一端和第二端分别与运放的第一输出端和运放的第一输入端相连;

45、第十四开关s36,第一端和第二端分别与运放的第二输出端和运放的第二输入端相连。

46、一实施例中,所述sdm积分器包括级联设置的一个第一积分器及一个第二积分器;或,

47、所述sdm积分器包括级联设置的多个第一积分器及一个第二积分器。

48、本发明具有以下有益效果:

49、本发明通过调整积分器的chop时序和复位方式,可以有效降低或消除增量型sdm积分器的输出失调。

- 还没有人留言评论。精彩留言会获得点赞!