电容器加权分段缓冲器的制作方法

本发明涉及缓冲电路设计,更具体地,涉及一种低功耗、超小面积、高精度的电容加权分段缓冲器。

背景技术:

1、数模转换器(digital-to-analog converter,dac)用于将数字输入转换为模拟输出。缓冲器用于缓冲或驱动模拟输入以生成模拟输出并将其输出到后续处理级。dac和缓冲器是多种电路中的常见组件。一般来说,缓冲器可以分为开环缓冲器和闭环缓冲器。开环缓冲器会受到工艺、电压、温度(process,voltage,temperature,pvt)变化的影响。此外,典型的电路设计通常使用单独的dac与开环缓冲器一起工作,由于缺乏集成而导致芯片面积较大。闭环缓冲器以牺牲速度和能量为代价来实现所需的稳定性/相位裕度性能(phasemargin performance)。因此,需要一种低功耗、超小面积、高准确度(accuracy)的创新的缓冲器。

2、如上所述,dac和缓冲器是多种电路中的常见组件。例如,人工智能(artificialintelligence,ai)应用使用的卷积神经网络(convolutional neural network,cnn))由具有可学习权重的神经元(neuron)组成。每个神经元接收ai输入,并对ai输入和权重执行点积(dot product)(即卷积运算)。一种传统方法采用中央处理单元(cpu)来处理卷积运算,这不是一种节能的解决方案。另一种传统方法可以采用逐位的(bit-wise)基于电流或基于时间的存算一体(compute-in-memory,cim)电路来处理卷积运算,这既不是节能解决方案也不是高准确度解决方案。因此,需要一种低功耗、超小面积和高准确度的创新缓冲器,以满足ai应用所使用的acim电路的要求。

技术实现思路

1、本发明的目的之一是提供一种低功耗、超小面积、高准确度的电容器加权分段缓冲器(capacitor weighted segmentation buffer)。例如,电容器加权分段缓冲器可以与数模转换器集成在一起。又例如,电容器加权分段缓冲器可以是模拟的cim缓冲器。

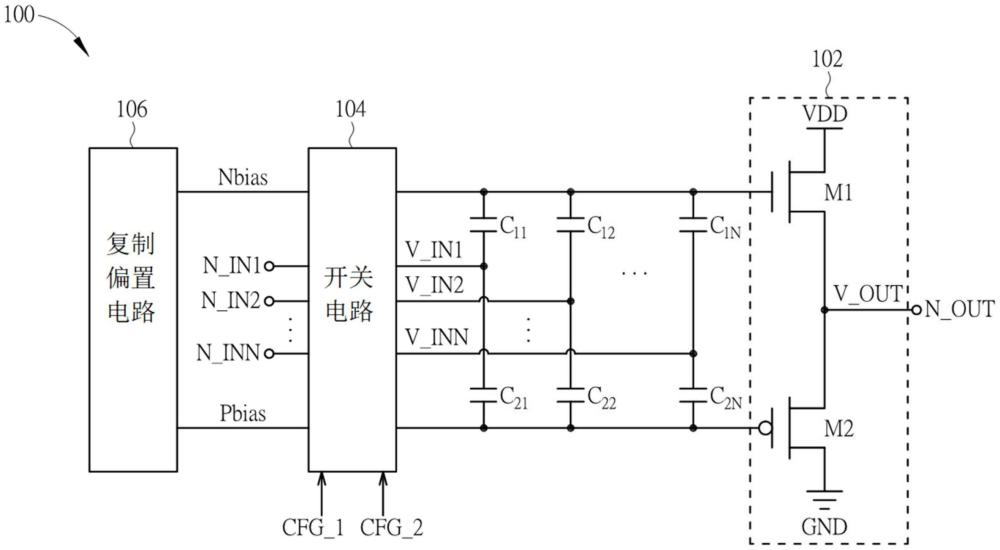

2、根据本发明的一方面,公开了示例性电容器加权分段缓冲器。示例性电容器加权分段缓冲器包括推挽式缓冲器电路和多个电容器。推挽式缓冲电路包括第一晶体管和第二晶体管,第一晶体管具有控制端、第一连接端和第二连接端,第二晶体管具有控制端、第一连接端和第二连接端,其中第一晶体管的第二连接端和第二晶体管的第二连接端耦接至电容器加权分段缓冲器的输出节点。电容器包括第一电容器,第二电容器,第三电容器和第四电容器,第一电容器具有耦接到第一晶体管的控制端的第一端和布置成接收电容器加权分段缓冲器的第一输入信号的第二端;第二电容器具有耦接到第二晶体管的控制端的第一端以及布置成接收电容器加权分段缓冲器的第一输入信号的第二端;第三电容器具有耦接到第一晶体管的控制端的第一端,以及布置成接收电容器加权分段缓冲器的第二输入信号的第二端;第四电容器具有耦接到第二晶体管的控制端的第一端和布置成接收电容器加权分段缓冲器的第二输入信号的第二端。第一电容器和第二电容器中的每个电容器具有第一电容值,并且第三电容器和第四电容器中的每个电容器具有不同于第一电容值的第二电容值。

3、在阅读了以下对各个附图和附图中示出的优选实施例的详细描述之后,本发明的这些和其他目的对于本领域普通技术人员来说无疑将变得显而易见。

技术特征:

1.一种电容器加权分段缓冲器,其特征在于,包括:

2.根据权利要求1所述的电容器加权分段缓冲器,其特征在于,所述多个电容器进一步包括:

3.根据权利要求1所述的电容器加权分段缓冲器,其特征在于,还包括:

4.根据权利要求3所述的电容器加权分段缓冲器,其特征在于,还包括:

5.根据权利要求4所述的电容器加权分段缓冲器,其特征在于,当所述推挽式缓冲器电路操作在所述缓冲模式时,所述复制偏置电路与所述推挽式缓冲器电路断开连接。

6.根据权利要求3所述的电容加权分段缓冲器,其特征在于,当所述推挽式缓冲电路操作在所述缓冲模式时,所述第一输入信号被传送至所述第一电容器的第二端和所述第二电容器的第二端;以及当所述推挽式缓冲器电路操作在所述缓冲模式时,所述第二输入信号被传送至所述第三电容器的第二端和所述第四电容器的第二端。

7.根据权利要求6所述的电容器加权分段缓冲器,其特征在于,当所述推挽式缓冲器电路操作在所述重置模式时,所述第一输入信号与所述第一电容器和所述第二电容器断开,且所述第二输入信号与所述第三电容器和所述第四电容器断开。

8.根据权利要求3所述的电容器加权分段缓冲器,其特征在于,当所述推挽式缓冲器电路操作于所述重置模式时,共模电压被传送到所述第一电容器的第二端,所述第二电容器的第二端,和所述第三电容器的第二端以及所述第四电容器的第二端。

9.根据权利要求1所述的电容器加权分段缓冲器,其特征在于,所述电容器加权分段缓冲器与数模转换器(dac)集成在一起。

10.根据权利要求9所述的电容器加权分段缓冲器,其特征在于,所述dac包括:

11.根据权利要求10所述的电容器加权分段缓冲器,其特征在于,所述cdac包括:

12.根据权利要求11所述的电容器加权分段缓冲器,其特征在于,所述数字码是神经网络的一个输入数据。

13.根据权利要求9所述的电容器加权分段缓冲器,其特征在于,所述电容器加权分段缓冲器的输出节点被耦接到模拟存算一体(acim)电路。

14.根据权利要求1所述的电容器加权分段缓冲器,其特征在于,所述电容器加权分段缓冲器是模拟acim电路的缓冲器。

15.根据权利要求14所述的电容器加权分段缓冲器,其特征在于,所述第一输入信号和所述第二输入信号中的每一个输入信号是从acim电路产生的,并且所述acim电路包括:

16.根据权利要求15所述的电容器加权分段缓冲器,其特征在于,所述多个处理电路中的每个处理电路是乘法累加(mac)电路。

17.根据权利要求15所述的电容器加权分段缓冲器,其特征在于,每个模拟输入对应于神经网络的一个输入数据。

技术总结

本发明提供一种电容器加权分段缓冲器,包括:推挽式缓冲电路,包括:第一晶体管,第二晶体管和多个电容器,其中第一晶体管的第二连接端和第二晶体管的第二连接端耦接至电容器加权分段缓冲器的输出节点,多个电容器包括:第一电容器,具有耦接到第一晶体管的控制端的第一端,以及用于接收所述电容器加权分段缓冲器的第一输入信号的第二端;第二电容器,具有耦接到第二晶体管的控制端的第一端,以及用于接收所述第一输入信号的第二端;第三电容器,具有耦接到第一晶体管的控制端的第一端,以及用于接收电容器加权分段缓冲器的第二输入信号的第二端;以及第四电容器,具有耦接到第二晶体管的控制端的第一端,以及用于接收第二输入信号的第二端。

技术研发人员:谢颂恩

受保护的技术使用者:联发科技股份有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!