一种应用于分段式逐次逼近模数转换器的权重误差校准方法

本发明涉及微电子学与固体电子学领域,特别是该领域中分段电容型逐次逼近模数转换器中由寄生电容带来的权重误差的校准方法。

背景技术:

1、近几年集成电路领域发展迅速,集成电路主要包含数字集成电路与模拟集成电路两大类。自然界信号主要为模拟信号。而如今的存储器与计算设备主要处理数字信号。模数转换器(analog-to-digital converter,adc)以及数模转换器(digital to analogconverter,dac)为数字与模拟沟通的桥梁,在集成电路领域具有不可或缺的地位。adc有很多种不同的结构,在这些结构中逐次逼近型模数转换器(successive-approximation-register adc,sar adc),具有功耗低、速度较快、面积较小、容易与其它adc结构组成混合结构等优势而成为热门的研究方向。随着sar adc精度的升高,电容或电阻阵列中元件个数呈指数率升高,同时占用芯片的面积也会呈现指数上升,提高了生产成本。使得进一步提高adc精度变得困难。将传统adc中的电容阵列拆解并通过桥电容连接组合成为分段式电容阵列adc可以大大降低达到高精度所需要的电容数量,降低adc中电容阵列所占用的芯片面积。但分段式电容阵列adc对桥电容极板到地寄生以及桥电容两端并联寄生电容较为敏感,会导致分段电容阵列每一段之间出现权重误差,导致adc有效位数下降。本发明针对saradc中的分段式电容阵列采用一种基于误差电压的权重误差校准方法,从而减轻分段电容阵列中两种寄生电容对权重的影响。

技术实现思路

1、本发明针对现有分段式电容阵列sar adc设计中寄生电容带来的权重误差,提出一种基于误差电压的权重误差校准方法。

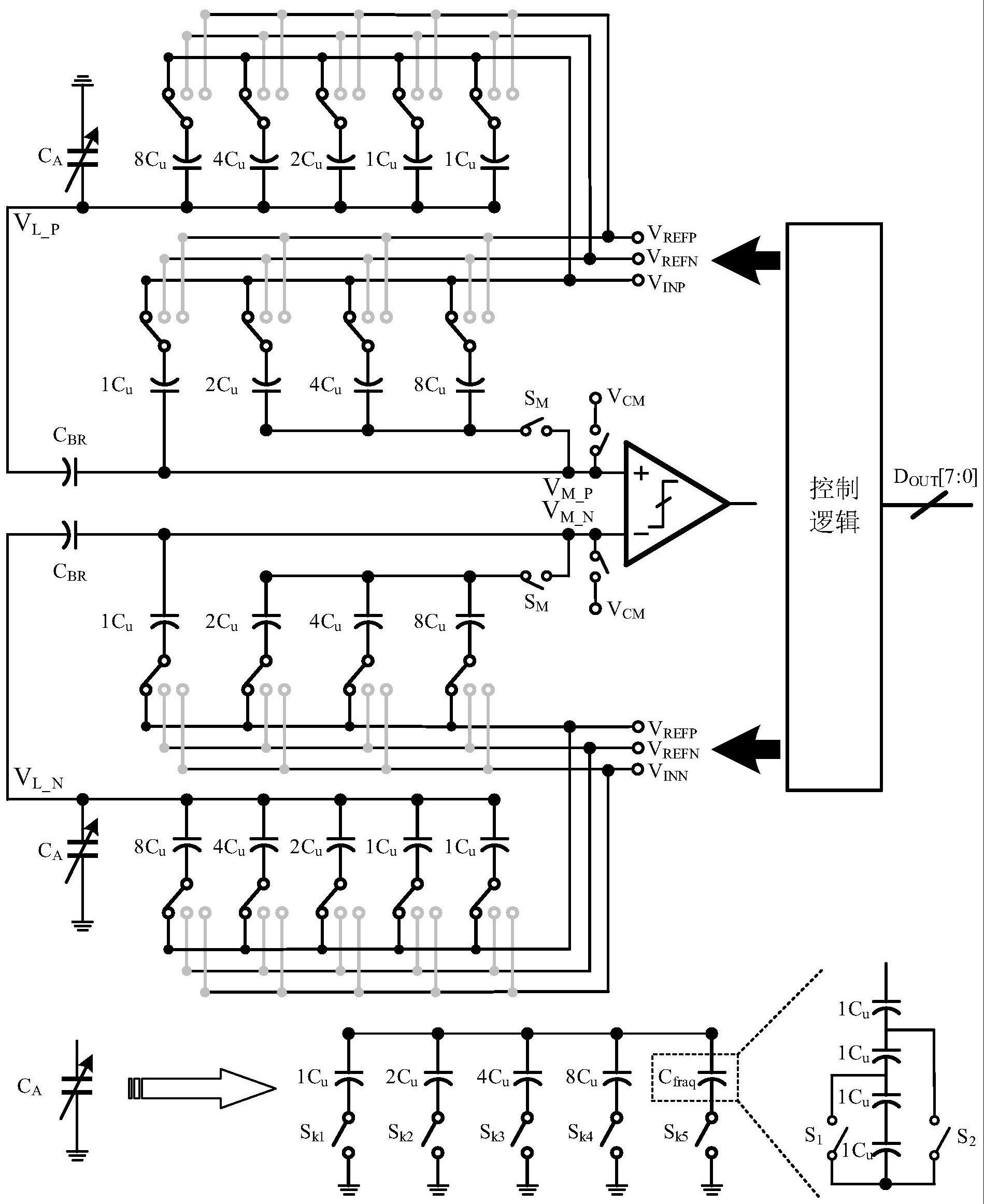

2、本发明技术方案为:一种应用于分段式逐次逼近模数转换器的权重误差校准方法,所述分段式逐次逼近模数转换器包括:比较器、p端阵列、n端阵列、控制逻辑单元;比较器正输入端和负输入端都通过开关连接共模参考电压vcm;

3、比较器正输入端连接p端阵列,p端阵列由l比特组成的lsb阵列、桥电容cbr和由m比特组成的msb阵列构成;adc有效位数n=m+l;设比较器负输入端连接n端阵列,n端阵列与p端阵列呈镜像关系;

4、msb阵列包含2m-1个单位电容cu,电容分组为:1cu、2cu、4cu、…、2p-1cu;除1cu上极板直接连接比较器外,其余电容上极板共接后通过开关sm连接比较器,每组电容的下极板组内共接后通过开关连接正参考电压vrefp、负参考电压vrefn或差分正端输入电压vinp;

5、lsb阵列包含2l个单位电容cu,电容分组为:1cu、1cu、2cu、4cu、…、2p-1cu,所有电容上极板连接比较器,每组电容的下极板组内共接后通过开关连接vrefp、vrefn或vinp信号;lsb阵列上极板共接点与msb阵列上极板共接点之间设置桥电容cbr;

6、在lsb电容阵列上极板添加校准dac阵列ca,ca由p比特单位电容cu组成的二进制阵列、校准结构cfraq以及接地开关组sk组成,p比特单位电容cu组成的二进制阵列分组为:1cu、2cu、4cu、…、2p-1cu,每组电容下极板组内共接后通过一个开关ski接地;校准结构cfraq包括:串联的四个单位电容和两个开关s1、s2;四个单位电容依次为第一到第四单位电容,第一单位电容的上极板连接第二单位电容的下极板,第二单位电容上极板连接第三单位电容下极板,第三单位电容上极板连接第四单位电容下极板;开关s1、s2的一端都连接在第一个单位电容的下极板,开关s1的另一端连接第二单位电容与第三单位电容之间,开关s2的另一端连接第三单位电容与第四单位电容之间,第四单位电容的上极板和p比特单位电容cu组成的二进制阵列中的所有电容上极板共接后与lsb电容阵列连接;通过控制开关s1、s2产生不同的电容值cu/4、cu/2、3cu/2;通过控制开关ski、s1、s2调整校准dac阵列ca的等效电容值;vrefp、vrefn或vinp信号由控制逻辑单元输出;

7、权重误差校准的步骤为:

8、步骤1:断开p端和n端开关sm;

9、步骤2:p端阵列和n端阵列的msb阵列上极板连通vcm,单位电容cu下极板连接参考电压vrefp,lsb阵列所有权电容电容下极板连接参考电压vrefn;待电压稳定后,断开p端阵列和n端阵列的上极板的vcm开关;

10、步骤3:p端阵列和n端阵列的msb阵列中单位电容cu下极板切换为vrefn,同时lsb阵列所有电容下极板切换为vrefp;

11、步骤4:待比较器两端电压稳定后,比较器两端的电压差即为权重误差引起的电压差;sar逻辑读取比较器输出数字值,并根据比较器结果控制校准dac阵列ca中的开关sk s1s2从而调整ca的电容值;

12、步骤5:重复步骤2到步骤4,最终校准dac阵列ca会收敛到固定值,完成校准步骤。

13、本发明提出的基于误差电压的权重误差校准方法,通过添加开关msb阵列开关sm放大了权重误差带来的电压误差,降低了比较器的要求。开关sm也使得单位电容cu在校准阶段和校准结束的工作阶可以共用,节约了芯片面积。lsb阵列添加的校准结构cfraq通过四个电容和两个开关的组合产生多种不同的电容值,既使用了单位电容cu保证了电容的匹配,又降低了芯片面积。传统方法使用单位电容cu产生cu/4电容需要4个串联的cu,产生cu/2需要2个串联的cu,产生3cu/2需要两个串联的cu并联一个cu。总共需要4+2+3=9个单位电容。本发明的校准方案为前台校准方法,校准完成后并不会降低工作时的转换速度。

技术特征:

1.一种应用于分段式逐次逼近模数转换器的权重误差校准方法,所述分段式逐次逼近模数转换器包括:比较器、p端阵列、n端阵列、控制逻辑单元;比较器正输入端和负输入端都通过开关连接共模参考电压vcm;

技术总结

本发明公开了一种应用于分段式逐次逼近模数转换器的权重误差校准方法,涉及微电子学与固体电子学领域,特别是该领域中分段电容型逐次逼近模数转换器中由寄生电容带来的权重误差的校准方法。本发明提出的方法MSB阵列不需要添加额外的电容,仅需要添加开关S<subgt;k</subgt;以降低比较器设计难度。同时LSB部分需要添加校准DAC阵列C<subgt;A</subgt;。C<subgt;A</subgt;由P比特单位电容C<subgt;u</subgt;组成(C<subgt;u</subgt;2C<subgt;u</subgt; 4C<subgt;u</subgt;…2<supgt;P‑1</supgt;C<subgt;u</subgt;)的二进制阵列、校准结构C<subgt;fraq</subgt;以及接地开关S<subgt;k</subgt;组成。校准结构C<subgt;fraq</subgt;又包括了四个单位电容和两个开关S<subgt;1</subgt;S<subgt;2</subgt;。通过控制开关S<subgt;1</subgt;S<subgt;2</subgt;可以产生不同的电容值C<subgt;u</subgt;/4,C<subgt;u</subgt;/2,3C<subgt;u</subgt;/2可以降低面积消耗。此结构可以将误差降低到LSB/4。既提降低了ADC的权重误差,提高了ADC的有效位数,又不会过度提高比较器的增益要求(提高设计难度同时增大功耗)。

技术研发人员:樊华,刘翼霖,张伟,罗静,赵攀峰,冯全源

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!