一种多输出忆阻器等效电路、应用系统及控制方法与流程

本发明涉及电子线路,特别涉及一种多输出忆阻器等效电路、应用系统及控制方法。

背景技术:

1、忆阻器是一种具有记忆功能的非线性电阻,通过控制电流或电压来改变电阻值,被认为是除电阻、电容、电感之外的第四种基本无源电子器件。忆阻器器件具有结构简单、尺寸小、能耗低、密度高和非易失性等特点,并且因其独特的电学特性在阻变存储、人工神经网络和人工智能中有着良好的应用前景。

2、然而忆阻器器件的制造成本高、制造条件要求严格,具有商业价值的忆阻器成本较高、短时间内通过大量制备忆阻器实体,以满足工程应用不现实。因此,通过仿真模型来分析研究忆阻特性和潜在应用价值具有十分重要的意义,不仅降低了制备忆阻器的成本,还有助于减少复杂环境对忆阻器产生的影响。而忆阻器的等效电路实现或是难以实现高阶精度忆阻,亦或是需要动用大量元器件,不利于电路系统的小型化设计。

技术实现思路

1、为了降低三阶忆阻器等效电路的复杂程度,本发明采用的技术方案如下:

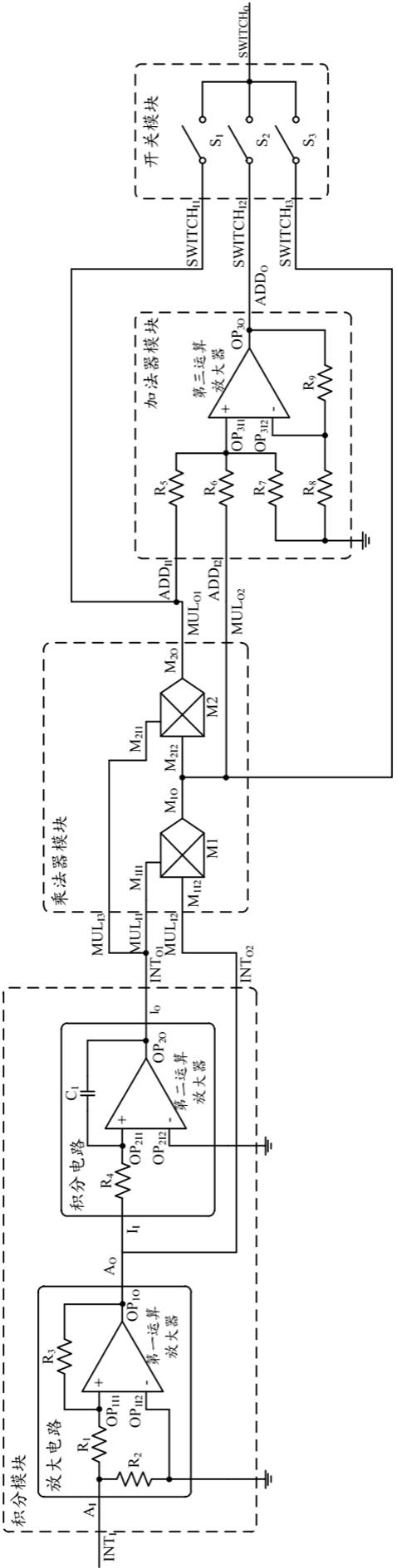

2、第一方面,提供一种多输出忆阻器等效电路,包括:积分模块,乘法器模块,加法器模块,开关模块;

3、积分模块的积分输入端作为等效电路输入端;积分模块的第一积分输出端与乘法器模块的第一乘法输入端和第三乘法输入端电性连接,积分模块的第二积分输出端与乘法器模块的第二乘法输入端电性连接;乘法器模块的第一乘法输出端与加法器模块的第一加法输入端电性连接,第二乘法输出端与加法器模块的第二加法输入端电性连接,加法器模块的加法输出端与开关模块的第二开关输入端电性连接,开关模块的第一开关输入端与第一乘法输出端电性连接,开关模块的第三开关输入端与第二乘法输出端电性连接,开关模块的开关输出端作为等效电路输出端。

4、进一步地,积分模块包括:放大电路、积分电路;

5、放大电路的放大电路输入端作为积分输入端,放大电路的放大电路输出端与积分电路的积分电路输入端电性连接后作为第二积分输出端,积分电路的积分电路输出端作为第一积分输出端。

6、进一步地,放大电路包括:第一运算放大器、第一电阻、第二电阻、第三电阻;

7、第一运算放大器的第一运放第一输入端与第一电阻的一端电性连接,第一电阻的另一端作为放大电路输入端,第一运算放大器的第一运放第二输入端与第二电阻的一端电性连接后接地,第二电阻的另一端与第一电阻的另一端电性连接,第一运算放大器的第一运放输出端与第三电阻的一端电性连接后作为放大电路输出端,第三电阻的另一端与第一运放第一输入端电性连接。

8、进一步地,积分电路包括:第二运算放大器、第四电阻、第一电容;

9、第二运算放大器的第二运放第一输入端与第四电阻的一端电性连接,第四电阻的另一端作为积分电路输入端,第二运算放大器的第二运放输出端与第一电容的一端电性连接后作为积分电路输出端,第一电容的另一端与第二运放第一输入端电性连接。

10、进一步地,乘法器模块包括:第一乘法器、第二乘法器;

11、第一乘法器的第一乘法器第一输入端作为第一乘法输入端,第一乘法器的第一乘法器第二输入端作为第二乘法输入端,第一乘法器的第一乘法器输出端与第二乘法器的第二乘法器第二输入端电性连接后作为第二乘法输出端,第二乘法器的第二乘法器第一输入端作为第三乘法输入端,第二乘法器的第二乘法器输出端作为第一乘法输出端。

12、进一步地,加法器模块包括:第三运算放大器、第五电阻、第六电阻、第七电阻、第八电阻、第九电阻;

13、第三运算放大器的第三运放第一输入端与第五电阻的一端电性连接,第五电阻的另一端作为第一加法输入端,第三运放第一输入端还与第六电阻的一端电性连接,第六电阻的另一端作为第二加法输入端,第三运放第一输入端还与第七电阻的一端电性连接,第七电阻的另一端与第八电阻的一端电性连接后接地,第八电阻的另一端与第三运算放大器的第三运放第二输入端电性连接,第三运算放大器的第三运放输出端与第九电阻的一端电性连接后作为加法输出端,第九电阻的另一端与第三运放第二输入端电性连接。

14、进一步地,加法器模块为同相加法器。

15、进一步地,开关模块包括:第一开关、第二开关、第三开关;

16、第一开关的一端作为第一开关输入端,第二开关的一端作为第二开关输入端,第三开关的一端作为第三开关输入端,第一开关的另一端与第二开关的另一端以及第三开关的另一端电性连接后作为开关输出端。

17、进一步地,第一开关为第一晶体管,第二开关为第二晶体管,第三开关为第三晶体管。

18、进一步地,等效电路为荷控忆阻器等效电路。

19、进一步地,等效电路的二次非线性忆阻值为:

20、

21、其中,m1(q)为等效电路的二次非线性忆阻值,r1为第一电阻的阻值,r2为第二电阻的阻值,r3为第三电阻的阻值,r4为第四电阻的阻值,q为电荷量。

22、进一步地,等效电路的二次项为0的三次非线性忆阻值为:

23、

24、其中,m2(q)为等效电路的二次项为0的三次非线性忆阻值。

25、进一步地,等效电路的二次项不为0的三次非线性忆阻值为:

26、

27、其中,m3(q)为等效电路的二次项不为0的三次非线性忆阻值。

28、第二方面,提供一种多输出忆阻器应用系统,包括:上述第一方面记载的多输出忆阻器等效电路、微控制器、fpga、辅助电路;

29、微控制器与fpga电性连接,fpga与辅助电路以及多输出忆阻器等效电路电性连接,辅助电路与多输出忆阻器等效电路电性连接。

30、进一步地,微控制器产生控制信号,控制信号用于控制fpga工作。

31、进一步地,fpga根据控制信号产生第一时序信号,并将第一时序信号传输至辅助电路;

32、fpga还根据控制信号产生第二时序信号,并将第二时序信号传输至多输出忆阻器等效电路的开关模块。

33、进一步地,辅助电路包括数模转换电路、电压转换电路、函数信号产生电路;

34、数模转换电路根据第一时序信号产生第一模拟电压信号,电压转换电路根据第一模拟电压信号产生电源电压,电源电压为多输出忆阻器等效电路中的第一运算放大器、第二运算放大器、第三运算放大器、第一乘法器以及第二乘法器供电;

35、数模转换电路根据第一时序信号还产生第二模拟电压信号,函数信号产生电路根据第二模拟电压信号产生多输出忆阻器等效电路的输入信号。

36、第三方面,提供一种多输出忆阻器控制方法,应用于上述第二方面记载的多输出忆阻器应用系统;其中,开关信号包括:第一开关信号、第二开关信号、第三开关信号;

37、第一晶体管第二极作为第一开关的一端,第一晶体管第三极作为第一开关的另一端,第一晶体管第一极接收第一开关信号;

38、第二晶体管第二极作为第二开关的一端,第二晶体管第三极作为第二开关的另一端,第二晶体管第一极接收第二开关信号;

39、第三晶体管第二极作为第三开关的一端,第三晶体管第三极作为第三开关的另一端,第三晶体管第一极接收第三开关信号;

40、方法包括:

41、识别多输出忆阻器应用系统的忆阻器适用精度;

42、响应于忆阻器适用精度适用于等效电路的二次非线性忆阻值,第一开关信号控制第一晶体管关断,第二开关信号控制第二晶体管关断,第三开关信号控制第三晶体管导通。

43、进一步地,方法还包括:

44、响应于忆阻器适用精度适用于等效电路的二次项为0的三次非线性忆阻值,第一开关信号控制第一晶体管导通,第二开关信号控制第二晶体管关断,第三开关信号控制第三晶体管关断。

45、进一步地,方法还包括:

46、响应于忆阻器适用精度适用于等效电路的二次项不为0的三次非线性忆阻值,第一开关信号控制第一晶体管关断,第二开关信号空难感知第二晶体管导通,第三开关信号控制第三晶体管关断。

47、本发明实施例提供的技术方案带来的有益效果是:

48、1. 通过实施本发明实施例提供的多输出忆阻器等效电路、应用系统及控制方法,可以减少乘法器器件的使用,节约电路面积;

49、2. 对应于忆阻器应用场景的需求,适配多输出忆阻器等效电路的忆阻值精度;

50、3. 通过对同一忆阻器等效电路的复用,实现多种忆阻值精度,提高等效电路的适用灵活性。

- 还没有人留言评论。精彩留言会获得点赞!