时域交织ADC高输入带宽匹配低时钟偏斜采样前端网络

本发明属于超宽带模数转换器,具体涉及一种时域交织adc高输入带宽匹配低时钟偏斜采样前端网络。

背景技术:

1、随着信息技术的高速发展,低至几hz,高至几十ghz的数据转换器可应用于生活中的各个场合。而云计算的出现,对高速,低功耗通信需求迅速增加.超宽带通信系统分为无线和有线两种。在目前的5g无线通信系统中为了降低系统复杂度,节约面积可以采用射频直采架构接收机来取代传统超外差接收机,而这就需要超宽带模数转换器(adc)。而基于pam-4的背板接收器和相干光纤接收器是下一代有线通信系统的有前途的技术。对于这两种技术,超过10gs/s的adc必不可少。

2、对一个单通道的adc进行时域交织是实现如此高速的有效方法。如图1所示的时域交织adc架构,将n个adc并行工作,即可实现n倍的采样速率。然而,时域交织adc依然面临着很多问题。随着交织通道的增多,不同通道之间的失配以及时钟的抖动和采样时钟的偏斜严重的降低整体adc的性能。通道之间的失配包括失调失配和增益失配以及采样带宽失配。失调失配和增益失配与输入信号频率无关,属于固定失配,很容易在数字域进行校准。但是时钟偏斜和采样带宽失配与输入信号频率有很大关系,很难进行校准。需要大规模的校准电路,增加了整体adc的设计难度。如何设计一个具有低抖动,低偏斜,高输入匹配的采样前端电路是亟待解决的问题。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种时域交织adc高输入带宽匹配低时钟偏斜采样前端网络。本发明要解决的技术问题通过以下技术方案实现:

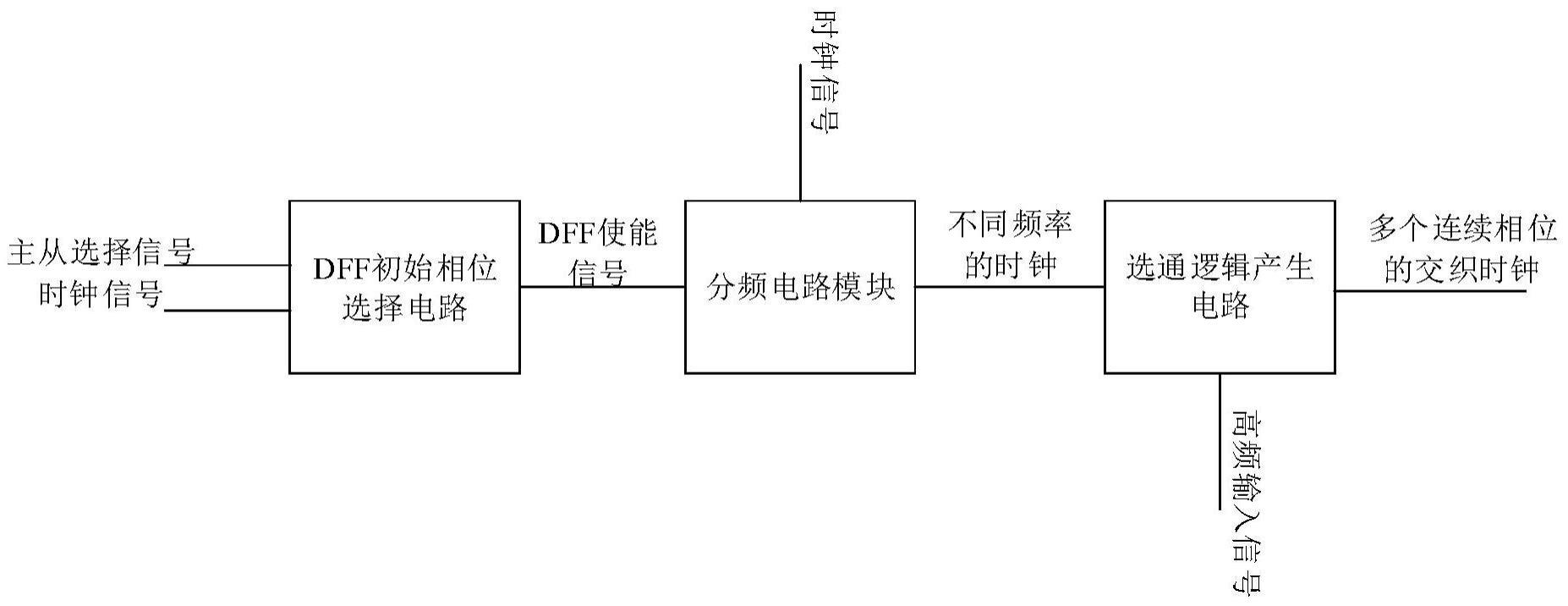

2、本发明提供了一种时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,包括:

3、dff初始相位选择电路,用于根据主从选择信号与时钟信号产生控制信号,根据所述控制信号控制dff使能信号的产生;

4、分频电路模块,用于根据所述dff使能信号,利用基于dff的分频电路实现所述时钟信号的分频,产生不同频率的时钟;

5、选通逻辑产生电路,用于对所述不同频率的时钟进行逻辑运算,产生不同相位的第一栅控时钟,通过高频输入信号对所述不同相位的第一栅控时钟进行边沿触发,得到不同相位的第二栅控时钟,根据所述不同相位的第二栅控时钟控制对应传输门导通传输所述高频输入信号,产生多个连续相位的交织时钟。

6、与现有技术相比,本发明的有益效果在于:

7、1.本发明的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,设置有dff初始相位选择电路,根据dff初始相位选择电路,利用设置的主从选择信号与时钟信号产生控制信号,通过该控制信号确保时域交织adc中奇偶通道对应的分频电路中的dff的初始态,有效避免了时域交织adc中奇数通道和偶数通道间顺序错乱的问题。

8、2.本发明的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,针对dff存在建立时间和信号传输延时引起的信号偏移导致出现包不住的现象,利用在选通逻辑产生电路中设置的边沿触发单元,产生新的栅控时钟,将高频输入信号包住并使其位于栅控时钟中间,减小了时钟偏斜和时钟抖动。

9、3.本发明的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,在网络布线时,通过层与层之间的打孔方式使得高频输入信号的两个传输路径的长度相等,从而使每个通道的采样带宽达到一致。

10、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

技术特征:

1.一种时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,包括:

2.根据权利要求1所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述dff初始相位选择电路,包括:控制信号产生单元和dff使能信号传输门单元,其中,

3.根据权利要求2所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,利用所述控制信号确保时域交织adc中奇偶通道对应的所述分频电路中的dff的初始态。

4.根据权利要求2所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述控制信号产生单元,包括:第一异或门(xor1)和第一反相器(inv1),其中,所述主从选择信号和所述时钟信号输入至所述第一异或门(xor1)产生第一控制差分信号(xor),第一控制差分信号(xor)通过所述反相器(inv1)得到第二控制差分信号(xorb),所述第一控制差分信号(xor)和所述第二控制差分信号(xorb)作为所述控制信号。

5.根据权利要求2所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述dff使能信号传输门单元,包括:第二反相器(inv2)、第三反相器(inv3)、第一cmos传输门(tg1)和nmos管,其中,

6.根据权利要求1所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述分频电路模块包括多级基于dff的分频电路,其中,

7.根据权利要求1所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述高频输入信号为一对差分高频信号,所述选通逻辑产生电路包括两个结构相同的相位时钟产生电路;

8.根据权利要求7所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述相位时钟产生电路包括多个并联的相位时钟产生单元,所述相位时钟产生单元包括:第二异或门(xor2)、边沿触发单元、第二cmos传输门(tg2)和pmos管,其中,

9.根据权利要求7所述的时域交织adc高输入带宽匹配低时钟偏斜采样前端网络,其特征在于,所述时域交织adc高输入带宽匹配低时钟偏斜采样前端网络在网络布线时,所述高频输入信号与所述时钟信号布线在不同金属层,所述高频输入信号布线在顶层金属层,通过对所述顶层金属层与设置在所述顶层金属层下方的过渡金属层进行打孔,实现所述高频输入信号的两个传输路径的长度相等。

技术总结

本发明涉及一种时域交织ADC高输入带宽匹配低时钟偏斜采样前端网络,包括:DFF初始相位选择电路,用于根据主从选择信号与时钟信号产生控制信号,根据控制信号控制DFF使能信号的产生;分频电路模块,用于根据DFF使能信号,利用基于DFF的分频电路实现时钟信号的分频,产生不同频率的时钟;选通逻辑产生电路,用于对不同频率的时钟进行逻辑运算,产生不同相位的第一栅控时钟,通过高频输入信号对不同相位的第一栅控时钟进行边沿触发,得到不同相位的第二栅控时钟,根据不同相位的第二栅控时钟控制对应传输门导通传输高频输入信号,产生多个连续相位的交织时钟。本发明避免了时域交织ADC中奇数通道和偶数通道间顺序错乱的问题,减小了时钟偏斜和时钟抖动。

技术研发人员:刘术彬,常军,梁鸿志,朱樟明

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!