一种实现毫米波频率拓展的电路的制作方法

本发明属于毫米波通信系统,具体地说,是涉及一种实现毫米波频率拓展的电路。

背景技术:

1、频率实现技术是各类雷达、收发信机、通信系统、电子对抗系统的核心技术,其工作频率、频率步进、跳频时间、相位噪声等指标直接决定了各类通信系统的性能;根据合成方法的不同,频率合成器主要可分为直接频率合成(ds)、锁相频率合成(pll)、直接数字频率合成(dds)三种,性能上各有优缺点,相互之间可以实现很好的补充。

2、直接频率合成的输出频率切换速度快,噪声低;但是电路结构复杂、体积大、成本高、调试困难等,并且直接频率合成技术采用了大量的频率变换器件,引入了很多非线性杂散,因此,难以实现良好的杂散指标。dds技术利用数字方式累加相位,再以相位和查询正弦函数表得到正弦波的离散数字序列,最后经d/a变换形成模拟正弦波。锁相频率合成器利用反馈原理,由于环路的作用,相位噪声、杂散水平都可以做的很好,适合于对频率切换速度不高而对相位噪声和杂散要求比较高的应用场合。dds频率合成技术具有超高的捷变速度(<0.1ns),超细的分辨率(可达1hz),以及相位的连续性,可以输出宽带的正交信号,容易实现线性调频和其它各种频率、相位、幅度调制,输出频率的稳定度及相位噪声等指标与系统时钟相当,全数字化便于单片集成。但dds也有其固有的不足之处,那就是输出频率带宽小和杂散指标不太高。近年来不少学者对抑制dds输出频谱中的杂散进行了研究,相继提出了抖动注入、rom存储压缩、平衡dac结构等杂散抑制的方法,使dds的输出杂散得到了一定程度的改善,但dds信号仍无法实现高频信号输出,尤其是在毫米技术领域,该方式很难直接应用。

3、近年来,随着雷达及各类通信系统的工作频率越来越高,越来越多的整机系统希望能够利用dds的快速调制的优点,通过dds产生频率低但覆盖各类信号样式的信号,然后通过各类频率变换的方式将该信号叠加到需要的输出频段中去,且要求输出信号的高信号质量,由于输入信号与输出信号在工作频率、频率步进、相位噪声、杂散等方面的性能有很大差别,因此对于频率拓展的方法提出了很大的挑战。

技术实现思路

1、本发明的目的在于提供一种实现毫米波频率拓展的电路,使获得的毫米波具有工作频率高、相位噪声低、杂散性能高的特点。

2、为实现上述目的,本发明采用的技术方案如下:

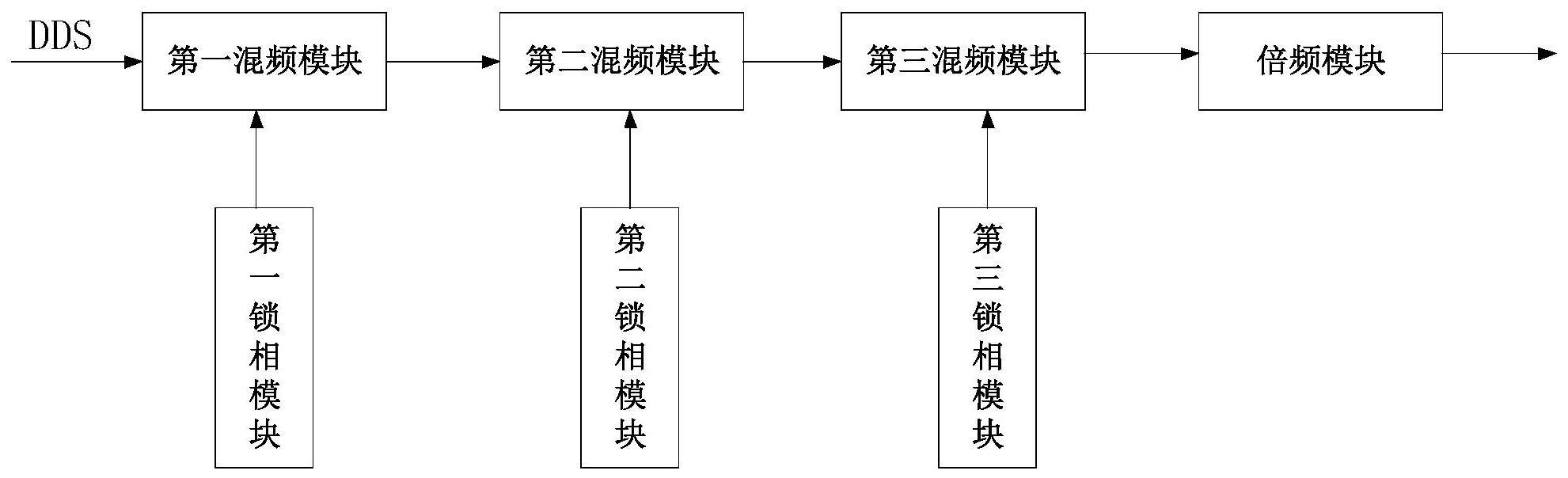

3、一种实现毫米波频率拓展的电路,包括用于产生低频本振信号的第一锁相模块,用于将输入的dds信号与第一锁相模块产生的低频本振信号进行混频的第一混频模块,用于产生l波段本振信号的第二锁相模块,用于将第一混频模块输出的混频信号与第二锁相模块产生的l波段本振信号进行混频的第二混频模块,用于产生ku波段本振信号的第三锁相模块,用于将第二混频模块输出的混频信号与第三锁相模块产生的ku波段本振信号进行混频的第三混频模块,以及用于将第三混频模块输出的信号的频率拓展到ka波段的倍频模块。

4、进一步地,在本发明中,所述第一锁相模块和第二锁相模块的电路拓扑结构相同,均包括第一锁相环和第一放大器,所述第一锁相环包括依次连接的第一鉴相器、第一环路滤波器和第一压控振荡器,其中,第一压控振荡器的反馈输出端还与第一鉴相器相连,第一压控振荡器的另一输出端与第一放大器相连;参考信号经内部分频后产生鉴相频率fpd,第一压控振荡器经分频后与参考信号产生的鉴相频率进行鉴相,鉴相后产生与两个信号相位差成正比的电压信号,该信号经第一环路滤波器进行环路滤波,实现电压信号的放大和低通滤波,产生高纯度电压信号,该电压进入第一压控振荡器的压控端控制第一压控振荡器产生相应的频率,该信号再进入鉴相器实现负反馈,重复进行分频、鉴相的过程,最终实现锁定,经锁定后参考信号与l波段本振信号有固定的相位差且实现相应的第一锁相模块的频谱搬移。

5、进一步地,在本发明中,所述第三锁相模块采用两个锁相环实现环内混频后经第三放大器输出,两个锁相环记为第二锁相环和第三锁相环,所述第二锁相环的电路拓扑结构与第一锁相模块、第二锁相模块中的第一锁相环相同,包括依次连接的第二鉴相器、第二环路滤波器和第二压控振荡器,其中,第二压控振荡器的反馈输出端还与第二鉴相器相连,第二压控振荡器的另一输出端与第三锁相环相连;所述第三锁相环包括依次连接的第三鉴相器、第三环路滤波器、第三压控振荡器及连接于第三鉴相器和第三压控振荡器之间的第一混频器;其中,第二锁相环中的第二压控振荡器的一个输出端与第一混频器相连;第三压控振荡器的输出端与第三放大器相连。。

6、进一步地,在本发明中,所述第一混频模块、第二混频模块、第三混频模块的电路拓扑结构相同,均包括依次连接的第二混频器、第一滤波器和第二放大器;

7、其中,第一混频模块中的第二混频器与第一锁相模块中的第一放大器相连,第一混频模块中的第二放大器与第二混频模块中的第二混频器相连;

8、第二混频模块中的第二混频器与第二锁相模块中的第一放大器相连,第二混频模块中的第二放大器与第三混频模块中的第二混频器相连;

9、第三混频模块中的第二混频器与第三锁相模块中的第一放大器相连,第三混频模块中的第二放大器与倍频模块相连。

10、进一步地,在本发明中,所述倍频模块由倍频器和第二滤波器组成;其中,所述倍频器的输入端与第三混频模块中的第二放大器的输出端相连,所述第二滤波器的输出端输出拓展后的毫米波。

11、与现有技术相比,本发明具有以下有益效果:

12、(1)本发明采用多级变频加逐级扩频的设计方法,完整的将dds信号的频率及相位信息搬移至毫米波频段,弥补了传统dds激励锁相环方式无法在dds信号中加入调制信号的缺点,将dds信号的应用范围从l波段扩展到ka波段,有效提升了雷达系统性能。

13、(2)本发明在传统的dds与锁相频率合成进行多次混频方案基础上进行方案优化,有效解决原有设计方案在频段拓宽时混频杂散难以抑制且滤波器尺寸大的缺点,在实现频率变换的同时,对工作带宽进行变换,降低每一级滤波器的设计难度,对滤波器带外抑制要求进行逐级分配,使得整体方案的带外抑制水平显著提升;通过本发明的实施,有效解决传统方式在外形尺寸和杂散指标上的缺点,可将原有的杂散技术指标由55dbc提升至65dbc,是对原有技术方案的跨越式提升。

14、(3)本发明针对现有频率实现方法应用于雷达系统的缺点,在原有设计方法的基础上,采用多级锁相环路同时跳频的设计方法,并在每一级锁相环路中加入助锁电路,使得原有锁相环的跳频时间由200us提升至5us,大大提升了整体系统的响应时间,使得系统的应用范围进一步提升。

15、(4)本发明针对雷达系统对于相位噪声技术指标要求高的特点,针对性的采用环内混频的设计方法,将传统锁相环的n分频比有效降低,极大提升了发射信号的相位噪声水平,可有效提升整个雷达系统对于目标分辨的水平。

16、(5)本发明采用微组装与印制板结合的微波毫米波混合集成电路的硬件设计方法,大大降低了传统快速小步进频率合成器的硬件尺寸,更加满足小型化的设计要求,更易于进行扩展和集成。

- 还没有人留言评论。精彩留言会获得点赞!