一种适用于NMOS开关的衬底偏置电路的制作方法

本发明涉及mos模拟开关,特别涉及一种适用于nmos开关的衬底偏置电路。

背景技术:

1、高性能的mos模拟开关广泛引用于零漂移放大器、模数转换和电源管理等单片模拟电路。在某些精密检测领域,mos开关自身的噪声电压占据了较高的比重,因此,需要采用有效的方法来降低mos开关的噪声。传统降低片上模拟mos开关噪声的方法是提高mos管的w/l以减小其导通电阻进而降低导通电阻带来的白噪声,但mos管较高的w/l会带来较大的开关毛刺;提高mos管栅源电压可以提高mos管的跨导进而降低噪声电压,但较高的栅源电压不仅带来较大的开关毛刺,降低系统的检测精度,而且通常需要额外的自举电路或电荷泵电路来提高栅压。

技术实现思路

1、本发明目的是:提供一种适用于nmos开关的衬底偏置电路,保证输出电压始终跟随输入电压,降低噪声电压,消除高频毛刺和干扰,保证nmos开关的衬底电压的精度,减小输入信号的负载效应。

2、本发明的技术方案是:

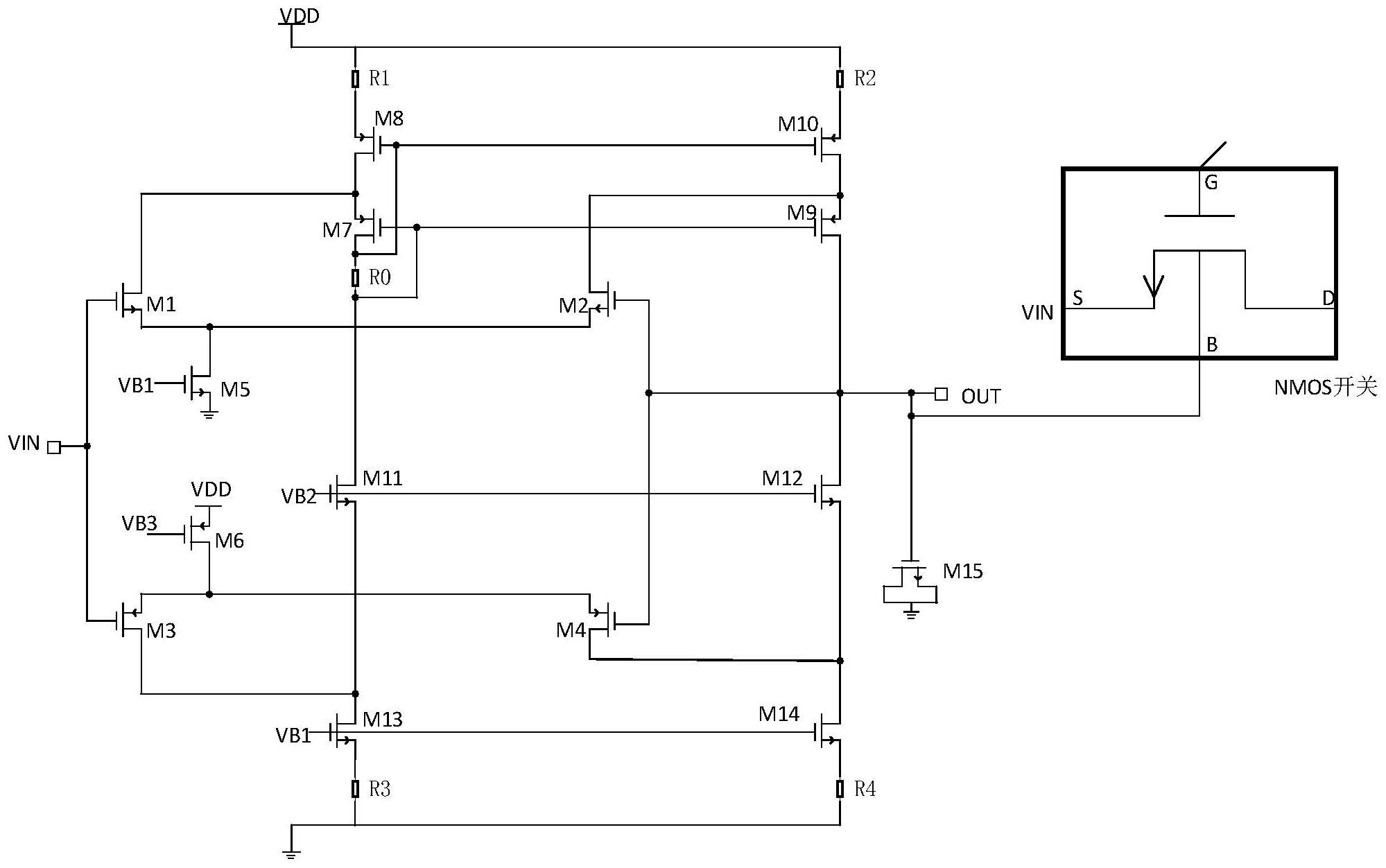

3、一种适用于nmos开关的衬底偏置电路,包括:

4、nmos管m1、m2组成的nmos输入差分对,及其尾电流源nmos管m5;

5、pmos管m3、m4组成的pmos输入差分对,及其尾电流源pmos管m6;

6、作为电流源的nmos管m13、m14,以及pmos管m8、m10;pmos管m8、m10共栅极连接,源极接电压vdd,漏极分别接nmos管m1、m2的漏极;nmos管m13、m14共栅极连接,源极接地,漏极分别接pmos管m3、m4的漏极;

7、输入电压vin,分别连接nmos管m1和pmos管m3的栅极;当vin输入高电压较高时,m1和m2导通;当vin输入电压较低时,m3和m4导通;当vin的电压处于中间值时,m1、m2、m3和m4同时导通;

8、输出结点out,分别接nmos管m2 和pmos管m4的栅极,向nmos开关提供衬底电压。

9、优选的,还包括共栅管m7、m9和m11、m12,以及电阻r0,其中m7、r0和m11依次串接在pmos管m8、nmos管m13的漏极之间,电阻r0的两端分别接m8、m7的栅极;m9和m12依次串接在pmos管m10、nmos管m14的漏极之间,m9和m12的中间结点连接输出结点out,增加输出结点out的阻抗。

10、优选的,还包括电阻r1、r2、r3和r4,分别与pmos管m8、m10和nmos管m13、m14的源极串联,提高环路增益。

11、优选的,还包括nmos管m15,nmos管m15的栅极接输出结点out,源极和漏极短接至地,作为频率补偿电容。

12、优选的,所述尾电流源nmos管m5的偏置电压为vb1;尾电流源pmos管m6的偏置电压为vb3。

13、优选的,所述nmos管m13、m14作为电流源,其偏置电压为vb1。

14、本发明的优点是:

15、本发明提出了一种适用于nmos开关的衬底偏置电路,电路采用电压负反馈结构,保证输出电压始终跟随输入电压,在整个输入电压范围内消除了nmos开关的体效应,提高了nmos开关的过驱动电压,降低了噪声电压;同时,衬底偏置电路的输出极点为主极点,通过在输出极点设置滤波补偿电容,消除了混入输入信号中的高频毛刺和干扰,保证nmos开关的衬底电压的精度。

技术特征:

1.一种适用于nmos开关的衬底偏置电路,其特征在于,包括:

2.根据权利要求1所述的适用于nmos开关的衬底偏置电路,其特征在于,还包括共栅管m7、m9和m11、m12,以及电阻r0,其中m7、r0和m11依次串接在pmos管m8、nmos管m13的漏极之间,电阻r0的两端分别接m8、m7的栅极;m9和m12依次串接在pmos管m10、nmos管m14的漏极之间,m9和m12的中间结点连接输出结点out,增加输出结点out的阻抗。

3.根据权利要求2所述的适用于nmos开关的衬底偏置电路,其特征在于,还包括电阻r1、r2、r3和r4,分别与pmos管m8、m10和nmos管m13、m14的源极串联,提高环路增益。

4.根据权利要求3所述的适用于nmos开关的衬底偏置电路,其特征在于,还包括nmos管m15,nmos管m15的栅极接输出结点out,源极和漏极短接至地,作为频率补偿电容。

5.根据权利要求1所述的适用于nmos开关的衬底偏置电路,其特征在于,所述尾电流源nmos管m5的偏置电压为vb1;尾电流源pmos管m6的偏置电压为vb3。

6.根据权利要求5所述的适用于nmos开关的衬底偏置电路,其特征在于,所述nmos管m13、m14作为电流源,其偏置电压为vb1。

技术总结

本发明公开了本发明提出了一种适用于NMOS开关的衬底偏置电路,电路采用电压负反馈结构,保证输出电压始终跟随输入电压,在整个输入电压范围内消除了NMOS开关的体效应,提高了NMOS开关的过驱动电压,降低了噪声电压,减小了输入信号的负载效应;同时,衬底偏置电路的输出极点为主极点,通过在输出极点设置滤波补偿电容,消除了混入输入信号中的高频毛刺和干扰,保证NMOS开关的衬底电压的精度。

技术研发人员:白涛,徐叔喜

受保护的技术使用者:中国兵器工业集团第二一四研究所苏州研发中心

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!