DAC电路的制作方法

本发明涉及数模转换集成电路,尤其是指一种dac电路。

背景技术:

1、dac是数字-模拟转换器(digital-to-analog converter)的缩写。dac是一种电子设备或电路,用于将数字信号转换为模拟信号。dac接受数字输入,通常是一个二进制数,然后根据输入值的大小,在其输出范围内生成相应的模拟电压或电流。

2、dac的性能可以通过多种指标来评估,其中“分辨率”被认为是关键性能指标。分辨率描述了dac可以表示的不同电平或数值的数量,并常用位数来表示,如8位、12位或16位。简单说,比特位数越高,dac的分辨率就越高,从而能够实现更精确和细致的数模转换效果。随着技术进步和高性能产品的普及,市场对高分辨率dac的需求持续上升。然而,这类dac的生产和研发成本相对较高,导致制造商必须提高其售价。因此,高分辨率dac的价格往往是低分辨率版本的数倍,这也成为制约其市场普及的一个重要因素。

3、因此,迫切需要提供一种低成本的dac电路以克服现有技术存在的问题。

技术实现思路

1、为此,本发明所要解决的技术问题在于克服现有技术中存在的技术缺陷,而提出一种dac电路,其使用两个低分辨率的数模转换器模拟一个高分辨率的数模转换器,能以低成本实现高分辨率的数模转换器,在降低硬件成本的同时还可以提高设备的性能,部分性能甚至优于高分辨率的数模转换器,易于推广使用。

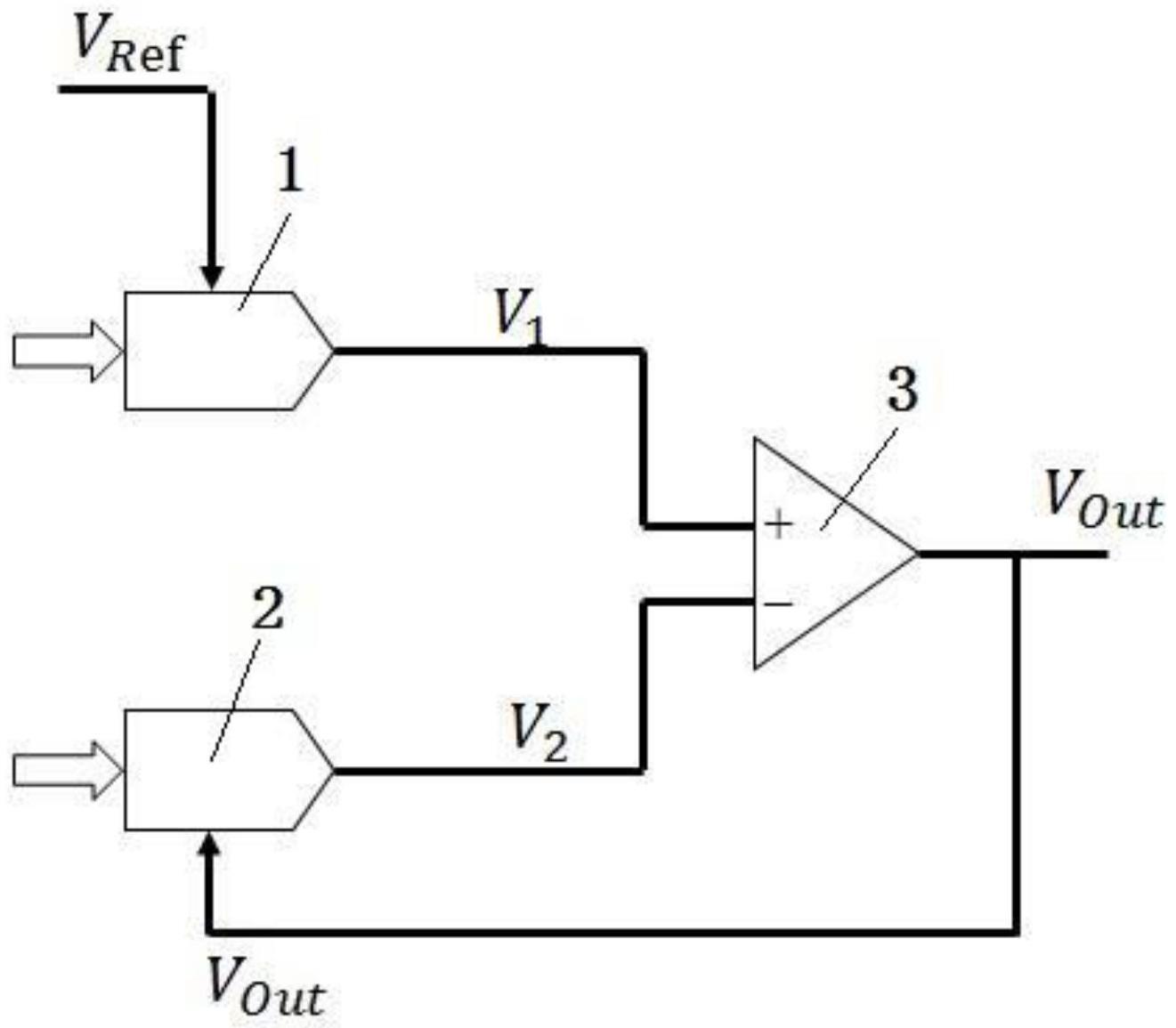

2、为解决上述技术问题,本发明提供了一种dac电路,包括:

3、第一数模转换器和第二数模转换器,其均具有输出端,其中,所述第一数模转换器外接预设的参考信号;

4、运算放大器,其具有输入端,所述运算放大器的正输入端连接所述第一数模转换器的输出端和所述运算放大器的负输入端连接所述第二数模转换器的输出端;

5、其中,所述运算放大器的输出信号反馈至所述第二数模转换器,通过设置所述第一数模转换器和第二数模转换器调节所述运算放大器的输出信号。

6、在本发明的一个实施例中,通过设置所述第一数模转换器的数码值和第二数模转换器的数码值调节所述运算放大器的输出信号。

7、在本发明的一个实施例中,当所述第一数模转换器的数码值发生改变时,所述运算放大器的输出信号发生改变,同时所述运算放大器的输出信号反馈至所述第二数模转换器,使所述第二数模转换器的输出信号发生改变,以对所述运算放大器形成反馈调节;当所述第二数模转换器的数码值发生改变时,会改变反馈回路的增益,也会导致所述运算放大器的输出信号发生改变。

8、在本发明的一个实施例中,在对所述运算放大器的输出信号进行调节时,根据预设的所述运算放大器的输出信号选择所述第一数模转换器的数码值和第二数模转换器的数码值的初始迭代解。

9、在本发明的一个实施例中,选择所述第一数模转换器的数码值和第二数模转换器的数码值的初始迭代解的方法,包括:

10、将预设的输出信号归一化为一正数vout,其中,正数vout介于0和1之间,n1表示第一数模转换器的位数和n2表示第二数模转换器的位数,两个数模转换器的位数可相同或不同;f表示第一数模转换器的数码值,r表示第二数模转换器的数码值;

11、判断vout小于1/2n1是否成立;

12、若是,则将第二数模转换器的数码值r设定为最大数码值2n2-1,设置第一数模转换器的数码值f为0或1,计算f分别取值为0或1时的误差e0和e1,比较e0和e1的绝对值大小,选择绝对值较小的误差e值所对应的f和r的值,得到f和r的初始迭代解;

13、若否,则设定一最小误差e,设定其初始值为1/2n1,遍历所有可能的f值,范围从1到[vout*2n1],对于每个f值,分别计算第二数模转换器的数码值r2和r3,以及误差e2和e3,并分别比较误差e2和e3与前述设定的最小误差e的绝对值大小,当误差e2或e3的绝对值小于设定的最小误差e的绝对值时,选择绝对值较小的误差更新最小误差e、f和r的值,并判断最小误差是否为0或已遍历完所有的f,若否,则继续遍历所有可能的f值,若是,则根据最小误差e值所对应的f和r的值,得到f和r的初始迭代解。

14、在本发明的一个实施例中,所述误差e0和e1的计算公式为:

15、e0=(f0/r)-vout,

16、e1=(f1/r)-vout,

17、其中,f表示第一数模转换器的数码值,f0表示f取值为0,f1表示f取值为1,e0表示f取值为0时的误差,e1表示f取值为1时的误差,r表示第二数模转换器的数码值,取值为2n2-1,vout表示运算放大器的输出信号的归一化值。

18、在本发明的一个实施例中,分别比较误差e2和e3与设定的最小误差的大小,当误差e2和e3小于设定的最小误差时,更新最小误差、f和r的值的方法,包括:

19、比较误差e2和当前的最小误差的绝对值大小,当误差e2小于当前的最小误差时,则将误差e2作为当前的最小误差,并更新f和r的值;以及比较误差e3和当前的最小误差的绝对值大小,当误差e3小于当前的最小误差时,则将误差e3作为当前的最小误差,并更新f和r的值。

20、在本发明的一个实施例中,所述第二数模转换器的数码值r2和r3,以及误差e2和e3的计算公式为:

21、r2=[f/vout],

22、r3=r2+1,

23、e2=(f/r2)*2n2-n1-vout

24、e3=(f/r3)*2n2-n1-vout

25、其中,f表示第一数模转换器的数码值,vout表示运算放大器的输出信号,[f/vout]表示对f/vout向下取整。

26、在本发明的一个实施例中,根据f和r的初始迭代解计算得到f和r的最优组合的方法,包括:

27、根据n1,n2,f,r的值,计算出公共缩放因子,将f和r的初始迭代解乘以公共缩放因子进行放大,得到f和r的最优组合。

28、在本发明的一个实施例中,所述缩放因子为a=[2^min(n1,n2)/max(f,r)],其中,n1表示第一数模转换器的位数和n2表示第二数模转换器的位数,f表示第一数模转换器的数码值,r表示第二数模转换器的数码值。

29、本发明的上述技术方案相比现有技术具有以下优点:

30、本发明所述的一种dac电路,其使用两个低分辨率的数模转换器模拟一个高分辨率的数模转换器,能以低成本实现高分辨率的数模转换器,在降低硬件成本的同时还可以提高设备的性能,部分性能甚至优于高分辨率的数模转换器,易于推广使用。

技术特征:

1.一种dac电路,其特征在于:包括:

2.根据权利要求1所述的一种dac电路,其特征在于:通过设置所述第一数模转换器的数码值和第二数模转换器的数码值调节所述运算放大器的输出信号。

3.根据权利要求2所述的一种dac电路,其特征在于:当所述第一数模转换器的数码值发生改变时,所述运算放大器的输出信号发生改变,同时所述运算放大器的输出信号反馈至所述第二数模转换器,使所述第二数模转换器的输出信号发生改变,以对所述运算放大器形成反馈调节;当所述第二数模转换器的数码值发生改变时,会改变反馈回路的增益,也会导致所述运算放大器的输出信号发生改变。

4.根据权利要求2或3所述的一种dac电路,其特征在于:在对所述运算放大器的输出信号进行调节时,根据预设的所述运算放大器的输出信号选择所述第一数模转换器的数码值和第二数模转换器的数码值的初始迭代解。

5.根据权利要求4所述的一种dac电路,其特征在于:选择所述第一数模转换器的数码值和第二数模转换器的数码值的初始迭代解的方法,包括:

6.根据权利要求5所述的一种dac电路,其特征在于:所述误差e0和e1的计算公式为:

7.根据权利要求5所述的一种dac电路,其特征在于:分别比较误差e2和e3与设定的最小误差的大小,当误差e2和e3小于设定的最小误差时,更新最小误差、f和r的值的方法,包括:

8.根据权利要求5所述的一种dac电路,其特征在于:所述第二数模转换器的数码值r2和r3,以及误差e2和e3的计算公式为:

9.根据权利要求5所述的一种dac电路,其特征在于:根据f和r的初始迭代解计算得到f和r的最优组合的方法,包括:

10.根据权利要求9所述的一种dac电路,其特征在于:所述缩放因子为a=[2^min(n1,n2)/max(f,r)],其中,n1表示第一数模转换器的位数,n2表示第二数模转换器的位数,f表示第一数模转换器的数码值,r表示第二数模转换器的数码值。

技术总结

本发明涉及一种DAC电路,包括第一数模转换器、第二数模转换器和运算放大器,第一数模转换器和第二数模转换器均具有输出端,第一数模转换器外接预设的参考信号;运算放大器具有输入端,运算放大器的输入端连接第一数模转换器的输出端和第二数模转换器的输出端;运算放大器的输出信号反馈至第二数模转换器,通过设置第一数模转换器和第二数模转换器调节运算放大器的输出信号。本发明使用两个低分辨率的数模转换器模拟一个高分辨率的数模转换器,能以低成本实现高分辨率的数模转换器,在降低硬件成本的同时还可以提高设备的性能,部分性能甚至优于高分辨率的数模转换器,易于推广使用。

技术研发人员:徐润生,曹石

受保护的技术使用者:胜达克半导体科技(上海)股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!