输入输出驱动器结构、输入输出控制方法及通信系统与流程

本发明涉及输入输出驱动器,具体涉及输入输出驱动器结构、输入输出控制方法及通信系统。

背景技术:

1、现场可编程门阵列(field programmable gate array,fpga)需要通过输入输出驱动器(io buf)与外部器件通信,输入输出驱动器用于将现场可编程门阵列内部的信号转换为外部器件可识别的信号以及用于将外部器件发出的信号转换为现场可编程门阵列可识别的信号。相关技术人员设计输入输出驱动器的过程中,往往需要考虑电压级别、信号速度、功耗等因素,为降低设计难度,相关技术中提供了多种输入输出驱动器架构,但每种输入输出驱动器架构往往只适用于特定场景,在场景更换的情况下,则必须使用另一种输入输出驱动器架构。由此带来的问题是,在外部器件更换或外部器件的通信参数更新等情况下,输入输出驱动器架构也要随之更换,这种情况不仅导致用户投入成本增加的问题,而且会延长项目交付时间。因此,常规输入输出驱动器架构存在使用场景受限的问题,亟需对常规输入输出驱动器架构进行改进或优化。

技术实现思路

1、有鉴于此,本发明提供了一种输入输出驱动器结构、输入输出控制方法及通信系统,以解决常规输入输出驱动器架构存在使用场景受限的问题。

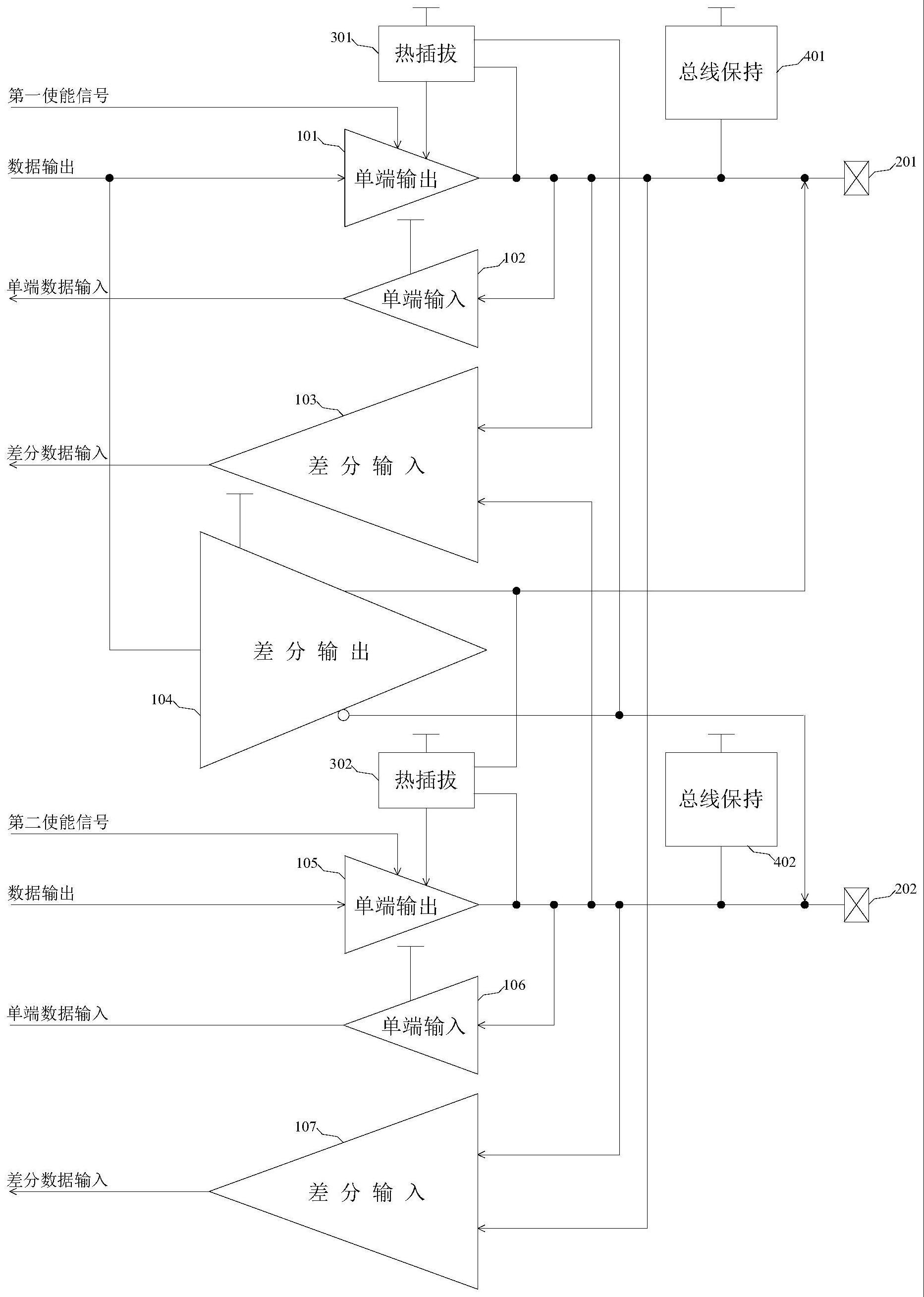

2、第一方面,本发明提供了一种输入输出驱动器结构,包括:

3、第一单端输出模块,与第一端子连接,第一单端输出模块用于将第一目标器件发出的第一单端信号输出至第一端子,第一端子用于与第二目标器件连接;

4、第一单端输入模块,与第一端子连接,第一单端输入模块用于将从第一端子输入的第二单端信号向第一目标器件发送,第二单端信号由第二目标器件发出;

5、第一差分输入模块,与第一端子、第二端子分别连接,第一差分输入模块用于将从第一端子输入的第一差分信号和从第二端子输入的第二差分信号进行差分解码,以及用于将通过差分解码得到的第三差分信号向第一目标器件发送,第一差分信号和第二差分信号均由第二目标器件发出,第二端子用于与第二目标器件连接;

6、第一差分输出模块,与第一端子、第二端子分别连接,第一差分输出模块用于对第四差分信号进行差分编码,得到通过第一端子输出的第五差分信号和通过第二端子输出的第六差分信号;

7、第二单端输出模块,与第二端子连接,第二单端输出模块用于将第一目标器件发出的第三单端信号输出至第二端子,第二端子用于与第二目标器件连接;

8、第二单端输入模块,与第二端子连接,第二单端输入模块用于将从第二端子输入的第四单端信号向第一目标器件发送,第四单端信号由第二目标器件发出;

9、第二差分输入模块,与第一端子、第二端子分别连接,第二差分输入模块用于将从第一端子输入的第七差分信号和从第二端子输入的第八差分信号进行差分解码,以及用于将通过差分解码得到的第九差分信号向第一目标器件发送,第七差分信号和第八差分信号均由第二目标器件发出。

10、相比于常规技术中的输入输出驱动器架构只能适用于特定场景的问题,本发明提供了一种全新的输入输出驱动器结构,能够支持基于第一单端输出模块和/或第二单端输出模块提供的单端输出工作模式、基于第一单端输入模块和/或第二单端输入模块提供的单端输入工作模式、基于第一差分输入模块和/或第二差分输入模块提供的差分输入工作模式以及基于第一差分输出模块提供的差分输出工作模式,从而本发明能够在不同的使用场景下使用对应的工作模块,在场景更换的情况下,无需更换输入输出驱动器结构,即避免了相关技术在场景更换的情况下必须要更换输入输出驱动器硬件的问题,从而明显降低用户投入成本,缩短了输入输出驱动器相关项目交付时间。

11、在一种可选的实施方式中,第一单端输出模块具有第一输入端和第一输出端,第一输入端用于接收第一单端信号,第一输出端用于输出通过第一单端输出模块处理后的第一单端信号,第一输出端与第一端子连接;

12、第一单端输入模块具有第二输入端和第二输出端,第二输入端用于接收第二单端信号,第二输入端与第一端子连接,第二输出端用于发出通过第一单端输入模块处理后的第二单端信号;

13、第一差分输入模块具有第三输入端、第四输入端以及第三输出端,第三输入端与第一端子连接,第四输入端与第二端子连接,第三输入端用于接收第一差分信号,第四输入端用于接收第二差分信号,第三输出端用于向第一目标器件发送第三差分信号。

14、本发明使用第一端子直接连接第一单端输出模块和第一单端输入模块,并使用第一端子和第二端子直接连接第一差分输入模块,可见本发明在使用较少数量的端子的情况下实现单端输出功能、单端输入功能及差分输入功能。

15、在一种可选的实施方式中,第一差分输出模块具有第五输入端、第四输出端以及第五输出端,第五输入端用于接收第四差分信号,第四输出端与第一端子连接,第五输出端与第二端子连接,第四输出端用于输出第五差分信号至第一端子,第五输出端用于输出第六差分信号至第二端子。

16、本发明使用第一端子和第二端子直接连接第一差分输出模块,可见本发明还能够在使用较少数量的端子的情况下实现了单端输出功能、单端输入功能、差分输入功能及差分输出功能。

17、在一种可选的实施方式中,第二单端输出模块具有第六输入端和第六输出端,第六输入端用于接收第三单端信号,第六输出端用于输出通过第二单端输出模块处理后的第三单端信号,第六输出端与第二端子连接;

18、第二单端输入模块具有第七输入端和第七输出端,第七输入端用于接收第四单端信号,第七输入端与第二端子连接,第七输出端用于发出通过第二单端输入模块处理后的第四单端信号;

19、第二差分输入模块具有第八输入端、第九输入端以及第八输出端,第八输入端与第一端子连接,第九输入端与第二端子连接,第八输入端用于接收第七差分信号,第九输入端用于接收第八差分信号,第八输出端用于向第一目标器件发送第九差分信号。

20、本发明使用第二端子直接连接第二单端输出模块和第二单端输入模块,并使用第二端子和第一端子直接连接第二差分输入模块,可见本发明还能够基于上述第一端子和第二端子分别与第一单端输出模块、第一单端输入模块、第一差分输入模块、第一差分输出模块、第二单端输出模块、第二单端输入模块、第二差分输入模块的具体连接方式和整体架构设计,本发明在兼顾了单端输出模式、单端输入模式、差分输出模式及差分输入模式的基础上,仍然只使用两个端子与外部器件连接,即只通过第一端子和第二端子作为第一目标设备与第二目标设备之间的物理连接端子,可见本发明相比于多种常规设计的简单叠加的方案来说,用于对外连接的端子数量更少,整体架构设计更合理。

21、在一种可选的实施方式中,输入输出驱动器结构,还包括:

22、第二差分输出模块,具有第十输入端、第九输出端以及第十输出端,第十输入端用于接收第十差分信号,第二差分输出模块用于对第十差分信号进行差分编码,得到第十一差分信号和第十二差分信号,第九输出端与第一端子连接,第十输出端与第二端子连接,第九输出端用于输出第十一差分信号至第一端子,第十输出端用于输出第十二差分信号至第二端子。

23、本发明还能够额外增加第二差分输出模块,该方式不仅能够实现第一差分输出模块与第二差分输出模块交替地进行工作的方式,而且还能够在第一差分输出模块故障时起到冗余等目的,保证差分输出性能,提高本发明产品可靠性。

24、在一种可选的实施方式中,第一单端输出模块还具有第一使能端,第一使能端用于接收由第一目标器件发出的第一使能信号,第一使能信号用于控制第一单端输出模块是否输出通过第一单端输出模块处理后的第一单端信号;

25、第二单端输出模块还具有第二使能端,第二使能端用于接收由第二目标器件发出的第二使能信号,第二使能信号用于控制第二单端输出模块是否输出通过第二单端输出模块处理后的第三单端信号。

26、本发明还能通过向第一使能端发送的第一使能信号控制第一单端输出模块的使能状态或者通过向第二使能端发送的第二使能信号控制第二单端输出模块的使能状态,从而实现对单端输出功能的有效控制。

27、在一种可选的实施方式中,第一差分输出模块为lvds输出驱动器。

28、通过lvds(low-voltage differential signaling,低电压差分信号)输出驱动器作为第一差分输出模块,本发明能够提高差分输出模式下数据传输速率、提高抗干扰能力、降低传输功耗以及实现长距离传输功能。

29、在一种可选的实施方式中,输入输出驱动器结构,还包括:

30、第一总线保持模块,与第一端子连接,第一总线保持模块用于在非驱动状态下保持第一端子的电平状态;

31、第二总线保持模块,与第二端子连接,第二总线保持模块用于在非驱动状态下保持第二端子的电平状态。

32、本发明通过第一总线保持模块能够在第一端子未连接或输入无效电压时保持第一端子上有效的电平状态,通过第二总线保持模块能够在第二端子未连接或输入无效电压时保持第二端子上有效的电平状态,提高本发明工作的可靠性。

33、在一种可选的实施方式中,输入输出驱动器结构,还包括:

34、第一热插拔模块,具有第一连接端、第二连接端以及第三连接端,第一连接端与第一单端输出模块连接,第二连接端与第一端子连接,第三连接端与第二端子连接;第一热插拔模块用于在热插拔操作时抵消或吸收外部输入信号,外部输入信号来自于第一端子和/或第二端子;

35、第二热插拔模块,具有第四连接端、第五连接端以及第六连接端,第四连接端与第二单端输出模块连接,第五连接端与第二端子连接,第六连接端与第一端子连接;第二热插拔模块用于在热插拔操作时抵消或吸收外部输入信号,外部输入信号来自于第一端子和/或第二端子。

36、本发明能够通过第一热插拔模块保护第一单端输出模块、第一端子及第二端子,并通过第二热插拔模块保护第二单端输出模块、第一端子及第二端子,从而对本发明输入输出驱动器结构内部的相关电子元件进行有效保护。

37、在一种可选的实施方式中,输入输出驱动器结构基于鳍式场效应晶体管工艺制造而成。

38、本发明提供的输入输出驱动器结构能够适于具有更低的晶体管工作电压的特点的鳍式场效应晶体管工艺,从而使得该输入输出驱动器结构在适用于多种使用场景的基础上兼顾小体积、低功耗、高频率、高速率和宽电压等特性。

39、在一种可选的实施方式中,输入输出驱动器结构集成于现场可编程门阵列上。

40、相比于现有技术,本发明能够提供包含一种具备单端输出工作模式、单端输入工作模式、差分输入工作模式、差分输出工作模式的io buf的fpga。

41、在一种可选的实施方式中,第一端子和第二端子均为焊垫。

42、本发明通过焊垫实现第一单端输出模块、第一单端输入模块、第一差分输入模块、第一差分输出模块、第二单端输出模块、第二单端输入模块、第二差分输入模块与第二目标器件的通信连接,提高了不同器件之间连接的可靠性。

43、在一种可选的实施方式中,第一目标器件为现场可编程门阵列上的ip核;

44、第二目标器件为外部器件。

45、本发明实现了现场可编程门阵列上的ip核与外部器件之间的通信,具体可实现ip核通过单端输出工作模式、单端输入工作模式、差分输入工作模式以及差分输出工作模式中的至少一种工作模式与外部器件之间进行通信。

46、第二方面,本发明提供了一种输入输出控制方法,该方法应用于上述第一方面或其对应的任一实施方式的输入输出驱动器结构,该方法包括:

47、在单端输出工作模式下,通过第一单端输出模块向第二目标器件输出第一单端信号,和/或,通过第二单端输出模块向第二目标器件输出第三单端信号;

48、在单端输入工作模式下,通过第一单端输入模块向第一目标器件输入第二单端信号,和/或,通过第二单端输入模块向第一目标器件输入第四单端信号,

49、在差分输入工作模式下,通过第一差分输入模块向第一目标器件输入对第一差分信号和第二差分信号进行差分解码得到的第三差分信号,和/或,通过第二差分输入模块向第一目标器件输入对第七差分信号和第八差分信号进行差分解码得到的第九差分信号;

50、在差分输出工作模式下,通过第一差分输出模块向第二目标器件输出通过对第四差分信号进行差分编码得到的第五差分信号和第六差分信号。

51、相比于已有输入输出控制方法,本发明的输入输出控制方法能够支持单端输出工作模式、单端输入工作模式、差分输入工作模式以及差分输出工作模式,从而本发明能够在不同的使用场景下使用对应的工作模式,在场景更换的情况下,无需更换输入输出驱动器结构,只需要在本发明的基础上进行功能切换,从而明显降低用户投入成本,缩短了输入输出驱动器相关项目交付时间。

52、第三方面,本发明提供了一种通信系统,该通信系统包括基于上述第一方面或其对应的任一实施方式的输入输出驱动器结构制造的输入输出驱动器;该通信系统还包括第一目标器件和第二目标器件:

53、第一目标器件,通过输入输出驱动器与第二目标器件之间进行通信;

54、第二目标器件,通过输入输出驱动器与第二目标器件之间进行通信。

55、本发明中的通信系统能够为第一目标器件与第二目标器件之间的通信过程提供可切换使用的单端输出工作模式、单端输入工作模式、差分输入工作模式以及差分输出工作模式,从而使得本发明的通信系统能够应用于更多的场景。

- 还没有人留言评论。精彩留言会获得点赞!