一种适用于OOK调制的低功耗压控振荡器的制作方法

本发明属于压控振荡器模拟电路的,具体涉及一种适用于ook调制的低功耗压控振荡器。

背景技术:

1、日益增长的高速通信和雷达系统市场需求极大地推动了收发机的研究和开发,作为核心器件的压控振荡器也得到了越来越多的关注。在零中频和低中频收发机中,本振信号和来自天线经低噪放放大后的接收信号进行混频产生有用信号,其频谱纯度对整个收发系统的灵敏度和动态范围有着直接的影响。由于数字电路,比如直接数字频率综合技术(dds)直接合成的数字频率信号杂散严重且带宽有限,不能满足通信系统的要求,因此在射频收发系统中,本振信号基本都是通过锁相环实现的。其中压控振荡器负责产生锁相环的输出信号,是本振信号的直接来源。如果将锁相环视为一个控制系统,那么压控振荡器就是这个系统的主要控制对象,其功耗和噪声性能对决定了整个锁相环乃至通信系统的性能上限。

2、在进行数字调制时,经常采用通断键控(ook)调制,ook调制时将输入的数字信号与压控振荡器产生的载波信号在混频器中进行混频。在信号为高电平的时候传输高频载波至后端,在低电平的时候输出低电平,ook调制的一个好处是可以将调制后的信号拆成两路差分信号,可以在接收端使用全差分输入全差分输出的放大器来抑制共模噪声定的架构优势。

3、振荡器将电路噪声转换为稳定的周期信号输出,实现一个“从无到有”的过程。压控振荡器的输出信号频率会跟随控制电压的变化而变化,进而覆盖期望的频带。集成电路系统中的压控振荡器主要分为电容电压压控振荡器和环形压控振荡器两大类。电容电压压控振荡器相位噪声性能较好,但片上电感 q 值较小,面积大,当振荡频率较低时,需要并联大容值电容,导致所占用的芯片面积进一步增加,使得整个电路版图面积大,不利于集成。如图1所示,环形振荡器是由环路中的许多增益级电路(延迟单元)级联而成,相同的延时单元级联可以构成一个环形振荡器。相比于电容电压压控振荡器,环形振荡器不需要电感元件,能够以较小的芯片面积实现集成化,调谐范围更大,可以产生多相振荡信号,从而得到了广泛的应用。

4、根据奈奎斯特采样定理,压控振荡器产生的载波信号频率需要大于数字信号频率的两倍。所以随着传输信号频率的增加,压控振荡器输出信号频率的增幅需要大于传输频率的两倍,为满足数字信号最高传输速率时的要求,压控振荡器必须工作在高振荡频率模式。对于环形振荡器而言,其振荡频率本质上与其每个结点的等效寄生电容的充放电速度相关,频率越高,要求充放电速度越快,振荡器消耗的功率越大。在进行低数据率数据传输时,同样采用高频压控振荡器会带来十分严重的功耗浪费,甚至影响系统的待机时间和热稳定性。

技术实现思路

1、本发明的目的在于提供一种适用于ook调制的低功耗压控振荡器,旨在解决上述的问题。本发明根据数字信号速率的不同,自适应调整压控振荡器的振荡频率,达到低功耗的目的。

2、本发明主要通过以下技术方案实现:

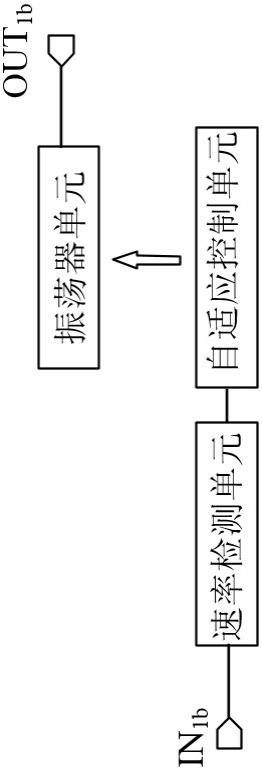

3、一种适用于ook调制的低功耗压控振荡器,包括从前至后依次连接的速率检测单元、自适应控制单元和振荡器单元,所述速率检测单元的输入端与信号输入端in连接,所述振荡器单元的输出端与信号输出端out连接;

4、所述速率检测单元用于对需要进行ook调制的数字信号进行检测,将输入的数字信号与参考电压的差值在误差放大器和输出电容上完成积分,实现当输入数字信号脉宽增加时,误差放大器的输出电压开始线性降低,当输入数字信号脉宽减小时,误差放大器的输出电压开始线性增加;所述自适应控制单元用于根据速率检测单元输出的电压控制信号,控制振荡器单元中可控电容阵列的切换,从而控制压控振荡器的振荡频率;所述振荡器单元包括若干个级联的反相器,且相邻反相器之间设置有可控电容阵列,所述反相器的两端分别设置有限流电阻,用于限制反相器开启关断时对节点电容充放电的电流大小。

5、为了更好地实现本发明,进一步地,所述速率检测单元包括误差放大器amp1d、pmos晶体管m1d和电容c1d;信号输入端in1d和基准电平输入端vref1d分别与误差放大器amp1d的反对向输入端、同向输入端连接;所述误差放大器amp1d的输出端分别与信号输出端out1d、电容c1d以及pmos晶体管m1d的漏极连接,所述电容c1d接地;所述pmos晶体管m1d的源极、栅极分别与电源vcc1d、信号输入端in1d连接。

6、为了更好地实现本发明,进一步地,所述自适应控制单元包括若干个并联设置的电压判决单元,所述电压判决单元包括电阻r1g、r2g、r3g、r4g、r5g、r6g、r7g、r8g、r9g、r10g,nmos晶体管m1g、m2g、m3g,电容c1g和二极管d1g;电源vcc1g分别与电阻r2g、r3g、r4g以及nmos晶体管m3g的漏极连接,信号输入端in1g通过电阻连r1g与nmos晶体管m1g的栅极接,所述nmos晶体管m1g的漏极、源极分别与电阻r2g、电阻r5g连接;所述nmos晶体管m2g的漏极分别与电阻r3g、电阻r7g连接,且源极与电阻r5g连接,且栅极分别与电阻r4g、电阻r6g连接;所述nmos晶体管m3g的栅极与电阻r7g连接,且源极分别与电阻r8g、电阻r9g连接,所述电阻r9g分别与电容c1g以及二极管d1g正极连接,所述二极管d1g负极分别与电阻r10g、信号输出端out1g连接,所述电阻r5g、电阻r6g、电阻r8g、电阻r10g、电容c1g分别接地。

7、为了更好地实现本发明,进一步地,所述振荡器单元包括从前至后依次连接的第一反相器、第二反相器、第三反相器、输出反相器和电阻r1c、r2c、r3c、r4c、r5c、r6c、r7c、r8c以及若干个可控电容阵列;电源vcc1c分别通过电阻r1c、r4c、r7c与第一反相器、第二反相器、第三反相器连接,所述第一反相器、第二反相器、第三反相器分别通过电阻r2c、r5c、r8c接地,所述第一反相器与第二反相器之间和第二反相器与第三反相器之间分别设置有电阻r3c与可控电容阵列和电阻r6c与可控电容阵列,所述第三反相器与第一反相器之间设置有可控电容阵列;所述输出反相器分别与电源vcc1c、接地端、信号输出端out1c连接。

8、为了更好地实现本发明,进一步地,所述第一反相器包括pmos晶体管m1c、m2c,所述第二反相器包括pmos晶体管m3c、m4c,所述第三反相器包括pmos晶体管m5c、m6c,所述输出反相器包括pmos晶体管m7c、m8c;所述pmos晶体管m1c、m2c的漏极与所述pmos晶体管m1c、m2c的栅极之间设置有可控电容阵列,所述pmos晶体管m1c、m2c的漏极之间设置有电阻r3c,所述pmos晶体管m1c、m2c的源极分别连接有电阻r1c、r2c;所述电阻r3c与pmos晶体管m3c、m4c的栅极之间设置有可控电容阵列,所述pmos晶体管m3c、m4c的源极分别连接有电阻r4c、r5c,所述pmos晶体管m3c、m4c的漏极之间设置有电阻r6c,电阻r6c与pmos晶体管m5c、m6c的栅极之间设置有可控电容阵列;所述pmos晶体管m5c、m6c的源极分别连接有电阻r7c、r8c。

9、为了更好地实现本发明,进一步地,所述可控电容阵列包括若干个并联支路,所述并联支路上串联设置有电容cf和射频开关swf;电源电源vcc1f分别与射频开关swf的一端连接,且射频开关swf的另一端与电容cf连接,所述电容cf的另一端与信号输出端out1f连接。

10、本发明的有益效果如下:

11、(1)本发明根据数字信号速率的不同,自适应调整压控振荡器的振荡频率,达到低功耗的目的。本发明与传统压控振荡器相比较,本发明提供的一种适用于ook调制的低功耗压控振荡器在同样的传输数据率下,电流损耗减小显著,具备更低的功耗特性。

12、(2)振荡器单元采用电流受限型延迟结构,在反相器结构基础上增加了两个限流电阻,限制反相器开启关断时对节点电容充放电的电流大小,从而抑制反相器结构在开启关断瞬时电流较大,功耗较大的缺点。在振荡器单元中,采用了三级反相器结构,且将pmos晶体管m7c和nmos晶体管m8c构成反相器用作输出级,提高了振荡器单元的输出能力。

13、(3)在实际工作中,在自适应控制单元中,nmos晶体管m1g、nmos晶体管m2g交替导通,流过电阻r5 g的尾电流大小都差不多,所以差分输入级电路相当于一个电流开关,nmos晶体管m1g、nmos晶体管m2g工作时只在截止和线性区之间转换,不进入饱和区,输入级开关速度很快。nmos晶体管m3g保持了差分输出信号相位以及逻辑关系不变,且将输出信号的电位下移一个vth,使前级输出电平和后级电路匹配。此外,nmos晶体管m3g作为源极跟随管,其输入阻抗较高、输出阻抗较低,也起到了前后级隔离缓冲和放大电流的作用,提高了电路的负载能力。

14、(4)在速率检测单元中,考虑到电路无法预判下一个信号的脉宽,pmos晶体管m1d用于实现输出电压的复位功能,保证振荡器在最高频率开始变化,当输入数字信号的最小脉宽出现时仍然能正确进行ook调制。

- 还没有人留言评论。精彩留言会获得点赞!