采样开关电路和电压采样电路的制作方法

本发明实施例涉及电子电路,尤其涉及一种采样开关电路和电压采样电路。

背景技术:

1、诸如电动汽车等用电设备中使用电池包来提供能量,电池包中可以包含多节串联的电芯(例如,锂离子电芯)。为了提高电池包的利用率、效率以及安全性,需要电池监控芯片来检测电池的电压、电流和/或温度信息。

2、在监测多个电芯的电压时,为了提高电压采样电路的采样精度,需要设置多个开关电路,能够对多个采样通道独立地进行开关。然而,开关电路会使采样通道的采样精度受到影响。

技术实现思路

1、有鉴于此,本发明实施例提供一种采样开关电路和电压采样电路,以至少部分解决上述问题。

2、根据本发明实施例的第一方面,提供了一种采样开关电路,包括:开关控制模块,包括:主开关支路,所述主开关支路的输入端连接到电芯采样节点,所述主开关支路的输出端连接到降压转换电路,所述主开关支路的输入端与输出端之间的第一偏置端跟随所述主开关支路的输入端的电压或输出端的电压变动,所述主开关支路在所述第一偏置端与控制端之间的第一驱动电压到达第一阈值时进入接通状态;辅开关支路,所述辅开关支路的输入端连接到所述电芯采样节点,所述主开关支路与所述辅开关支路通过所述控制端连接,在所述辅开关支路的输入端与输出端之间的第二偏置端与所述控制端之间的第二驱动电压到达第二阈值时所述辅开关支路进入接通状态,所述第二阈值不小于所述第一阈值;下拉控制模块,连接在所述第二偏置端与所述控制端之间,用于根据所述第一偏置端的电压下拉所述控制端的电压,生成所述第二驱动电压。

3、在本发明的另一实现方式中,所述主开关支路包括第一pmos管,所述辅开关支路包括第二pmos管,所述第一偏置端连接到所述第一pmos管的源极,所述第二偏置端连接到所述第二pmos管的源极,所述控制端连接在所述第一pmos管的栅极与所述第二pmos管的栅极之间。

4、在本发明的另一实现方式中,所述主开关支路还包括第三pmos管,所述辅开关支路包括第四pmos管,所述第一pmos管的源极连接到所述第三pmos管的源极,所述第二pmos管的源极连接到所述第四pmos管的源极,所述第一pmos管的漏极为所述主开关支路的输出端,所述第三pmos管的漏极为所述主开关支路的输入端,所述第二pmos管的漏极为所述辅开关支路的输出端,所述第四pmos管的漏极为所述辅开关支路的输入端,所述控制端连接在所述第三pmos管的栅极与所述第四pmos管的栅极之间。

5、在本发明的另一实现方式中,所述采样开关电路还包括钳位电路,所述钳位电路连接在所述第二偏置端与所述控制端之间。

6、在本发明的另一实现方式中,所述钳位电路包括第五pmos管,所述第五pmos管的源极连接到所述第二偏置端,所述第五pmos管的栅极与漏极连接到所述控制端。或者,所述钳位电路包括通过源极与漏极连接串联的多个第五pmos管,每个第五pmos管的栅极与漏极连接,首个第五pmos管的源极连接到所述第二偏置端,最末第五pmos管的栅极与漏极连接到所述控制端。

7、在本发明的另一实现方式中,所述开关控制模块还包括第六pmos管,所述第六pmos管的栅极与源极连接,所述第六pmos管的源极连接到所述第一pmos管的源极与所述第三pmos管的源极之间,所述第六pmos管的衬底连接到所述第二pmos管的源极与所述第四pmos管的源极之间,所述第六pmos管的漏极连接到所述控制端。

8、在本发明的另一实现方式中,所述采样开关电路还包括上拉电流源,所述上拉电流源的一端连接在所述第一pmos管的源极和所述第三pmos管的源极之间,所述上拉电流源的另一端连接到偏置高压侧。

9、在本发明的另一实现方式中,所述下拉控制模块包括第一nmos管和第一电阻,所述第一电阻连接在所述第二偏置端与所述第一nmos管的漏极之间,所述第一nmos管的漏极连接到所述控制端,所述第一nmos管的源极连接到偏置低压侧,所述第一nmos管的栅极接收第一下拉控制信号。

10、在本发明的另一实现方式中,所述下拉控制模块还包括第一下拉电流源,所述第一下拉电流源的一端连接到所述第一nmos管的源极,所述第一下拉电流源的另一端接地。

11、在本发明的另一实现方式中,所述采样开关电路还包括第二nmos管和第二下拉电流源,所述第二nmos管的源极连接到所述第二下拉电流源的一端,所述第二下拉电流源的另一端接地,所述第二nmos管的漏极连接到所述第一nmos管的源极,所述第二nmos管的栅极接收第二下拉控制信号。

12、在本发明的另一实现方式中,所述采样开关电路还包括上拉控制模块,连接在所述第二偏置端和所述控制端之间,用于在所述下拉控制模块执行控制之后,根据所述第二偏置端的电压对所述控制端的电压进行上拉。

13、在本发明的另一实现方式中,所述上拉控制模块包括第三下拉电流源、第三nmos管以及由第七pmos管和第八pmos管组成的电流镜,所述第七pmos管的栅极连接到所述第八pmos管的栅极,所述第七pmos管的源极和所述第八pmos管的源极连接到所述偏置电压端,所述第七pmos管的漏极连接到所述第三nmos管的漏极,所述第八pmos管的漏极连接到所述控制端,所述第三nmos管的源极连接到所述第三下拉电流源的一端,所述第三下拉电流源的另一端连接到偏置低压侧,所述第三nmos管的栅极接收第一上拉控制信号。

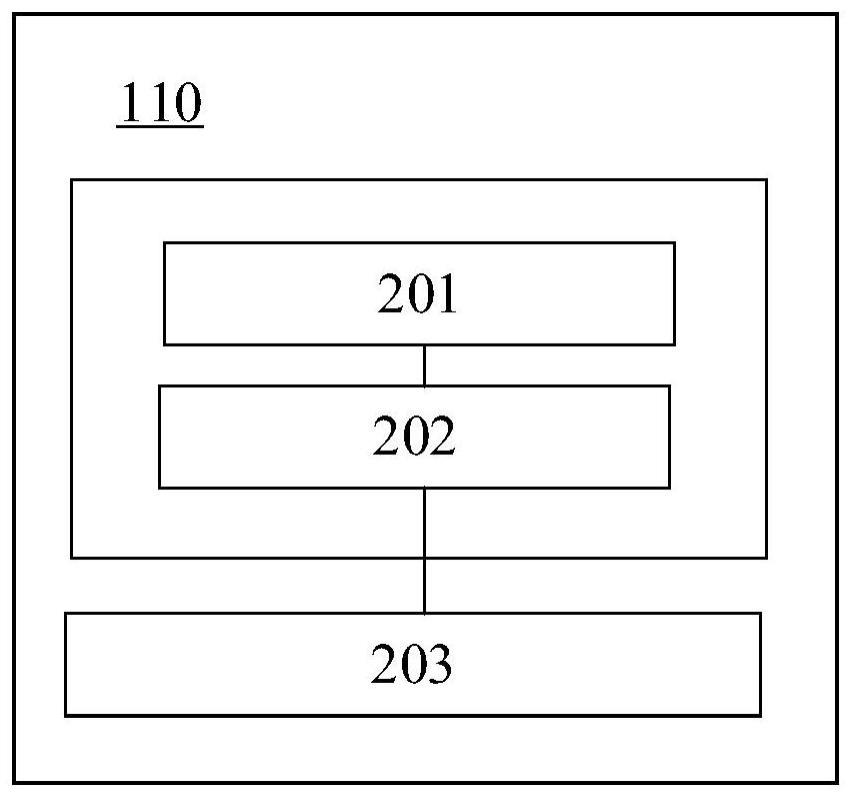

14、根据本发明实施例的第二方面,提供了一种电压采样电路,包括:根据第一方面所述的采样开关电路、降压转换电路以及模数转换电路。

15、在根据本发明实施例中,主开关支路的输入端与输出端之间的第一偏置端跟随主开关支路的输入端的电压或输出端的电压变动,主开关支路与辅开关支路通过控制端连接,因此,在第二驱动电压到达第二阈值时辅开关支路进入接通状态的情况下,第一驱动电压会到达第一阈值,从而主开关支路进入接通状态。也就是说,第二驱动电压随着第一驱动电压到达第一阈值而到达第二阈值。进一步地,下拉控制模块连接在第二偏置端与控制端之间,生成用于驱动辅开关支路的第二驱动电压,第二驱动电压到达第二阈值时产生的电流会经由辅开关支路流到下拉控制模块,而不会流过主开关支路,从而减小了主开关支路的静态功耗,提高了电压采样的精度。

技术特征:

1.一种采样开关电路,包括:

2.根据权利要求1所述的电路,其中,所述主开关支路包括第一pmos管,所述辅开关支路包括第二pmos管,所述第一偏置端连接到所述第一pmos管的源极,所述第二偏置端连接到所述第二pmos管的源极,所述控制端连接在所述第一pmos管的栅极与所述第二pmos管的栅极之间。

3.根据权利要求2所述的电路,其中,所述主开关支路还包括第三pmos管,所述辅开关支路包括第四pmos管,所述第一pmos管的源极连接到所述第三pmos管的源极,所述第二pmos管的源极连接到所述第四pmos管的源极,所述第一pmos管的漏极为所述主开关支路的输出端,所述第三pmos管的漏极为所述主开关支路的输入端,所述第二pmos管的漏极为所述辅开关支路的输出端,所述第四pmos管的漏极为所述辅开关支路的输入端,所述控制端连接在所述第三pmos管的栅极与所述第四pmos管的栅极之间。

4.根据权利要求3所述的电路,其中,所述采样开关电路还包括钳位电路,所述钳位电路连接在所述第二偏置端与所述控制端之间。

5.根据权利要求4所述的电路,其中,所述钳位电路包括第五pmos管,所述第五pmos管的源极连接到所述第二偏置端,所述第五pmos管的栅极与漏极连接到所述控制端;

6.根据权利要求3所述的电路,其中,所述开关控制模块还包括第六pmos管,所述第六pmos管的栅极与源极连接,所述第六pmos管的源极连接到所述第一pmos管的源极与所述第三pmos管的源极之间,所述第六pmos管的衬底连接到所述第二pmos管的源极与所述第四pmos管的源极之间,所述第六pmos管的漏极连接到所述控制端。

7.根据权利要求3所述的电路,其中,所述采样开关电路还包括上拉电流源,所述上拉电流源的一端连接在所述第一pmos管的源极和所述第三pmos管的源极之间,所述上拉电流源的另一端连接到偏置高压侧。

8.根据权利要求1所述的电路,其中,所述下拉控制模块包括第一nmos管和第一电阻,所述第一电阻连接在所述第二偏置端与所述第一nmos管的漏极之间,所述第一nmos管的漏极连接到所述控制端,所述第一nmos管的源极连接到偏置低压侧,所述第一nmos管的栅极接收第一下拉控制信号。

9.根据权利要求8所述的电路,其中,所述下拉控制模块还包括第一下拉电流源,所述第一下拉电流源的一端连接到所述第一nmos管的源极,所述第一下拉电流源的另一端接地。

10.根据权利要求8所述的电路,其中,所述采样开关电路还包括第二nmos管和第二下拉电流源,所述第二nmos管的源极连接到所述第二下拉电流源的一端,所述第二下拉电流源的另一端接地,所述第二nmos管的漏极连接到所述第一nmos管的源极,所述第二nmos管的栅极接收第二下拉控制信号。

11.根据权利要求1所述的电路,其中,所述采样开关电路还包括上拉控制模块,连接在所述第二偏置端和所述控制端之间,用于在所述下拉控制模块执行控制之后,根据所述第二偏置端的电压对所述控制端的电压进行上拉。

12.根据权利要求11所述的电路,其中,所述上拉控制模块包括第三下拉电流源、第三nmos管以及由第七pmos管和第八pmos管组成的电流镜,所述第七pmos管的栅极连接到所述第八pmos管的栅极,所述第七pmos管的源极和所述第八pmos管的源极连接到所述偏置电压端,所述第七pmos管的漏极连接到所述第三nmos管的漏极,所述第八pmos管的漏极连接到所述控制端,所述第三nmos管的源极连接到所述第三下拉电流源的一端,所述第三下拉电流源的另一端连接到偏置低压侧,所述第三nmos管的栅极接收第一上拉控制信号。

13.一种电压采样电路,包括:

技术总结

本发明实施例提供了一种采样开关电路和电压采样电路。采样开关电路包括开关控制模块和下拉控制模块。开关控制模块包括主开关支路和辅开关支路。主开关支路的输入端连接到电芯采样节点,输出端连接到降压转换电路,输入端与输出端之间的第一偏置端跟随输入端的电压或输出端的电压变动,并且在第一偏置端与控制端之间的第一驱动电压到达第一阈值时进入接通状态。辅开关支路的输入端连接到电芯采样节点,与辅开关支路通过控制端连接,并且在第二偏置端与控制端之间的第二驱动电压到达第二阈值时进入接通状态,第二阈值不小于第一阈值。下拉控制模块,连接在第二偏置端与控制端之间,用于根据第一偏置端的电压下拉控制端的电压,生成第二驱动电压。

技术研发人员:王铭,王红义,李一民

受保护的技术使用者:拓尔微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!