一种时序调整电路的制作方法

本发明属于数字电路,更具体地,涉及一种灵活的时序调整电路。

背景技术:

1、传统的时序调整方法较难解决以下情况:在电路速度要求较高的情况下,经常发生数据0与数据1的时序参数不一致的情况。这时速度常常要受较差时序的数据限制,例如对于fpga来说,通过调节idelay或odelay将信号延后或提前于事无补。

2、某电路模块b有一个时钟clk2,一个输入信号sig。高速输入信号sig的触发时钟以2ns为步长,输入信号sig由电路a传递给b:a的时钟clkl周期为2ns的整数倍。对于时钟clk2,输入信号sig的信号高电平要求setup time(建立时间)大于3.5ns,hold time(保持时间)大于0.2ns。

3、一般情况下tphl(high to low delay time,高电平到低电平延时)与tplh(low tohigh delay time,低电平到高电平延时)相差小于0.3ns时,取时钟周期为4ns即可。

4、但是随着工艺制造的偏差,电路a的tphl与tplh会存在差异。这种情况在工艺偏差时(snfp/fnsp)常常发生,根据工艺的不同,高温或低温还会加剧这种现象,尤其是信号奇数级传递时。snfp是指fast-nmos-slow-pmos,fnsp是指fast-nmos-slow-pmos。

5、假设tphl=0.2ns,tplh=1ns。此时,为了避免电路亚稳态,输入信号sig最小以6ns为周期变化,clk2最小周期为6ns,因此电路最高频率fmax=1/6ns,即fmax=166mhz,如图1所示。

6、现有技术中的解决方案包括以下方式:

7、1.设计时的mos尺寸调节:

8、针对工艺角可能的偏差,通过增大较差类型的管子宽长比(例如pmos)来减小高/低电平传输延时的差距。这种情况下会改善某个方向工艺角制造的产品性能,例如增大pmos宽长比来改善fnsp的表现,但是会恶化相反方向工艺角制造的产品性能,例如snfp。应用此种方法设计高速电路时,还是会牺牲一些因为工艺偏差大而不能使用的产品,而且对于电路设计人员经验的要求很高,需要对性能和芯片良率进行折衷。

9、2.片外驱动能力调节:

10、除了调整电路中管子的尺寸,还可以使用片外驱动补偿(ocd,off-chip driver)。这种补偿方法主要是针对信号斜率进行补偿,提高给负载充电的速度,在驱动大电容时甚为有效。但是当高/低电平信号的tr/tf差距很小时就很难再起到什么作用了,甚至会因为过快的信号上升/下降时间而引起信号完整性问题。tr是上升时间,指电压信号从vdd的10%升至90%的所需时间;tf是下降时间,指电压信号从vdd的90%降至10%的用时。

11、3.片内驱动能力调节:

12、当特别关注信号质量时,可以通过观察信号的眼图来调整内部电流饥饿型反相器的电流大小来控制某个方向的传播延时。或者说与pll类似用电流源,或者电荷泵加电容形成反馈环路来调节信号的传播延时。这种方法调节精度高,但是需要额外的电路结构,增加较多的静态或动态功耗,而且需要稳定的时间较长,成本较高。

13、针对这一情况,输入信号sig整体提前或延后都不能提高电路b的最高工作频率。传统的串联反相器链、加上rc-delay等延时调整方法在这种情况下失效了。

技术实现思路

1、为解决现有技术中存在的不足,本发明提供一种灵活的时序调整电路,根据需要调节的延时范围而增加动态功耗,占芯片面积很小且无静态电流。

2、本发明采用如下的技术方案。一种时序调整电路,用于将输入信号sig的高低电平宽度调整至设定值;所述时序调整电路包括:可编程延时路径、延时大小配置模块和延时方向配置模块,所述延时大小配置模块具有高电平延时寄存器和低电平延时寄存器;

3、可编程延时路径一端接入输入信号sig,另一端输出高低电平宽度调整至设定值的信号sig_to_b;可编程延时路径包括n级可编程延时单元,n≥2,每个可编程延时单元用于使输入信号延迟设定时长,通过控制投入到路径中的可编程延时单元数量,改变电路拓扑结构,用以编程可编程延时路径整体延时时间;

4、延时大小配置模块接受数字接口的配置,设置所述高电平延时寄存器的值和所述低电平延时寄存器的值;其中,所述高电平延时寄存器的值用于在信号sig_to_b为低电平时配置可编程延时路径投入可编程延时单元的数量,以实现l2h延时;所述低电平延时寄存器的值用于在信号sig_to_b为高电平时配置可编程延时路径投入可编程延时单元的数量,以实现h2l延时;

5、延时方向配置模块用于接受数字接口配置的延时模式,控制延时大小配置模块选择输出高电平延时寄存器或低电平延时寄存器的值输出。

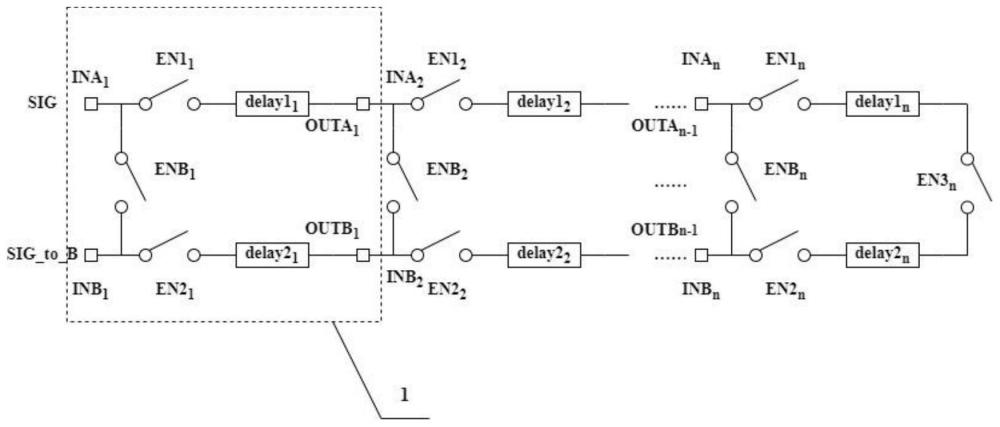

6、优选地,每个可编程延时单元采用相同的结构,对于第i个可编程延时单元,包括:输入端inai和inbi,输出端outai和outbi,开关enbi,延时单元delay1i和延时单元delay2i,开关en1i和开关en2i;

7、开关enbi设置在输入端inai与inbi之间;delay1i与开关en1i串联后,设置在输入端inai与输出端outai之间;delay2i与开关en2i串联后,设置在输入端inbi与输出端outbi之间,输出端outan与outbn之间设置有开关en3n;

8、i=1,2,…n-1时,开关en1i与开关en2i结构相同,受控于相同的信号eni;开关en1n、开关en2n与开关en3n结构相同,受控于相同的信号enn;

9、i=1,2,…n时,开关enbi受控于信号eni的反相信号。

10、优选地,每个可编程延时单元的延时单元delay1i和延时单元delay2i结构相同,采用一阶rc串联或反相器链串联实现。

11、优选地,通过配置r/c的大小、改变反相器的尺寸、等效扇出或串联个数来配置每个可编程延时单元的延时。

12、优选地,开关en1i、开关en2i和开关enbi为传输门。

13、优选地,延时大小配置模块2控制可编程延时单元使能信号的输入信号位为k位,k为正整数,控制2k级可编程延时单元,延时大小配置模块2使用k-2k译码器。

14、优选地,n的取值范围为,23≤n≤25,延时单元delay1i和延时单元delay2i均实现0.1ns的延迟。

15、优选地,延时方向配置模块包括:两个配置信号位d0和d1,用于配置延时模式;延时模式包括:

16、d0d1=00:h2l、l2h都延时;

17、d0d1=01:仅h2l延时;

18、d0d1=10:仅l2h延时;

19、d0d1=11:都不延时。

20、优选地,延时方向配置模块包括:方向检测位sd;

21、方向检测位sd用于检测可编程延时路径输出的信号sig_to_b的电平,方向检测位sd与配置信号位做组合逻辑运算,以信号sig_to_b当前的电平,控制下一位反相信号的延时。

22、优选地,延时方向配置模块包括:延时选择信号位;

23、延时选择信号位输出至延时大小配置模块,控制延时大小配置模块选择输出高电平延时寄存器或低电平延时寄存器的值。

24、与现有技术相比,本发明的有益效果至少包括:

25、(1)本发明提供的时序调整电路的模块是数字电路模块,根据需要调节的延时范围而增加动态功耗,占芯片面积很小且无静态电流。

26、(2)对于关心的传输路径,只要各传递一次高电平信号与一次低电平信号即可获得延时调整范围,不需要很长的调整时间,可以随时根据工作情况的变化而动态配置。

27、(3)本发明提供的时序调整电路的电路模块不仅可以实现l2h/h2l的延时单向调节,还可以双向分别配置成不同的延时。对于serdes应用情景还可以结合多相时钟或计数器,针对数据帧中的特定位拓展脉宽。对于周期性信号也可以起到调节占空比的作用。

- 还没有人留言评论。精彩留言会获得点赞!