半导体结构与半导体装置的制作方法

本揭示是关于一种半导体结构;具体而言是关于一种具有芯片堆叠结构的半导体结构。

背景技术:

1、虽然3d芯片堆叠技术使得电子装置能够在较小的面积和较低的功率下拥有更强大的计算能力,但是其制造工艺也比用于生产单一芯片的传统制造工艺更加复杂。举例来说,为了简化不同芯片之间的布线和连接,就可能需要将具有相同功能的芯片生产成不同的版本,进而为输入/输出接垫提供不同的排置。在这种情况下,具有相同功能但不同版本的芯片,仍需要以多组微影掩膜来制作,由于掩膜的价值不斐,因此这样的做法不仅会增加复杂性同时也会提高制造成本。此外,3d芯片堆叠技术中采用的硅通孔(through siliconvia;tsv)可能会干扰与模拟信号相关的电路的操作,例如输入/输出(i/o)电路和实体接口电路(例如phy),这也使得设计布局规划和堆叠芯片的排列更加困难。因此,如何提供一种能够简化制程并降低成本的堆叠芯片已成为亟待解决的问题。

技术实现思路

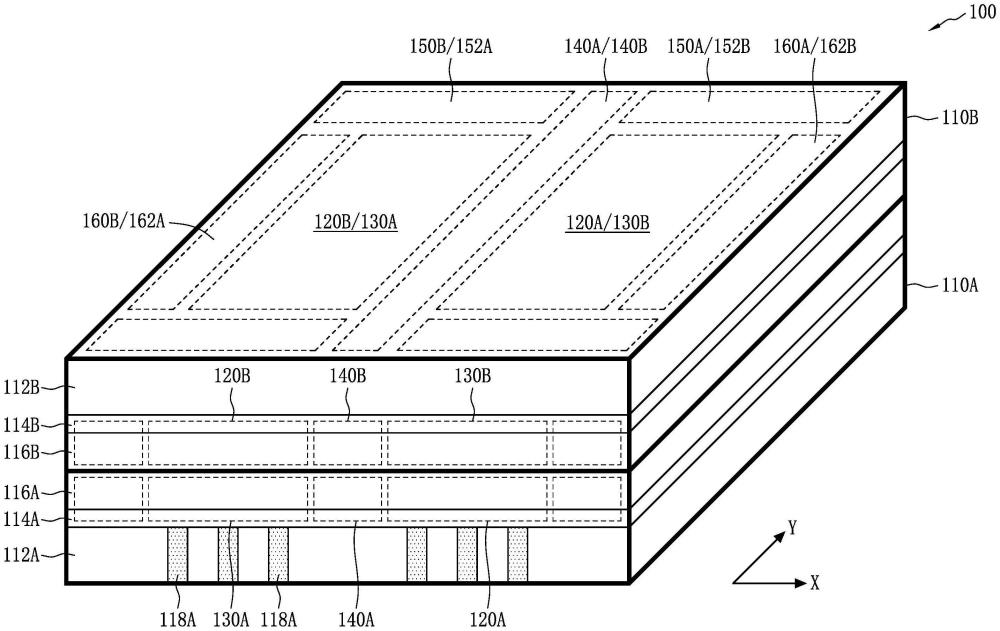

1、本发明的一实施例提供一种半导体结构,半导体结构包含第一芯片及第二芯片。该第一芯片包含第一基板、第一装置层、第一重布层(redistribution layer;rdl)及多个硅通孔(through silicon via;tsv)。该第一装置层设于该第一基板上。该第一rdl设于该第一装置层上,其中第一计算电路、第一内存电路以及第一堆叠内连接电路形成于该第一装置层与该第一rdl中。该多个tsv至少穿透该第一基板。该第二芯片包含第二基板、第二装置层及第二rdl。该第二芯片堆叠于该第一芯片上。该第二装置层设于该第二基板上。该第二rdl设于该第二装置层上,其中第二计算电路、第二内存电路、以及第二堆叠内连接电路形成于该第二装置层与该第二rdl中。在一俯视视角中,该第二堆叠内连接电路的多个接垫与该第一堆叠内连接电路的多个接垫对齐,且该第一计算电路透过该第一堆叠内连接电路与该第二堆叠内连接电路而耦接于该第二计算电路与该第二内存电路。该第一装置层与该第一rdl的结构与该第二装置层与该第二rdl的结构相同。

2、本发明的另一实施例提供一种半导体装置。该半导体装置包含至少一动态随机存取内存(dynamic random-access memory;dram)及第一半导体结构。该第一半导体结构包含第一芯片及第二芯片。该第一芯片包含第一基板、第一装置层、第一rdl及多个tsv。该第一装置层设于该第一基板上。该第一rdl设于该第一装置层上,其中第一计算电路、第一内存电路、及第一堆叠内连接电路形成于该第一装置层与该第一rdl中。该多个tsv至少贯穿该第一基板。该第二芯片堆叠于该第一芯片上,且该第二芯片包含第二基板、第二装置层及第二rdl。该第二装置层设于该第二基板上。该第二rdl设于该第二装置层上。其中第二计算电路、第二内存电路、及第二堆叠内连接电路形成于该第二装置层与该第二rdl中。该至少一dram耦接于该第一计算电路。在一俯视视角中,该第二堆叠内连接电路的接垫与该第一堆叠内连接电路的接垫对齐,且该第二计算电路透过该第一堆叠内连接电路与该第二堆叠内连接电路而耦接于该第一计算电路与该第一内存电路。该第一装置层与该第一rdl的结构与该第二装置层与该第二rdl的结构相同。

技术特征:

1.一种半导体结构,其特征在于,包含:

2.如权利要求1所述的半导体结构,其中在该俯视视角中:

3.如权利要求1所述的半导体结构,其中:

4.如权利要求3所述的半导体结构,其中在该俯视视角中:

5.如权利要求1所述的半导体结构,其中:

6.如权利要求5所述的半导体结构,其中在该俯视视角中:

7.如权利要求1所述的半导体结构,其中:

8.如权利要求7所述的半导体结构,其中:

9.如权利要求7所述的半导体结构,其中:

10.如权利要求1所述的半导体结构,其中:

11.如权利要求10所述的半导体结构,其中:

12.如权利要求11所述的半导体结构,其中在该俯视视角中:

13.如权利要求10所述的半导体结构,其中:

14.一种半导体装置,其特征在于,包含:

15.如权利要求14所述的半导体装置,还包含一中介层,其中:

16.如权利要求15所述的半导体装置,还包含:

17.如权利要求16所述的半导体装置,其中:

18.如权利要求16所述的半导体装置,其中在该俯视视角中:

19.如权利要求15所述的半导体装置,还包含:

20.如权利要求19所述的半导体装置,其中:

21.如权利要求19所述的半导体装置,其中:

22.如权利要求21所述的半导体装置,其中在该俯视视角中:

23.如权利要求21所述的半导体装置,其中在该俯视视角中:

24.如权利要求14所述的半导体装置,还包含一电路板,其中:

技术总结

本揭示揭露一种半导体结构。所述半导体结构有一顶部芯片与一底部芯片,且最大芯片大小受限于掩膜尺寸。每一芯片包含(1)核心:计算电路、(2)phy:连接至内存的模拟电路、(3)I/O:连接输出部分的模拟电路、(4)SERDES:序列高速模拟电路、(5)堆叠内连接电路、及(6)高速缓存。此种半导体结构可以采用小芯片设计,能够以最少的投片掩膜来实现高晶圆产量,进而降低成本。堆叠内连接电路以最短的距离(约数十微米)连接顶部芯片和底部芯片,进而提供高信号质量及功率效率。

技术研发人员:邱志威,张峻玮,陈尚斌,陈维志,黄哲彦

受保护的技术使用者:序星科技股份有限公司

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!