一种逐次逼近型模数转换器的制作方法

本技术涉及电路,尤其涉及一种逐次逼近型模数转换器。

背景技术:

1、逐次逼近型模数转换器(successive approximation registeranalogtodigital converter,sar adc)是一种模拟信号到数字信号的转换电路,采用连续逼近法实现模拟信号的采样和量化,采样速率)数ksps(每秒千次采样)至数百msps(每秒百万次采样)的中等至高分辨率应用结构。具有采样速度快,精度高,功耗低,但是复杂度较高的应用特点。sar adc应用广泛,在通信设备、医疗设备、音频处理、自动化控制和传感器技术等领域都有应用。

2、目前,在sar adc的每次量化过程中,sar adc在比较输入信号和dac输出电压时,会造成固定的能量损耗次数。且sar adc的高比特位电容电容值较大,在每次量化过程中都会进行充放电,因此会造成较大能量损耗。

技术实现思路

1、本技术实施例提供了一种逐次逼近型模数转换器,能够降低在模数转换过程中的能量损耗。

2、为解决上述技术问题,本技术实施例提供以下技术方案:

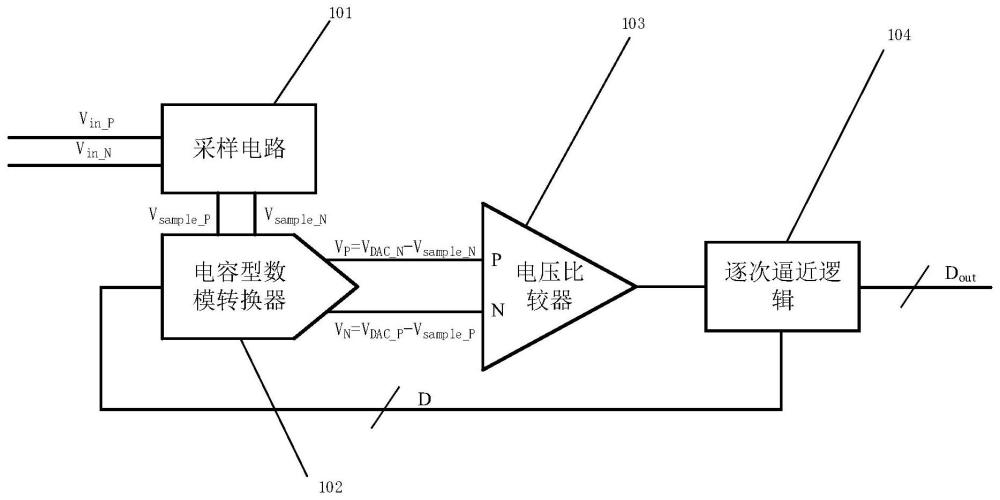

3、第一方面,本技术实施例提供一种逐次逼近型模数转换器,所述逐次逼近型模数转换器包括:采样电路、电容型数模转换器、电压比较器和逐次逼近逻辑电路;

4、其中,所述电压比较器的输入端连接所述电容型数模转换器的差分输出端,所述电压比较器的输出端连接所述逐次逼近逻辑电路,所述逐次逼近逻辑电路的输出端连接所述电容型数模转换器的输入端;

5、所述采样电路,用于将外部输入的第一模拟信号进行采样,以得到待量化模拟信号;并将所述待量化模拟信号保存至所述电容型数模转换器的电容阵列中;

6、所述逐次逼近逻辑电路,用于向所述电容型数模转换器输入数字控制码;

7、所述电容型数模转换器,用于将所述数字控制码转换为相应的第二模拟信号,并将所述数字控制码对应的第二模拟信号输入到所述电压比较器中;

8、所述电压比较器,用于比较所述数字控制码对应的第二模拟信号与所述待量化模拟信号的大小关系,以得到比较结果,向所述逐次逼近逻辑电路输出所述比较结果;

9、所述逐次逼近逻辑电路,用于根据所述电压比较器输出的比较结果,先从所述数字控制码的中位信号向高位信号进行高位部分逐次逼近,再从所述数字控制码的中位信号向低位信号进行低位部分逐次逼近,得到数字量化结果。

10、结合第一方面,在第一方面的第一种可能的实现方式中,所述逐次逼近逻辑电路,还包括:高位部分逐次逼近逻辑电路和低位部分逐次逼近逻辑电路;

11、所述高位部分逐次逼近逻辑电路的输出端和所述低位部分逐次逼近逻辑电路的输出端分别连接所述电容型数模转换器的输入端;

12、所述高位部分逐次逼近逻辑电路,用于根据所述电压比较器输出的比较结果,从所述数字控制码的中位信号向高位信号进行高位部分逐次逼近;

13、所述低位部分逐次逼近逻辑电路,用于根据所述电压比较器输出的比较结果,从所述数字控制码的中位信号向所述低位信号进行低位部分逐次逼近。

14、结合第一方面,在第一方面的第一种可能的实现方式中,所述逐次逼近逻辑电路,还包括:编码器、译码器和输出寄存器;

15、所述编码器的输入端连接所述输出寄存器,所述编码器的输出端连接所述高位部分逐次逼近逻辑电路;

16、所述译码器的输入端分别连接所述高位部分逐次逼近逻辑电路和所述低位部分逐次逼近逻辑电路,所述译码器的输出端连接所述输出寄存器;

17、所述编码器,用于将上一次的高位部分量化结果进行重编码,以得到上一次的高位部分量化重编码值,向所述电容型数模转换器输入所述上一次的高位部分量化重编码值;

18、所述译码器,用于对所述电容型数模转换器的控制码进行译码,以得到二进制译码结果;将所述二进制译码结果发送至所述输出寄存器;

19、所述输出寄存器,用于存储所述二进制译码结果的最终值;所述输出寄存器的输出结果为所述逐次逼近型模数转换器输出的数字控制码;所述输出寄存器的输出端连接所述编码器的输入端。

20、结合第一方面,在第一方面的第一种可能的实现方式中,所述高位部分逐次逼近逻辑电路包括:时钟顺序生成电路、比较结果寄存器、锁存器和数据选择器;

21、所述时钟顺序生成电路的输入端连接所述锁存器的输出端,所述时钟生成电路的输出端连接所述锁存器的输入端;

22、所述比较结果寄存器的时钟输入端连接所述锁存器的输出端,所述比较结果寄存器的输出端连接所述数据选择器的数据输入端;所述比较结果寄存器的数据输入端连接所述电压比较器的输出端;

23、所述时钟顺序生成电路和所述锁存器,用于产生输入到所述结果比较寄存器的时钟信号;

24、所述时钟顺序生成电路,用于控制多位时钟信号的变化顺序;

25、所述锁存器,用于暂存所述时钟信号的电平状态;

26、所述数据选择器,用于从所述上一次的高位部分量化重编码值和所述比较结果寄存器中选择出一组数据,得到数据选择结果。

27、结合第一方面,在第一方面的第一种可能的实现方式中,所述高位部分逐次逼近逻辑电路,具体用于:

28、在所述采样电路对所述第一模拟信号的采样结束之后,将所述电容型数模转换器的数字控制码恢复至三态数模转换控制码的中间态,存储所述电压比较器输出的比较结果;

29、若所述电压比较器第一次的比较结果与所述上一次的高位部分量化重编码值的最高位相同,将所述上一次的高位部分量化重编码值赋值给所述三态数模转换控制码;待所述赋值过程完成后,再次储存所述电压比较器输出的比较结果,所述电压比较器输出的第二次的比较结果作为所述输出寄存器的第一状态值;

30、从所述中位信号开始向高位方向逐位将所述三态数模转换控制码的各比特位赋值为所述输出寄存器的第一状态值,直至所述电压比较器输出的比较结果与所述输出寄存器的第一状态值不相等;

31、待所述电压比较器输出的比较结果与所述输出寄存器的第一状态值不相等后,向低位方向逐位将所述三态数模转换控制码的各比特位赋值为第二状态值,所述第二状态值通过对所述第一状态值取反得到;

32、在所述电压比较器完成比较后,将前一次改变的比特位赋值为所述电压比较器的当前次的比较结果,直至实现对所述中位信号的赋值。

33、结合第一方面,在第一方面的第一种可能的实现方式中,所述低位部分逐次逼近逻辑电路,具体用于:

34、待所述高位部分逐次逼近逻辑电路执行的所述高位部分逐次逼近完成后,从所述中位信号的低一位开始,逐位将所述三态数模转换控制码的各比特位赋值为所述电压比较器的当前次的比较结果,直至最低位赋值完成。

35、结合第一方面,在第一方面的第一种可能的实现方式中,所述电容型数模转换器的数字控制码包括n个的控制码和1个的冗余位,其中,所述n为所述逐次逼近型模数转换器的分辨率。

36、结合第一方面,在第一方面的第一种可能的实现方式中,所述比较结果寄存器,包括:第一寄存器和第二寄存器;

37、所述第一寄存器的时钟输入端连接所述锁存器的输出端,所述第一寄存器的输出端连接所述数据选择器的数据输入端;所述第一寄存器的数据输入端连接所述电压比较器的输出端;

38、所述第二寄存器的时钟输入端连接所述锁存器的输出端,所述第二寄存器的输出端连接所述数据选择器的数据输入端;所述第二寄存器的数据输入端连接所述电压比较器的输出端。

39、结合第一方面,在第一方面的第一种可能的实现方式中,所述电容型数模转换器的输出电压小于预设的参考电压。

40、结合第一方面,在第一方面的第一种可能的实现方式中,所述逐次逼近逻辑电路,用于高位部分逐次逼近结束之后,从所述数字控制码的中位信号向低位信号进行低位部分逐次逼近。

41、从以上技术方案可以看出,本技术实施例具有以下优点:

42、在本技术实施例中,由于逐次逼近逻辑电路是根据电压比较器输出的比较结果,先从数字控制码的中位信号向高位信号进行高位部分逐次逼近,再从数字控制码的中位信号向低位信号进行低位部分逐次逼近,来得到数字量化结果,所以可以减少单次量化过程中的电压比较器工作次数,并避免高比特位电容在每次量化过程中都需要进行充放电,从而可以有效降低能量损耗。

- 还没有人留言评论。精彩留言会获得点赞!