逐次逼近型模数转换器及其电容阵列的校准方法和介质与流程

本公开涉及信号处理,尤其涉及一种逐次逼近型模数转换器及其电容阵列的校准方法和介质。

背景技术:

1、模数转换器(analog-to-digital converter,adc)是几乎每个复杂集成电路的基本组成部分。特别是近年来,无线通信的迅猛发展,也为adc在其中的应用提供了非凡的机遇。其中,第五代移动通信(5g)要求应用在5g基站中的adc精度不低于12bit。5g应用中更快的数据传输率,更高的数据传输质量对于adc的转换速度和精度提出了更高的要求。同时,无线通信主要应用在便携式手持终端上,为了增加终端设备的待机时间,通常要求电池续航尽可能长,这也给adc的低功耗技术提出了更高的要求。

2、为了满足更加广泛的应用场景和日益增长的性能要求,不同结构的adc应运而生,其中典型的结构包括快闪型(flash)adc、流水线型(pipeline)adc、逐次逼近型(successive approximation register,sar)adc、σ-δ型adc。对于现阶段这些主流adc结构而言,速度、精度、功耗三种特性相互影响又相互制约。其中,sar adc的结构相对于其他结构的adc具有低功耗、结构简单、无源化的特点,一直是低功耗应用场景中的首选。saradc具有天然的低功耗优势,是因为其采用的是数字电路和模拟电路相结合的实现方式,模拟部分不需要精确的有源放大器,从而减少了直流功耗。其主要功耗来自于开关电容充放电带来的动态功耗,配合精心设计的开关切换方式可进一步降低整体的功耗。同时,saradc兼具提升速度和精度的优势,从而在众多adc结构中脱颖而出。

3、在高精度sar adc中,高精度的dac(digital-to-analog convertor,数模转换器)是其重要组成部分,其常常由二进制电容阵列组成,通过不同电容的翻转实现不同的输出电压。但由于工艺的原因使得单个电容的实际电容值偏离理想值,不同电容之间的不匹配将造成输出的线性度恶化,直接限制了整体高精度sar adc的精度性能。适当放大电容的尺寸可以改善电容的匹配程度,但是又会降低adc整体的转换速度,提高功耗。所以,针对saradc中电容失配的校准技术相继出现。

4、现有的大多数自校准技术属于前台校准方法,辅助电路通过校准电容电路连接到dac的输出端。在adc正常工作之前进行失配误差检测,校准逻辑控制辅助dac和比较器来量化电容失配造成的误差电压并送入校准存储器。在校准阶段,存储的误差信息通过辅助dac恢复成模拟电压量叠加在主dac的输出上,从而得到校准后准确的输出。但是,校准dac需要占用大量芯片面积,同时开关和逻辑电路消耗了额外的功耗,其失配检测的准确度受到adc自身精度的制约。如果adc自身的分辨率不够,可能会导致量化误差更加严重。

技术实现思路

1、为克服相关技术中存在的问题,本公开提供一种逐次逼近型模数转换器及其电容阵列的校准方法和介质。

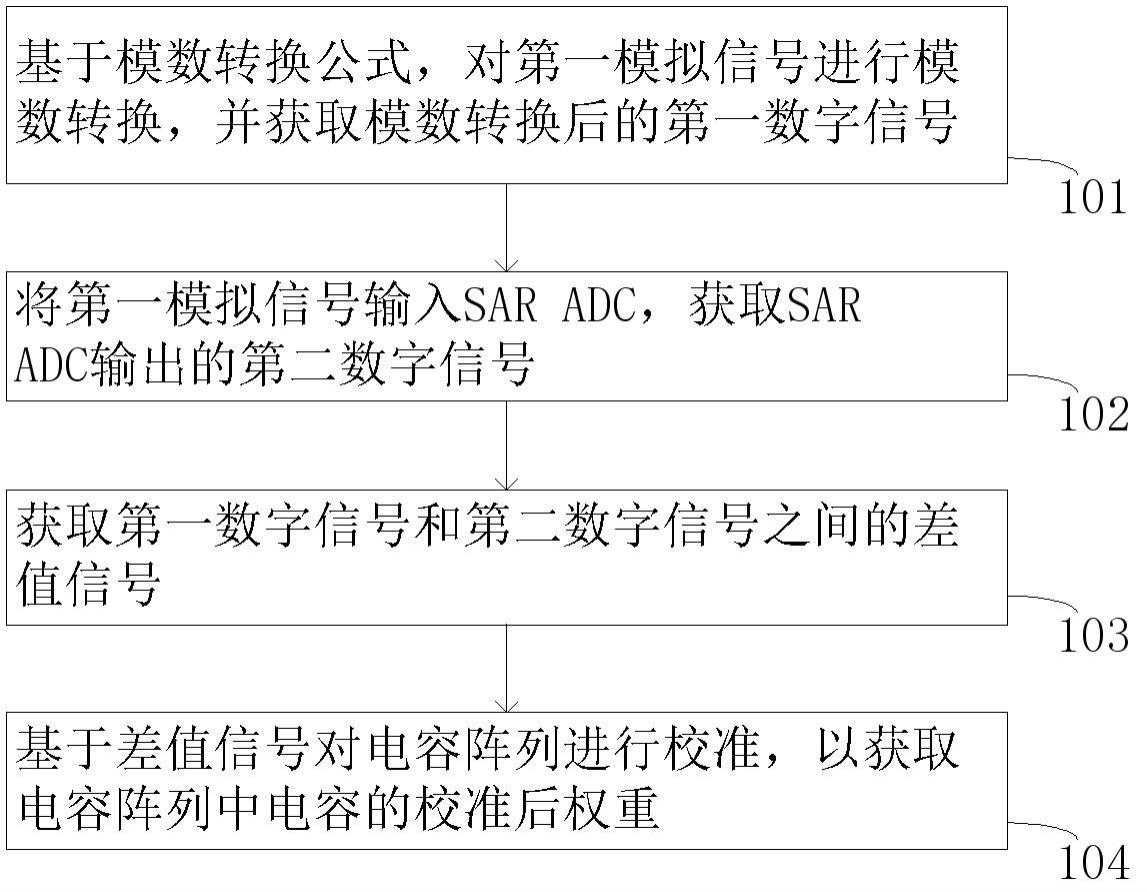

2、根据本公开的第一方面,提供了一种逐次逼近型模数转换器中电容阵列的校准方法,所述方法包括:

3、基于模数转换公式,对第一模拟信号进行模数转换,并获取所述模数转换后的第一数字信号;

4、将所述第一模拟信号输入所述逐次逼近型模数转换器,获取所述逐次逼近型模数转换器输出的第二数字信号;

5、获取所述第一数字信号和所述第二数字信号之间的差值信号;

6、基于所述差值信号对所述电容阵列进行校准,以获取所述电容阵列中电容的校准后权重。

7、其中,所述基于所述差值信号对所述电容阵列进行校准,以获取所述电容阵列中电容的校准后权重,包括:

8、获取所述电容阵列中电容的理想权重和待校准权重;

9、基于所述理想权重、待校准权重和所述差值信号,对所述电容阵列进行校准,以获取所述电容阵列中电容的校准后权重。

10、其中,所述基于所述理想权重、待校准权重和所述差值信号,对所述电容阵列进行校准,以获取所述电容阵列中电容的校准后权重,包括:

11、基于所述理想权重、待校准权重和所述差值信号,获取权重误差参数;

12、基于迭代算法,对所述待校准权重进行迭代计算,直至所述权重误差参数小于设定阈值;

13、将最后一次迭代计算输出的所述待校准权重作为所述校准后权重。

14、其中,所述获取权重误差参数,包括:

15、基于下述方式获取权重误差:

16、权重误差=,其中,n表示所述电容阵列中所述电容的个数,i表示对应的位数,表示第i位对应的所述电容的所述待校准权重,表示第i位对应的所述电容的所述理想权重,表示第一数字信号所述第i位上的值,delta表示所述差值信号;

17、通过计算所述权重误差的均方根,获取所述权重误差参数。

18、其中,所述通过计算所述权重误差的均方根,获取所述权重误差参数,包括:

19、基于下述方式获取权重误差参数:

20、权重误差参数=,其中,minrms()表示求均方根,m表示所述逐次逼近型模数转换器输出波形的一个周期波形所包括的采样点数,表示m个采样点中第j个采样点所对应的所述差值信号,和分别表示所述第j个采样点第i位所对应的所述待校准权重和所述理想权重,表示所述第j个采样点所对应的第一数字信号所述第i位上的值;

21、其中,对于所述m个采样点中的所有采样点,采用相同的和进行迭代计算。

22、其中,所述基于迭代算法,对所述待校准权重进行迭代计算,包括:

23、第一次迭代计算中,设置所述待校准权重的初始值为所述理想权重。

24、其中,所述基于迭代算法,对所述待校准权重进行迭代计算,包括:

25、将每次迭代计算输出的所述待校准权重作为下次迭代计算采用的待校准权重的初始值。

26、其中,所述迭代算法为单纯形法。

27、根据本公开的第二方面,提供了一种逐次逼近型模数转换器,所述逐次逼近型模数转换器包括:

28、第一数字信号获取模块,被设置为基于模数转换公式,对第一模拟信号进行模数转换,并获取所述模数转换后的第一数字信号;

29、模数转换模块,被设置为对输入的所述第一模拟信号进行模数转换,获取第二数字信号;

30、差值获取模块,被设置为获取所述第一数字信号和所述第二数字信号之间的差值信号;

31、校准模块,被设置为基于所述差值信号对所述电容阵列进行校准,以获取所述电容阵列中电容的校准后权重。

32、根据本公开的第三方面,提供了一种非临时性计算机可读存储介质,当所述存储介质中的指令由逐次逼近型模数转换器的处理器执行时,能够执行上述方法。

33、采用本公开的上述方法,具有以下有益效果:可以对sar adc电容阵列中的寄生电容进行校正,不需使用额外的校正电路和转换周期,从而避免了校准电路对sar adc自身性能的影响。并且,该校准方法对sar adc电路结构依赖程度低,适用于不同精度、不同电路结构的sar adc。

34、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!