全数字时钟占空比调节电路和时钟占空比调节方法与流程

本发明涉及时钟信号处理,尤其涉及一种全数字时钟占空比调节电路和时钟占空比调节方法。

背景技术:

1、时钟信号在传输过程中,其上升时间和下降时间会受信号通道特性的影响产生偏差,导致接收端的时钟信号占空比发生变化,使得接收端的时钟信号占空比不再是50%。其中,上升时间和下降时间的偏差对接收端时钟信号的占空比的影响如图1所示。传统的时钟占空比调节电路通常是由模拟电路定制而成,基本电路结构通常是将时钟信号通过一个rc网络(resistance-capacitance circuits,相移电路),和电源电压的一半作比较,从而判断出占空比是否发生变化,进而调整pmos管和nmos管的打开数量来调整时钟信号的占空比。

2、然而,目前的时钟占空比调节电路受限于mos管调节电流能力有限这一缺陷,使得时钟占空比调节电路的占空比调节范围小,电路的适用范围较窄。其次,现有时钟占空比调节电路的设计周期长,从设计到版图均需要手工搭电路,手工画布局图,并且电路的可移植性差,若需要将时钟占空比调节电路从一个工艺节点换到另一个工艺节点上,则上述电路设计和实现的所有流程需要从头重复一遍。

技术实现思路

1、本发明提供一种全数字时钟占空比调节电路和时钟占空比调节方法,用以解决现有技术中占空比调节范围小、设计周期长且可移植性差的缺陷。

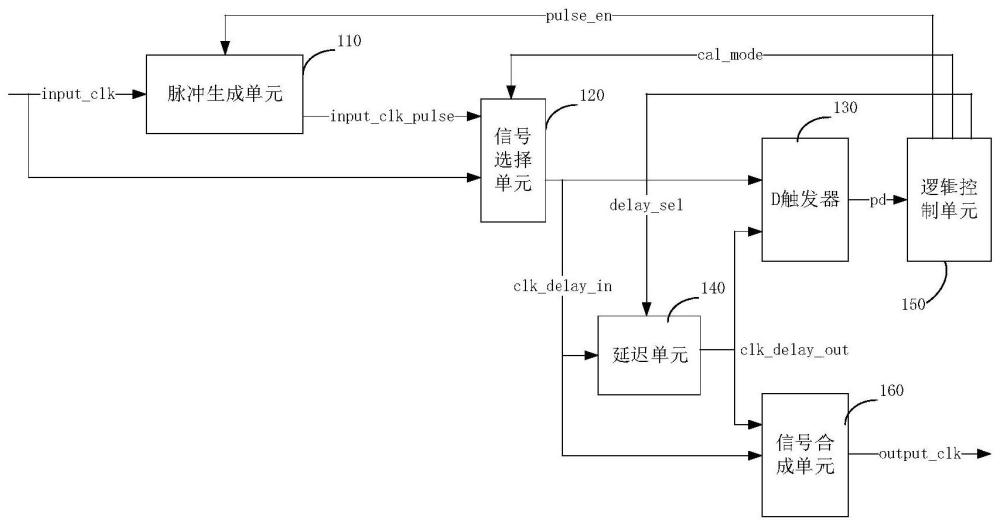

2、本发明提供一种全数字时钟占空比调节电路,包括:

3、脉冲生成单元、信号选择单元、d触发器、延迟单元、逻辑控制单元和信号合成单元;

4、其中,所述脉冲生成单元的输入端与输入时钟信号相连,所述脉冲生成单元的使能端与所述逻辑控制单元相连,以使得所述逻辑控制单元控制所述脉冲生成单元输出脉冲信号;

5、所述信号选择单元的输入端与所述脉冲信号和所述输入时钟信号相连,所述信号选择单元的使能端与所述逻辑控制单元相连,以使得所述逻辑控制单元控制所述信号选择单元选择所述脉冲信号或所述输入时钟信号;所述信号选择单元的输出端与所述d触发器的d端、所述延迟单元以及所述信号合成单元的输入端相连;

6、所述延迟单元的控制端与所述逻辑控制单元相连,以使得所述逻辑控制单元控制所述延迟单元的延迟程度;所述延迟单元的输出端与所述d触发器的时钟端以及所述信号合成单元的输入端相连;

7、所述d触发器的输出端与所述逻辑控制单元相连,以使得所述逻辑控制单元基于所述d触发器的输出信号控制所述脉冲生成单元、所述信号选择单元和所述延迟单元;

8、所述信号合成单元输出与所述输入时钟信号同周期且占空比为50%的输出时钟信号。

9、根据本发明提供的一种全数字时钟占空比调节电路,所述逻辑控制单元具体用于:

10、在校准模式下,控制所述脉冲生成单元输出脉冲信号,并控制所述信号选择单元选择所述脉冲信号;控制所述延迟单元以不同的延迟程度进行信号延迟,并基于所述d触发器的输出信号,确定所述延迟单元对应的当前延迟程度是否能将所述输入时钟信号延迟一个时钟周期;若确定所述延迟单元对应的当前延迟程度能将所述输入时钟信号延迟一个时钟周期,则切换至占空比调节模式;

11、在占空比调节模式下,关闭所述脉冲生成单元,并控制所述信号选择单元选择所述输入时钟信号;基于所述延迟单元对应的当前延迟程度,确定占空比调节延迟程度,并控制所述延迟单元基于所述占空比调节延迟程度对所述输入时钟信号进行延迟。

12、根据本发明提供的一种全数字时钟占空比调节电路,所述基于所述延迟单元对应的当前延迟程度,确定占空比调节延迟程度,具体包括:

13、确定所述延迟单元对应的当前延迟程度的1/2为目标延迟程度;

14、基于所述延迟单元的延迟精度以及所述目标延迟程度,确定所述占空比调节延迟程度。

15、根据本发明提供的一种全数字时钟占空比调节电路,所述控制所述延迟单元以不同的延迟程度进行信号延迟,并基于所述d触发器的输出信号,确定所述延迟单元对应的当前延迟程度是否能将所述输入时钟信号延迟一个时钟周期,具体包括:

16、按照延迟程度由小到大的顺序控制所述延迟单元以不同的延迟程度进行信号延迟;

17、若检测到所述d触发器的输出信号出现由高电平至低电平的跳变,则确定所述延迟单元对应的当前延迟程度能将所述输入时钟信号延迟一个时钟周期。

18、根据本发明提供的一种全数字时钟占空比调节电路,所述信号合成单元包括异或门和二分频单元。

19、本发明还提供一种基于如上述任一种全数字时钟占空比调节电路的时钟占空比调节方法,包括:

20、开启逻辑控制单元的校准模式后,基于所述逻辑控制单元控制脉冲生成单元基于输入时钟信号输出相应的脉冲信号,并控制信号选择单元选择并输出所述脉冲信号;基于所述逻辑控制单元控制延迟单元以不同的延迟程度对所述脉冲信号进行信号延迟得到延迟脉冲信号,并基于d触发器基于时钟端输入的所述延迟脉冲信号对d端输入的所述脉冲信号进行采样,得到所述d触发器输出的输出信号,直至所述逻辑控制单元根据所述d触发器输出的输出信号确定所述延迟单元对应的当前延迟程度能将所述输入时钟信号延迟一个时钟周期,并将所述逻辑控制单元切换至占空比调节模式;

21、在占空比调节模式下,基于所述逻辑控制单元关闭所述脉冲生成单元,并控制所述信号选择单元选择并输出输入时钟信号;基于所述逻辑控制单元,根据所述延迟单元对应的当前延迟程度,确定占空比调节延迟程度,并控制所述延迟单元基于所述占空比调节延迟程度对所述输入时钟信号进行延迟,得到所述延迟单元输出的延迟时钟信号;基于所述信号合成单元对所述输入时钟信号和所述延迟时钟信号进行信号合成,得到与所述输入时钟信号同周期且占空比为50%的输出时钟信号。

22、根据本发明提供的一种时钟占空比调节方法,所述根据所述延迟单元对应的当前延迟程度,确定占空比调节延迟程度,具体包括:

23、确定所述延迟单元对应的当前延迟程度的1/2为目标延迟程度;

24、基于所述延迟单元的延迟精度以及所述目标延迟程度,确定所述占空比调节延迟程度。

25、根据本发明提供的一种时钟占空比调节方法,所述基于所述逻辑控制单元控制延迟单元以不同的延迟程度对所述脉冲信号进行信号延迟得到延迟脉冲信号,并基于d触发器基于时钟端输入的所述延迟脉冲信号对d端输入的所述脉冲信号进行采样,得到所述d触发器输出的输出信号,直至所述逻辑控制单元根据所述d触发器输出的输出信号确定所述延迟单元对应的当前延迟程度能将所述输入时钟信号延迟一个时钟周期,并将所述逻辑控制单元切换至占空比调节模式,具体包括:

26、基于所述逻辑控制单元按照延迟程度由小到大的顺序控制所述延迟单元以不同的延迟程度对所述脉冲信号进行信号延迟得到延迟脉冲信号,并基于d触发器基于时钟端输入的所述延迟脉冲信号对d端输入的所述脉冲信号进行采样,得到所述d触发器输出的输出信号;

27、若检测到所述d触发器的输出信号出现由高电平至低电平的跳变,则确定所述延迟单元对应的当前延迟程度能将所述输入时钟信号延迟一个时钟周期,并将所述逻辑控制单元切换至占空比调节模式。

28、根据本发明提供的一种时钟占空比调节方法,所述基于所述信号合成单元对所述输入时钟信号和所述延迟时钟信号进行信号合成,得到与所述输入时钟信号同周期且占空比为50%的输出时钟信号,具体包括:

29、基于所述信号合成单元中的异或门对所述输入时钟信号和所述延迟时钟信号进行异或操作,得到初始合成信号;

30、基于所述信号合成单元中的二分频单元对所述初始合成信号进行二分频处理,得到所述与所述输入时钟信号同周期且占空比为50%的输出时钟信号。

31、本发明提供的全数字时钟占空比调节电路和时钟占空比调节方法,通过逻辑控制单元的校准模式,控制脉冲生成单元基于输入时钟信号输出相应的脉冲信号,并控制信号选择单元选择并输出脉冲信号,控制延迟单元以不同的延迟程度对脉冲信号进行信号延迟得到延迟脉冲信号,并基于d触发器基于时钟端输入的延迟脉冲信号对d端输入的脉冲信号进行采样,得到d触发器输出的输出信号,直至逻辑控制单元根据d触发器输出的输出信号确定延迟单元对应的当前延迟程度能将输入时钟信号延迟一个时钟周期,并将逻辑控制单元切换至占空比调节模式,从而通过逻辑控制单元的占空比调节模式,关闭脉冲生成单元,并控制信号选择单元选择并输出输入时钟信号,根据延迟单元对应的当前延迟程度,确定占空比调节延迟程度,并控制延迟单元基于占空比调节延迟程度对输入时钟信号进行延迟,得到延迟单元输出的延迟时钟信号,随后基于信号合成单元对输入时钟信号和延迟时钟信号进行信号合成,得到与输入时钟信号同周期且占空比为50%的输出时钟信号,其占空比调节范围大,当延迟单元的延迟精度足够小时,可以调节任意占空比的输入时钟信号,同时,该电路由于是全数字实现,可以通过verilog代码实现,设置好约束,采用eda工具综合并完成布局布线即可,设计周期间短,且即使需要转换工艺,可以利用原始的verilog代码和设计约束,采用eda工具映射到新的工艺库即可,大大缩短了工艺转换时电路调整的时间。

- 还没有人留言评论。精彩留言会获得点赞!