一种I2C接口电路的输出电路及I2C接口电路的制作方法

本发明涉及集成电路,尤其涉及一种i2c接口电路的输出电路及i2c接口电路。

背景技术:

1、现有技术中,一个单通道双向传输的i2c接口电路由两个反向传输的数字隔离通道组成,每一数字隔离通道具有一输入电路、隔离器及输出电路,数字隔离通道共用一隔离器。

2、具体如图1所示,当信号传输方向由side1到side2时,side1侧的输入模块1工作,数据端sda1的电压与低电平阈值vref1进行比较,数据端sda1的电压的幅值高于低电平阈值vref1时被识别为高电平,低于低电平阈值vref1时被识别为低电平。由隔离器ib对输入模块1输出的信号进行编解码,具体的,隔离器ib包括编码器、隔离电路及解码器,编码器及解码器分别设置于side1侧及side2侧。当输入模块1输出低电平时,经过输出模块1中反向器输出高电平,nmos管m0导通,当输入模块1输出高电平时,经过输出模块1中反向器输出低电平,nmos管m0关断。

3、当通道方向由side2到side1时,side1侧的输出模块2工作,当rx_out信号为低电平时,nmos管m1关断,数据端sda1被上拉电阻rup1拉为高电平;当rx_out信号为高电平,nmos管m1导通,由于二极管d1的抬压作用,a点电压值等于低电平阈值vref2(vref2>vref1),即数据端sda1的电压为vref2。

4、现有技术中当side2侧数据端sda2的电压为低电平时,nmos管m1输入的rx_out信号为高电平,side1侧的输出模块2的输出电平幅值为vref2。vref2大于side1侧的输入模块的低电平阈值vref1,从而避免电平闩锁的问题。

5、但是在实际应用中,i2c总线隔离电路与其他多个设备共同挂接在i2c总线上,当输出模块输出低电平信号时,其他设备将i2c总线拉低然后释放时会导致图1中数据端sda1电压出现过冲,仿真波形如图2所示,该过冲电压为1.36v,远超输出模块的高电平阈值,导致原本的低电平输出信号被误识别为高电平,从而影响i2c总线隔离电路的可靠性。

技术实现思路

1、本发明用于解决现有技术中i2c总线上其它设备拉低释放时,i2c总线会产生过冲现象,i2c接口电路的输出电路输出的低电平会被误认为高电平,从而使得i2c接口电路存在可靠性差的问题。

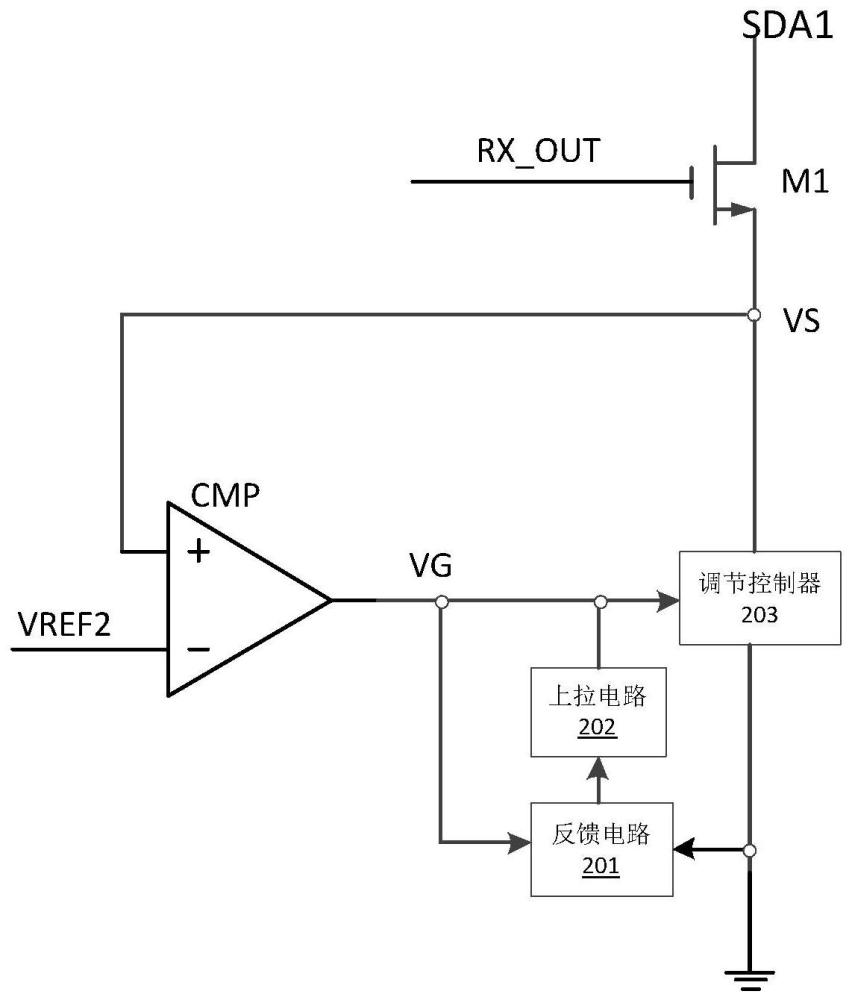

2、为了解决上述技术问题,本发明一方面提供一种i2c接口电路的输出电路,所述输出电路包括:第一nmos管、电压感知模块及电压调节模块;

3、所述第一nmos管的栅极连接i2c接口电路中隔离器的输出端,所述第一nmos管的漏极连接i2c数据端,所述第一nmos管的源极、所述电压调节模块的调节端及所述电压感知模块的输入端分别连接至中间节点;

4、所述电压感知模块的输出端连接所述电压调节模块的控制端,用于感知所述中间节点的电压变化,根据中间节点的电压变化控制所述电压调节模块的开启及关闭;

5、所述第一nmos管导通时中间节点电压为低电平阈值,所述电压调节模块开启时用于调节所述中间节点的电压值至低电平阈值。

6、作为本发明进一步实施例中,所述电压感知模块包括:比较器,所述比较器的正输入端连接所述中间节点,所述比较器的负输入端接入低电平阈值,所述比较器的输出端连接所述电压调节模块的控制端;

7、当所述中间节点的电压大于低电平阈值时,开启所述电压调节模块;

8、当所述中间节点的电压小于或等于低电平阈值时,关闭所述电压调节模块。

9、作为本发明进一步实施例中,所述电压调节模块包括:反馈模块、上拉模块及调节控制器,其中,所述调节控制器具有控制端、第一调节端及第二调节端;

10、所述上拉模块的输出端连接所述调节控制器的控制端,用于根据反馈模块输出的反馈电压开启或关闭所述调节控制器,进而调节所述中间节点的电压值至低电平阈值;

11、所述反馈模块的输入端连接所述比较器的输出端及调节控制器的第一调节端,所述反馈模块的输出端连接所述上拉模块的输入端,用于采集所述比较器的输出端及第一调节端之间的电压;

12、所述调节控制器的第一调节点连接接地端,所述调节控制器的第二调节点连接所述中间节点,所述调节控制器的控制端连接所述比较器的输出端;

13、所述比较器、上拉模块均可开启或关闭所述调节控制器。

14、作为本发明进一步实施例中,所述调节控制器至少包括:第二nmos管,所述第一调节端、第二调节端及控制端分别为第二nmos管的源极、漏极及栅极。

15、作为本发明进一步实施例中,所述反馈模块包括:第三nmos管及偏置单元;

16、所述第三nmos管的栅极连接所述第二nmos管的栅极,所述第三nmos管的源极连接所述第二nmos管的源极,所述第三nmos管的漏极连接所述上拉模块的输入端及所述偏置单元;

17、所述偏置单元用于为所述第三nmos管提供偏置电流。

18、作为本发明进一步实施例中,所述偏置单元至少包括:第一pmos管;

19、所述第一pmos管的栅极接入偏置电压,所述第一pmos管的源极连接电源,所述第一pmos管的漏极连接所述第三nmos管的漏极。

20、作为本发明进一步实施例中,所述上拉模块包括:第二pmos管及上拉电阻;

21、所述第二pmos管的栅极连接所述第三nmos管的漏极,所述第二pmos管的漏极连接所述第二nmos管的栅极,所述第二pmos管的源极连接所述上拉电阻的一端;

22、所述上拉电阻的另一端连接电源。

23、作为本发明进一步实施例中,还包括:稳压电容,连接在所述第三nmos的漏极及接地端之间。

24、本发明第二方面提供一种单向传输的i2c接口电路,包括:输入电路、前述任一实施例所述的输出电路、连接在所述输入电路及输出电路之间的隔离器。

25、本发明第三方面提供一种双向传输的i2c接口电路,包括:两个反向传输的数字隔离通道,其中一数字隔离通道包括:前述实施例所述的单向传输的i2c接口电路。

26、本发明提供的i2c接口电路的输出电路,通过在第一nmos管的源极端设置电压感知模块,使得在第一nmos管导通时,能够自动识别i2c总线上其它设备拉低释放时产生的电压波动。通过在第一nmos管的源极端与电压感知模块之间设计电压调节模块,能够快速调整第一nmos管源极侧的电压恢复至低电平阈值,不会出现第一nmos管低电平输出被误认为高电平的情况,从而能够提升i2c接口电路的可靠性。

27、为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附图式,作详细说明如下。

技术特征:

1.一种i2c接口电路的输出电路,其特征在于,所述输出电路包括:第一nmos管、电压感知模块及电压调节模块;

2.如权利要求1所述的输出电路,其特征在于,所述电压感知模块包括:比较器,所述比较器的正输入端连接所述中间节点,所述比较器的负输入端接入低电平阈值,所述比较器的输出端连接所述电压调节模块的控制端;

3.如权利要求2所述的输出电路,其特征在于,所述电压调节模块包括:反馈模块、上拉模块及调节控制器,其中,所述调节控制器具有控制端、第一调节端及第二调节端;

4.如权利要求3所述的输出电路,其特征在于,所述调节控制器至少包括:第二nmos管,所述第一调节端、第二调节端及控制端分别为第二nmos管的源极、漏极及栅极。

5.如权利要求4所述的输出电路,其特征在于,所述反馈模块包括:第三nmos管及偏置单元;

6.如权利要求5所述的输出电路,其特征在于,所述偏置单元至少包括:第一pmos管;

7.如权利要求5所述的输出电路,其特征在于,所述上拉模块包括:第二pmos管及上拉电阻;

8.如权利要求5所述的输出电路,其特征在于,还包括:稳压电容,连接在所述第三nmos管的漏极及接地端之间。

9.一种单向传输的i2c接口电路,其特征在于,包括:输入电路、权利要求1至8任意一项所述的输出电路、连接在所述输入电路及输出电路之间的隔离器。

10.一种双向传输的i2c接口电路,其特征在于,包括:两个反向传输的数字隔离通道,其中一数字隔离通道包括:权利要求9所述的单向传输的i2c接口电路。

技术总结

本发明涉及集成电路技术领域,提供了一种I2C接口电路的输出电路及I2C接口电路,输出电路包括:第一NMOS管的栅极连接I2C接口电路中隔离器的输出端,第一NMOS管的漏极连接I2C数据端,第一NMOS管的源极、电压调节模块的调节端及电压感知模块的输入端分别连接至中间节点;电压感知模块的输出端连接电压调节模块的控制端,用于感知中间节点的电压变化,根据中间节点的电压变化控制电压调节模块的开启及关闭;第一NMOS管导通时中间节点电压为低电平阈值,电压调节模块开启时用于调节中间节点的电压值至低电平阈值。本文能够避免I2C总线其它设备对总线操作引起的输出信号不准确的问题,提升I2C接口电路的可靠性。

技术研发人员:迟明

受保护的技术使用者:北京中科格励微科技有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!